伪静态随机存取存储器及其读取方法与流程

- 国知局

- 2024-07-31 19:15:46

本发明涉及一种存储器的读取方法,且尤其涉及一种伪静态随机存取存储器及其读取方法。

背景技术:

1、近年来在半导体存储器的发展中,因应高速存取与微型化的需求,对于同时具有静态随机存取存储器及动态随机存取存储器(dynamic random access memory,dram)的优点的伪静态随机存取存储器(pseudo static random access memory,psram)的需求持续增加,特别是运用在移动装置中。

2、在传统的psram中,为了减少外部接脚的数量,通过芯片使能信号(ce#)接脚、芯片时钟信号(clk)接脚与数据输入输出接脚adq来控制数据的读出。芯片使能接脚被配置以提供芯片使能信号ce#,以使能或禁能psram。当psram被使能时,可通过数据输入输出接脚adq来接收命令及地址,且psram中的输入接受器被使能以根据所接收的命令及地址开始对存储单元进行存取,并且在读取延迟后通过数据输入输出接脚adq来输出数据。此外,读取操作是响应于芯片使能信号ce#的上升缘而结束,亦即psram停止输出数据与停止产生列选择信号csl的列选择脉冲,且字线信号wl在列选择信号csl的最后一个脉冲下降之后被关闭(例如变为低电位)。当psram被禁能时(即处于待命状态),输入接受器亦被禁能以节省能耗。然而,基于上述的控制方法将产生固定长度(即n个列选择脉冲)的列选择信号csl,且上述固定长度大于数据输入输出接脚adq输出数据所需的时间长度,使得在数据输入输出接脚adq输出数据的期间维持列选择脉冲的输出。换句话说,列选择信号csl具有多余的脉冲,从而造成不必要的能耗。并且,由于下一个操作(例如刷新操作或存取操作)需在字线信号wl被关闭后才能被执行,因此上述的控制方法亦存在操作时间长的问题。

3、在psram使用双倍数据率同步动态随机存取存储器(double data ratesynchronous dynamic random access memory,ddr sdram)的单元结构的情况下,当进行读取操作时,可根据一个列选择信号csl的周期(cycle)来读取两笔数据。然而,上述问题在此情况会变得更严重。

技术实现思路

1、本发明提供一种伪静态随机存取存储器及其读取方法,可根据读取数据的数量来动态调整列选择信号csl的长度。

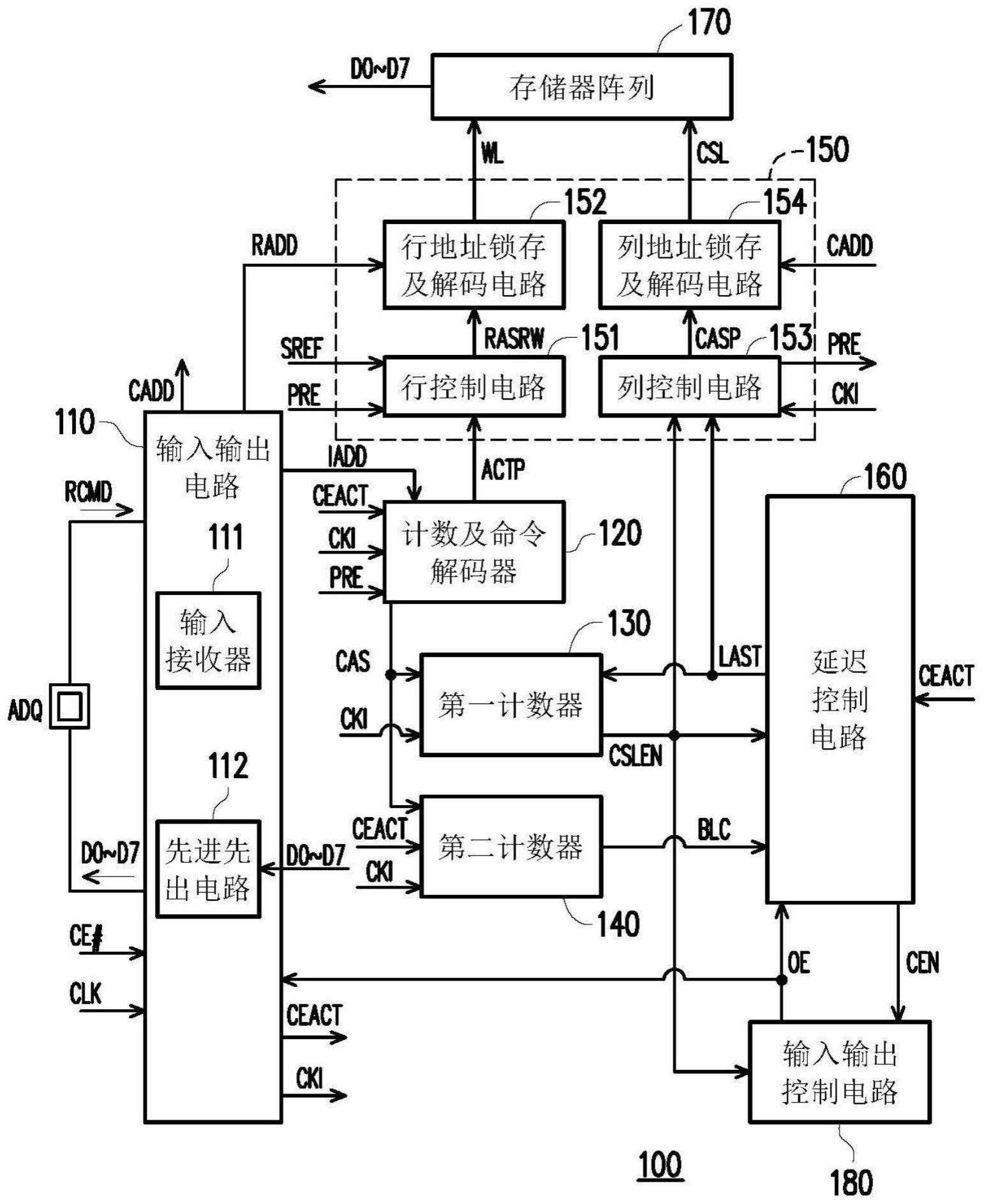

2、本发明的伪静态随机存取存储器包括存储器阵列、输入输出电路、计数及命令解码器、突发长度计数器、行与列控制电路、延迟控制电路及输入输出控制电路。输入输出电路接收来自数据输入输出接脚的读取命令序列,并根据读取命令序列产生读取命令、读取行地址及读取列地址。计数及命令解码器接收内部使能信号、时钟信号及读取命令,对读取命令进行解码,并且在自内部使能信号从禁能状态变为使能状态时开始对时钟信号进行计数,当计数到达第一时钟量时输出第一电平的列地址选通信号。突发长度计数器接收时钟信号、内部使能信号及列地址选通信号。在列地址选通信号从第二电平变为第一电平至内部使能信号从使能状态变为禁能状态为止的期间,突发长度计数器对时钟信号进行计数,据以提供突发长度。行与列控制电路接收时钟信号、列选择使能信号及读取列地址。当列选择使能信号从第二电平变为第一电平后,行与列控制电路反应于时钟信号而根据读取列地址输出列选择信号至存储器阵列。延迟控制电路接收列选择使能信号及突发长度。在自列选择使能信号从第二电平变为第一电平起延迟突发长度后,延迟控制电路输出第一电平的第一确认信号至行与列控制电路,使列选择信号的长度等于突发长度。

3、本发明的伪静态随机存取存储器的读取方法包括下列步骤:接收来自数据输入输出接脚的读取命令序列,并根据读取命令序列产生读取命令、读取行地址、读取列地址;对读取命令进行解码,并且在自内部使能信号从禁能状态变为使能状态时开始对时钟信号进行计数,当计数到达第一时钟量时输出第一电平的列地址选通信号;在列地址选通信号从第二电平变为第一电平至内部使能信号从使能状态变为禁能状态为止的期间对时钟信号进行计数,据以提供突发长度;以及在自列选择使能信号从第二电平变为第一电平起延迟突发长度后输出第一电平的第一确认信号至行与列控制电路,使列选择信号的长度等于突发长度。

4、基于上述,每当进行读取操作时,本发明的伪静态随机存取存储器可计算出适合于读取数据数量的突发长度,并且让列选择信号的长度等于突发长度。由此,可避免产生不必要的列选择信号,减少电流消耗,并且加快读取操作的处理速度。

技术特征:1.一种伪静态随机存取存储器,其特征在于,包括:

2.根据权利要求1所述的伪静态随机存取存储器,其特征在于,还包括:

3.根据权利要求2所述的伪静态随机存取存储器,其特征在于,所述行与列控制电路包括:

4.根据权利要求3所述的伪静态随机存取存储器,其特征在于,当所述计数及命令解码器所进行的计数到达第二时钟量时,所述计数及命令解码器输出所述就绪脉冲至所述行控制电路。

5.根据权利要求3所述的伪静态随机存取存储器,其特征在于,所述行与列控制电路还包括:

6.根据权利要求5所述的伪静态随机存取存储器,其特征在于,当所述第一确认信号从所述第二电平变为所述第一电平时,所述第一计数器输出所述第二电平的所述列选择使能信号。

7.根据权利要求5所述的伪静态随机存取存储器,其特征在于,当所述第一确认信号从所述第二电平变为所述第一电平时,所述列控制电路停止输出所述列选择脉冲序列,致使所述列地址锁存及解码电路停止输出所述列选择信号,并且所述列控制电路输出控制脉冲至所述计数及命令解码器及所述行控制电路,以使所述计数及命令解码器及所述行控制电路分别输出所述第二电平的所述列地址选通信号及所述第二电平的所述行地址选通信号。

8.根据权利要求1所述的伪静态随机存取存储器,其特征在于,还包括:

9.根据权利要求8所述的伪静态随机存取存储器,其特征在于,在自所述输出使能信号从所述第二电平变为所述第一电平起延迟所述突发长度后,所述延迟控制电路输出所述第二电平的芯片禁能信号至所述输入输出控制电路,

10.根据权利要求1所述的伪静态随机存取存储器,其特征在于,所述延迟控制电路包括:

11.根据权利要求10所述的伪静态随机存取存储器,其特征在于,所述确认信号控制电路包括:

12.一种读取方法,适用于伪静态随机存取存储器,其特征在于,包括:

13.根据权利要求12所述的读取方法,其特征在于,还包括:

14.根据权利要求13所述的读取方法,其特征在于,还包括:

15.根据权利要求14所述的读取方法,其特征在于,当所述列选择使能信号从所述第二电平变为所述第一电平后反应于所述时钟信号而根据所述读取列地址输出所述列选择信号至所述存储器阵列的步骤包括:

16.根据权利要求15所述的读取方法,其特征在于,还包括:

17.根据权利要求15所述的读取方法,其特征在于,还包括:

18.根据权利要求12所述的读取方法,其特征在于,还包括:

19.根据权利要求12所述的读取方法,其特征在于,输出所述第一电平的所述第一确认信号的步骤包括:

20.根据权利要求19所述的读取方法,其特征在于,根据所述列选择使能信号、所述时钟信号、所述突发长度、所述芯片禁能信号以及所述重置信号,以产生所述第一确认信号的步骤包括:

技术总结本发明提供一种伪静态随机存取存储器及其读取方法。计数及命令解码器在自内部使能信号从禁能状态变为使能状态时开始对时钟信号进行计数,当计数到达第一时钟量时输出第一电平的列地址选通信号。在列地址选通信号从第二电平变为第一电平至内部使能信号从使能状态变为禁能状态为止的期间,突发长度计数器对时钟信号进行计数,据以提供突发长度。延迟控制电路输出第一电平的第一确认信号至行与列控制电路,使列选择信号的长度等于突发长度。技术研发人员:佐佐木纯一,森郁受保护的技术使用者:华邦电子股份有限公司技术研发日:技术公布日:2024/1/16本文地址:https://www.jishuxx.com/zhuanli/20240731/182070.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。