存储器测试电路及方法与流程

- 国知局

- 2024-07-31 19:15:54

本公开涉及半导体,尤其涉及一种存储器测试电路及方法。

背景技术:

1、动态随机存储器(dynamic random access memory,dram)在生产后,需要进行一系列测试。但是,在进行晶圆测试(circuit probing,简称cp测试)的过程中,难以寻找出状态异常的存储单元。

技术实现思路

1、以下是对本公开详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开提供一种存储器测试电路及方法。

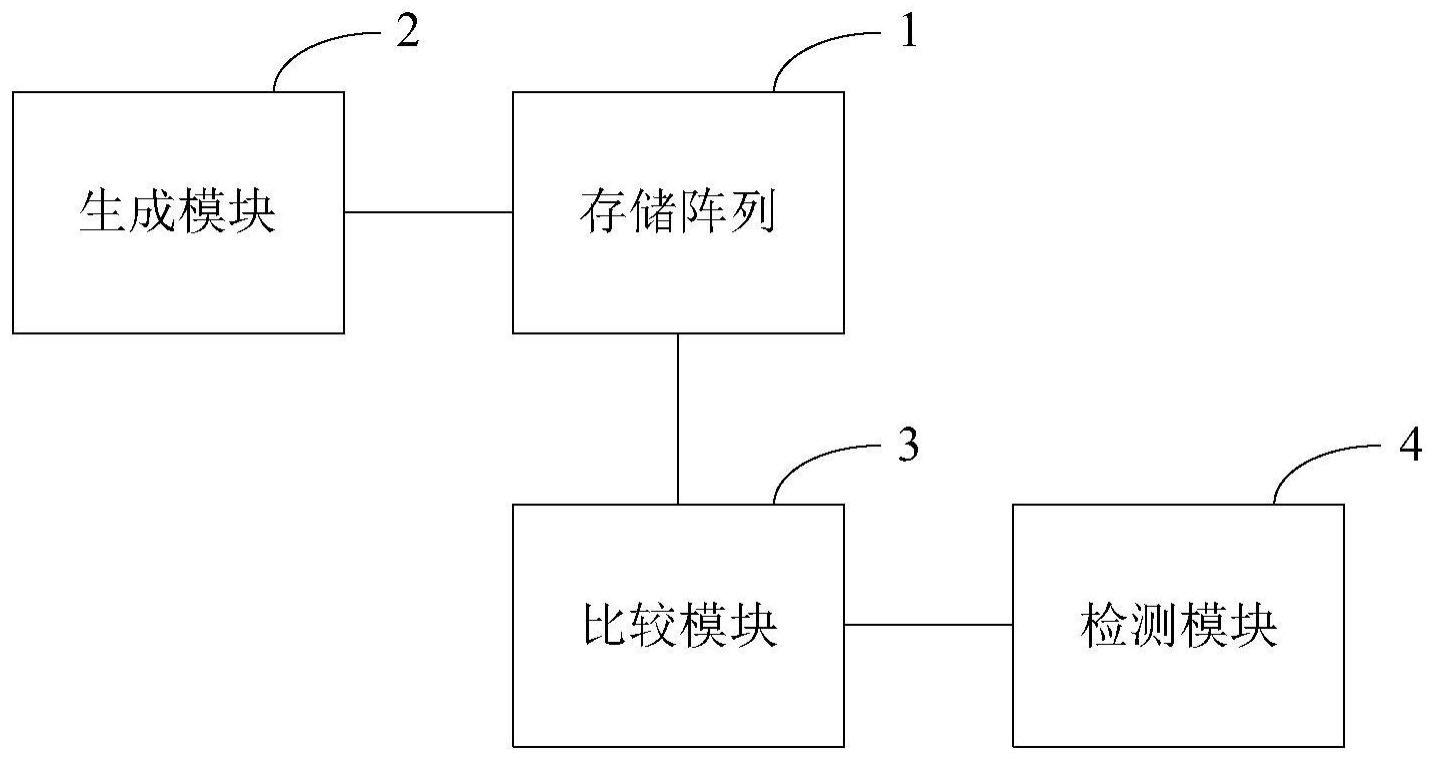

3、根据本公开实施例的第一方面,提供一种存储器测试电路,所述存储器测试电路包括:

4、存储阵列,所述存储阵列包含多个存储单元组,各所述存储单元组均包括数量相同的多个存储单元;

5、生成模块,所述生成模块与所述存储阵列耦接,所述生成模块用于生成随机的测试数据,相同的所述测试数据用于写入不同的所述存储单元组的各所述存储单元中;

6、比较模块,所述比较模块与所述存储阵列耦接,所述比较模块被配置为根据读取的各所述存储单元组的目标数据,生成比较信息;

7、检测模块,所述检测模块与所述比较模块耦接,所述检测模块用于根据所述比较信息生成检测信息,所述检测信息用于表征所述存储单元组中是否存在异常的存储单元。

8、根据本公开的一些实施例,所述生成模块包括:

9、线性反馈移位寄存器,所述线性反馈移位寄存器具有时钟信号输入端和多个数据输出端,所述线性反馈移位寄存器被配置为当所述时钟信号输入端接收到触发信号时,通过所述多个数据输出端输出随机的所述测试数据;

10、其中,所述触发信号为操作指令中的写入指令或读取指令。

11、根据本公开的一些实施例,所述比较模块包括:

12、比较逻辑门组,所述比较逻辑门组包括多个比较逻辑门,每个所述比较逻辑门的第一输入端均耦接一个所述存储单元,每个所述比较逻辑门的第二输入端均与所述生成模块耦接,每个所述比较逻辑门的输出端与所述检测模块耦接以将所述比较信息输出至所述检测模块。

13、根据本公开的一些实施例,所述检测模块包括:

14、多个晶体管组,每个所述晶体管组与一个所述存储单元组对应;每个所述晶体管组均包括多个晶体管,各所述晶体管的第一端均耦接,每个所述晶体管的控制端分别耦接一个所述比较逻辑门的输出端,同一所述晶体管组中各所述晶体管的第二端均耦接构成所述检测模块的信号输出端。

15、根据本公开的一些实施例,所述存储器测试电路还包括:

16、存储模块,所述存储模块存储有至少一个固定的测试数据;

17、选择模块,所述选择模块与所述生成模块、所述存储模块以及所述存储阵列均耦接,所述选择模块用于控制所述多个存储单元组与所述生成模块和所述存储模块择一导通。

18、本公开的第二方面提供一种存储器测试方法,所述存储器包括多个存储单元组,各所述存储单元组均包括数量相同的多个存储单元,所述存储器测试方法包括:

19、生成随机的测试数据;

20、将所述测试数据写入各所述存储单元组;

21、读取各所述存储单元组的目标数据;

22、根据所述目标数据,生成比较信息;

23、根据所述比较信息,生成检测信息,所述检测信息用于表征所述存储单元组中是否存在异常的存储单元。

24、根据本公开的一些实施例,所述测试数据由生成模块生成,所述生成模块包括时钟信号输入端和多个数据输出端;所述生成随机的测试数据,包括:

25、向所述时钟信号输入端发送触发信号,以在每个数据输出端生成随机的数据位;

26、将所述数据位构成的数据作为所述测试数据;

27、其中,所述触发信号为操作指令中的写入指令或读取指令。

28、根据本公开的一些实施例,所述测试数据包括第一测试数据和第二测试数据,所述第一测试数据是所述生成模块在接收到所述写入指令的情况下生成,所述第二测试数据是所述生成模块在接收到所述读取指令的情况下生成,所述第一测试数据与所述第二测试数据相同。

29、根据本公开的一些实施例,所述根据所述比较信息,生成检测信息,包括:

30、将多个所述比较信息分别输入至多个晶体管的控制端;

31、获取每个所述晶体管的状态信息;

32、根据所述状态信息,生成所述检测信息。

33、根据本公开的一些实施例,所述存储器测试方法在一个测试周期内执行多次,每次通过线性反馈移位寄存器生成的所述测试数据均不相同。

34、本公开实施例所提供的存储器测试电路及方法中,存储器测试电路包括生成模块、比较模块和检测模块。在进行存储器测试的过程中,生成模块能够生成随机的测试数据,避免了测试数据固定导致异常的存储单元遗漏。相同的测试数据用于一次写入多个不同的存储单元组的各存储单元中,从而提高了测试数据写入的效率。比较模块能够根据读取的目标数据,生成比较信息,确定目标数据中是否存在异常数据。检测模块能够根据比较模块生成的比较信息生成检测信息,以根据检测信息确定存储单元组中是否存在异常的存储单元。由于每个存储单元组中的存储单元的数量相同,避免了比较信息生成过程中因比较错位导致的错误,提高了存储单元状态确定的可靠性。通过生成模块生成的随机的测试数据对存储单元进行检测,能够提高测试的覆盖面,从而易于检测出状态异常的存储单元。

35、在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:1.一种存储器测试电路,其特征在于,所述存储器测试电路包括:

2.根据权利要求1所述的存储器测试电路,其特征在于,所述生成模块包括:

3.根据权利要求1所述的存储器测试电路,其特征在于,所述比较模块包括:

4.根据权利要求3所述的存储器测试电路,其特征在于,所述检测模块包括:

5.根据权利要求1至4任一项所述的存储器测试电路,其特征在于,所述存储器测试电路还包括:

6.一种存储器测试方法,其特征在于,所述存储器包括多个存储单元组,各所述存储单元组均包括数量相同的多个存储单元,所述存储器测试方法包括:

7.根据权利要求6所述的存储器测试方法,其特征在于,所述测试数据由生成模块生成,所述生成模块包括时钟信号输入端和多个数据输出端;所述生成随机的测试数据,包括:

8.根据权利要求7所述的存储器测试方法,其特征在于,所述测试数据包括第一测试数据和第二测试数据,所述第一测试数据是所述生成模块在接收到所述写入指令的情况下生成,所述第二测试数据是所述生成模块在接收到所述读取指令的情况下生成,所述第一测试数据与所述第二测试数据相同。

9.根据权利要求6所述的存储器测试方法,其特征在于,所述根据所述比较信息,生成检测信息,包括:

10.根据权利要求6至9任一项所述的存储器测试方法,其特征在于,所述存储器测试方法在一个测试周期内执行多次,每次通过线性反馈移位寄存器生成的所述测试数据均不相同。

技术总结本公开提供一种存储器测试电路及方法。存储器测试电路包括:存储阵列,存储阵列包含多个存储单元组,各存储单元组均包括数量相同的多个存储单元;生成模块,与存储阵列耦接,用于生成随机的测试数据,相同的测试数据用于写入不同的存储单元组的各存储单元中;比较模块,与存储阵列耦接,被配置为根据读取的各存储单元组的目标数据,生成比较信息;检测模块,与比较模块耦接,用于根据比较信息生成检测信息,检测信息用于表征存储单元组中是否存在异常的存储单元。通过以随机的测试数据对存储单元进行检测,能够提高测试的覆盖面,从而易于检测出状态异常的存储单元。技术研发人员:陆天辰受保护的技术使用者:长鑫存储技术有限公司技术研发日:技术公布日:2024/1/16本文地址:https://www.jishuxx.com/zhuanli/20240731/182075.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。