存储控制电路、存储器、存储器的修复方法及电子设备与流程

- 国知局

- 2024-07-31 19:36:24

本技术涉及存储,尤其涉及一种存储控制电路、存储器、存储器的修复方法及电子设备。

背景技术:

1、现有很多电子产品采用动态随机存取存储器(dynamic random access memory,dram)作为系统内存,用于暂存中央处理器(central processing unit,cpu)的运算数据,以及与硬盘等外部存储器交换的数据。

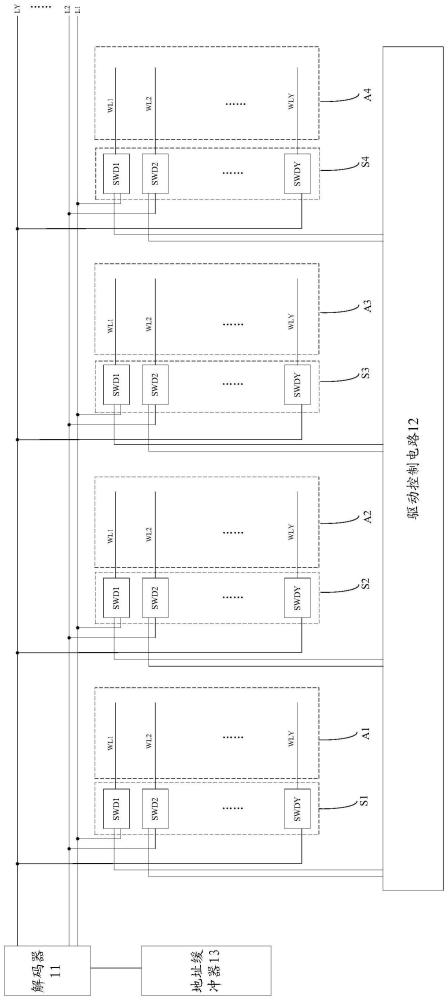

2、如图1所示,dram的存储空间一般包括多个库(bank),例如图1中的bank1~bank4,如图2所示,每个bank为二维的存储阵列,存储阵列沿字线方向被分为多个存储区域a1~ax,每一存储区域ax(x为1至x的任一整数)中均有多行存储单元行wl1~wln,每一行存储单元行wln(n为1至n的任一整数)连接一条字线和一个驱动电路swdn,所有的驱动电路swdn均与解码器连接。在进行数据写入或读取操作时,解码器一次仅能选中存储阵列中的一整行存储单元行,并向与该一整行存储单元行对应的多个驱动电路swdn同时发送控制信号,以驱动该一整行存储单元行。即现有的dram,只能以一整行存储单元行为单位进行驱动,对不同存储单元行的进行灵活的控制受到限制。

技术实现思路

1、本技术提供一种存储控制电路、存储器、存储器的修复方法及电子设备,用于提高存储器的控制灵活性。

2、第一方面,本技术实施例提供的一种存储控制电路,该存储控制电路应用于存储器,用于对存储器中的存储阵列进行控制。示例性的,存储控制电路包括解码器,多个字线驱动电路和驱动控制电路。存储阵列中包括沿字线方向(也即存储单元行的延伸方向)排列的多个存储区域。每一个存储区域中均包括多行存储单元行。每一存储单元行连接一条字线。相当于将存储阵列中的每一行存储单元整行分成多份,每一份为一个存储区域中的一个存储单元行。即存储阵列的每一行存储单元整行均包括多个存储区域中的每一存储区域中的一个存储单元行。在本技术中,存储区域中每一行存储单元行对应连接一条字线,以通过字线向存储单元行传输驱动信号。当存储单元行接收到驱动信号时,该存储单元行被激活,即该存储单元行中的各存储单元被导通,然后通过位线(一般一个存储单元行中,每一存储单元均会连接一条位线,不同的存储单元连接不同的位线)就可以向该存储单元行中的各存储单元写入数据或者读取数据。每一个存储区域对应配置有一个字线驱动电路,每一个字线驱动电路中均包括多个驱动子电路,多个驱动子电路中每一驱动子电路连接对应的存储区域中的一行存储单元行,用于向该存储单元行发送驱动信号。解码器与多个字线驱动电路中每一字线驱动电路中的多个驱动子电路连接,即每一字线驱动电路中的每一个驱动子电路均与解码器连接。示例性的,解码器用于向多个字线驱动电路中每一字线驱动电路中被选中的其中一个驱动子电路同时发送第一控制信号,以控制被选中的各驱动子电路同时向对应的存储单元行发送驱动信。驱动控制电路与多个字线驱动电路中每一字线驱动电路中至少部分驱动子电路连接;驱动控制电路可以独立的向与其连接的任意驱动子电路发送第一控制信号,从而使接收到该第一控制信号的驱动子电路可以向与该驱动子电路连接的存储单元行发送驱动信号。本技术对驱动控制电路连接的驱动子电路的位置和数量均不作限定,例如,与驱动控制电路连接的属于不同字线驱动电路中的驱动子电路的数量可以相同,也可以不相同,与驱动控制电路连接的属于不同字线驱动电路中的驱动子电路的位置可以相同,也可以不相同,具体可以根据实际需求进行设计,在此不作限定。

3、可以理解的是,本技术中,解码器和驱动控制电路均可以向与其连接的驱动子电路发送第一控制信号,而驱动子电路在接收到该第一控制信号时可以向与该驱动子电路连接的存储单元行发送驱动信号。不同的是,解码器一次必须同时驱动每一个字线驱动电路中的一个驱动子电路,即在解码器的控制下,每一存储区域中均有一行存储单元行被激活。而驱动控制电路则可以对与其连接的任意驱动子电路进行独立控制,即驱动控制电路一次可以控制的驱动子电路的数量和位置均不受限定,可以根据实际需求进行选择。正是因为在存储器中增加了驱动控制电路,因此本技术提供的存储器可以利用驱动控制电路对与其连接的任意驱动子电路进行独立的驱动,使与该驱动子电路连接的存储单元行进被激活,从而可以增加存储器中对存储单元行的控制灵活。

4、示例性的,存储器中一般还包括地址缓冲器。其中,地址缓冲器可以接收外部输入的地址信息,然后根据该地址信息产生内部地址信息,并将产生的内部地址信息发送给解码器。从而解码器可以根据接收的内部地址信息向该内部地址信息选中的驱动子电路发送第一控制信号。

5、示例性的,在本技术中,每一存储区域中的多行存储单元行包括m行第一存储单元行和n行第二存储单元行,其中,n为大于或等于2且小于m的整数。其中,不同存储区域中的m行第一存储单元行的对应位置相同,例如每一存储区域中的m行第一存储单元行均为该存储区域中的第1行存储单元行至第m行存储单元行。不同存储区域中的n行第二存储单元行的对应位置相同,例如每一存储区域中的n行第二存储单元行均为该存储区域中的第m+1行存储单元行至第m+n行存储单元行。

6、其中,与第一存储单元行连接的驱动子电路为第一驱动子电路,与第二存储单元行连接的驱动子电路为第二驱动子电路。示例性的,驱动控制电路与每一字线驱动电路中的所有第二驱动子电路均连接。这样,在本技术中,每一第二驱动子电路不仅可以在接收到解码器发送的第一控制信号时向对应连接的存储单元行发送驱动信号,还可以在接收到驱动控制电路发送的第一控制信号时向对应连接的存储单元行发送驱动信号,即每一第二驱动子电路受解码器和驱动控制电路控制,只要解码器和驱动控制电路二者中其中一个向第二驱动子电路发送第一控制信号,该第二驱动子电路就可以向对应连接的存储单元行发送驱动信号。这样,利用解码器可以实现正常的读取或写入操作,对于各第二存储单元行,则可以利用驱动控制电路单独的控制任意一个第二存储单元行,从而增加对第二存储单元行的控制灵活性。

7、在具体实施时,存储阵列中存储单元整行的行数一般会比设定的行数多,例如存储阵列中设定的存储单元整行的行数为1024行,则存储阵列中实际上存在的存储单元整行的行数大于1024行,多出来的行一般称为冗余存储单元行,冗余存储单元主要用于进行修复。

8、示例性的,例如每一存储区域中的n行第二存储单元行均为冗余存储单元行,存储器在进行数据写入或读取操作时,解码器获取的内部地址信息只会选中第一存储单元行对应的行,即解码器只会向第一驱动子电路发送第一控制信号,不会向第二驱动子电路发送第一控制信号。

9、在具体实施时,当存储阵列中任意一行存储单元整行中,如有任意一个第一存储单元行中存在失效存储单元,现有技术中只能选择一整行的冗余存储单元行进行替换,即每一存储区域中均需要选择一行第二存储单元行进行替换。这样会浪费有限的冗余存储资源。

10、在本技术中,对于存在失效存储单元的任意一行第一存储单元行,可以仅在对应的存储区域中选择至少两行第二存储单元行进行修复。例如存储单元a发生失效后,会影响内存的数据保持(retention)能力并造成存储数据的翻转,如用户存储的是数据“1”,存储单元a应该是数据“1”的电荷状态,实际变成了数据“0”的电荷状态。当在选通该存储单元a时,如果不对存储单元a进行修复,实际输出为数据“0”的电荷状态。当在选通该存储单元a时,同时选通冗余存储单元b和c,即同时选通同一列上的三个存储单元,即使其中一个存储单元为失效存储单元,另外的两个存储单元的电荷与该失效存储单元的电荷进行共享。共享后的电荷量经过灵敏放大器(sense amplifier,sa)放大后也足以读出正确的数值。

11、在具体实施时,针对存在失效存储单元的任意一行第一存储单元行,对应的第二存储单元行的行数越多,修复准确率会提高,但是需要的冗余资源也会越多。一般情况下,对于一行存在失效存储单元的第一存储单元行,选择两行第二存储单元行进行修复即可。

12、因此,在一种实施例中,本技术利用驱动控制电路可以对存在失效存储单元的第一存储单元行进行修复。具体地,驱动控制电路用于对于任一存储区域,根据预存的第一驱动子电路和第二驱动子电路的对应关系,在解码器向第一子驱动电路发送控制信号时,选中与第一驱动子电路对应的第二驱动子电路,并向选中的第二驱动子电路发送第一控制信号;其中,每一第一驱动子电路对应至少两个第二驱动子电路,且不同第一驱动子电路对应的至少两个第二驱动子电路不相同。

13、以第1个存储区域的第1行存储单元行和第5行存储单元行存在失效存储单元,第2个存储区域的第2行存储单元行存在失效存储单元,第3个存储区域的第3行存储单元行存在失效存储单元,第4个存储区域的第4行存储单元行存在失效存储单元为例:针对第1个存储区域的第1行存储单元行,可以在第1个存储区域中选择两条第二存储单元行例如第m+1条存储单元行和第m+2条存储单元行对第1行存储单元行进行修复,即解码器在向每一存储区域的第1个驱动子电路发送第一控制信号时,驱动控制电路仅向第1个存储区域的第m+1个驱动子电路和第m+2个驱动子电路发送第一控制信号。针对第2个存储区域的第2行存储单元行,可以在第2个存储区域中选择两条第二存储单元行进行修复,为了节省冗余资源,可以同样选择第m+1条存储单元行和第m+2条存储单元行对第2行存储单元行进行修复,即解码器在向每一存储区域的第2个驱动子电路发送第一控制信号时,驱动控制电路仅向第2个存储区域的第m+1个驱动子电路和第m+2个驱动子电路发送第一控制信号。针对第3个存储区域的第3行存储单元行,可以在第3个存储区域中选择两条第二存储单元行进行修复,为了节省冗余资源,可以同样选择第m+1条存储单元行和第m+2条存储单元行对第3行存储单元行进行修复,即解码器在向每一存储区域的第3个驱动子电路发送第一控制信号时,驱动控制电路仅向第3个存储区域的第m+1个驱动子电路和第m+2个驱动子电路发送第一控制信号。针对第4个存储区域的第4行存储单元行,可以在第4个存储区域中选择两条第二存储单元行进行修复,为了节省冗余资源,可以同样选择第m+1条存储单元行和第m+2条存储单元行对第4行存储单元行进行修复,即解码器在向每一存储区域的第4个驱动子电路发送第一控制信号时,驱动控制电路仅向第4个存储区域的第m+1个驱动子电路和第m+2个驱动子电路发送第一控制信号。这样修复4行存储单元整行仅使用了两行冗余存储单元整行,而现有技术中则需要采用4行冗余存储单元整行,因此本技术中可以节约冗余资源。且存储阵列中的存储区域越多,节约的冗余资源越多,即冗余资源的利用率越高。

14、进一步地,针对第1个存储区域的第5行存储单元行,由于第5个存储区域中的第m+1条存储单元行和第m+2条存储单元行用于存储第1个存储区域中第1行存储单元行的数据,因此可以在第1个存储区域中选择除了第m+1条存储单元行和第m+2条存储单元行之外任意两条第二存储单元行对第5行存储单元行进行修复,例如选择第m+3条存储单元行和第m+4条存储单元行对第5行存储单元行进行修复。即解码器在向每一存储区域的第5个驱动子电路发送第一控制信号时,驱动控制电路仅向第1个存储区域的第m+3个驱动子电路和第m+4个驱动子电路发送第一控制信号。也就是说本技术中,对于存储区域中存在失效存储单元的任一第一存储单元行,都可以在该存储区域中选择任意至少两条第二存储单元行进行修复,但是对于不同的第一存储单元行,对应的至少两条第二存储单元行是不同的,即一条第二存储单元行只能对其中一行第一存储单元行进行修复。

15、在具体实施时,可以遵循上述原理,选择尽可能少的冗余资源对存在失效存储单元的存储单元行进行修复。

16、需要说明的是,本技术基于电荷共享的修复方式主要针对的是存储单元由于retention导致的失效。

17、在另一种实施例中,每一存储区域中的m行第一存储单元行均为冗余存储单元行,那么每一存储区域中的n行第二存储单元行则是存储器中设定的存储单元行,存储器在进行数据写入或读取操作时,解码器获取的内部地址信息只会选中第二存储单元行对应的行,即解码器只会向第二驱动子电路发送第一控制信号,不会向第一驱动子电路发送第一控制信号。在该实施例中,每一个第二驱动子电路还与驱动控制电路连接,即每一第二驱动子电路不仅在接收到解码器发送的第一控制信号时可以向对应的第二存储单元行发送驱动信号,而且每一第二驱动子电路还可以在接收到驱动控制电路发送的第一控制信号时向对应的第二存储单元行发送驱动信号。这样,存储器就可以实现同时驱动多行存储单元整行。

18、在又一种实施例中,驱动控制电路与每一字线驱动电路中的所有驱动子电路连接。即存储器中的任一驱动子电路,既可以在解码器的控制下向与其连接的存储单元行发送驱动信号,也可以在驱动控制电路的控制下向与其连接的存储单元行发送驱动信号。

19、示例性的,在本技术中,驱动控制电路可以包括开关选择电路、多个开关和电源电路;每一个开关的一端分别对应连接一个驱动子电路,每一个开关的另一端均与电源电路连接;开关选择电路分别与多个开关中各开关的控制端连接,用于根据接收的开关地址信息控制与该开关地址信息对应的开关处于导通状态;电源电路用于输出第一控制信号。例如,根据预存的第一驱动子电路和第二驱动子电路的对应关系,在解码器向第一子驱动电路发送控制信号时,开关选择电路接收的开关地址信息为与该第一子驱动电路对应的第二驱动子电路所连接的开关的地址,这样开关选择电路控制与该开关地址信息对应的开关处于导通状态,从而电源电路向与该第一子驱动电路对应的第二驱动子电路发送第一控制信号。

20、本技术中驱动控制电路中开关的数量等于该驱动控制电路所连接的驱动子电路的数量,每一开关连接一个驱动子电路。开关选择电路可以独立控制任一个开关的导通和截止。

21、在一种可行的实施方式中,开关选择电路可以为多路复用器,当然开关选择电路也可以是其它能够实现开关选择电路功能的电路结构,在此不作限定。

22、在具体实施时,存储器一般会在芯片中加入内置自我检测(build-in-self-test,bist)模块,内置自我分析(build-in-self-analysis,bisa)模块和内置自我修复(build-in-self-repair,bisr)模块。其中,bist模块可精确地确认存储器中的失效存储单元,bisa模块可以根据存储器中的冗余结构,计算得到合适的修复方案,从而尽量少的资源的情况下修复更多的错误。bisr模块可以根据bisa模块确定的修复方案控制驱动控制电路实现修复。例如,bisr模块可以根据bisa模块确定的修复方案配置冗余控制信号,例如用于表征上述实施例提到的开关地址信息的信号。为了避免掉电丢失,bisr模块中的一次性可编程存储器(efuse)模块用于存储冗余控制信息,例如本技术上述实施例提到的“预存的第一驱动子电路和第二驱动子电路的对应关系”。

23、第二方面,本技术还提供了一种存储器,该存储器包括存储阵列和如第一方面或第一方面的各种实施方式所述的存储控制电路。其中,存储阵列包括沿字线方向排列的多个存储区域,多个存储区域中每一存储区域中均包括多行存储单元行。存储控制电路包括解码器,多个字线驱动电路和驱动控制电路。多个字线驱动电路中每一字线驱动电路中均包括多个驱动子电路,多个驱动子电路中每一驱动子电路连接对应的存储区域中的一行存储单元行,用于向该存储单元行发送驱动信号。解码器与多个字线驱动电路中每一字线驱动电路中的多个驱动子电路连接;解码器用于向多个字线驱动电路中每一字线驱动电路中被选中的其中一个驱动子电路同时发送第一控制信号,以控制被选中的各驱动子电路同时向对应的存储单元行发送驱动信号。驱动控制电路与多个字线驱动电路中每一字线驱动电路中至少部分驱动子电路连接;驱动控制电路用于独立的向与其连接的任意驱动子电路发送第一控制信号,以控制该驱动子电路向对应的存储单元行发送驱动信号。在本技术中,解码器一次必须同时驱动每一个字线驱动电路中的一个驱动子电路,即在解码器的控制下,每一存储区域中均有一行存储单元行被激活。而驱动控制电路则可以对与其连接的任意驱动子电路进行独立控制,即驱动控制电路一次可以控制的驱动子电路的数量和位置均不受限定,可以根据实际需求进行选择。正是因为在存储器中增加了驱动控制电路,因此本技术提供的存储器可以利用驱动控制电路对与其连接的任意驱动子电路进行独立的驱动,使与该驱动子电路连接的存储单元行进被激活,从而可以增加存储器中对存储单元行的灵活控制。

24、第三方面,本技术还提供了一种电子设备,该电子设备包括处理器和与该处理器耦合如第二方面所述的存储器,该存储器用于存储处理器产生的数据。由于该电子设备解决问题的原理与前述一种存储器相似,因此该电子设备的实施可以参见前述存储器的实施,重复之处不再赘述。

25、上述第二方面和第三方面可以达到的技术效果可以参照上述第一方面中任一可能设计可以达到的技术效果说明,这里不再重复赘述。

26、第四方面,本技术实施例还提供了一种存储器的修复方法,存储器包括多个存储区域,多个存储区域中每一存储区域中均包括多行存储单元行该修复方法可以包括以下步骤:首先获取每一存储区域中存在失效存储单元的存储单元行,为了便于理解,将存在失效存储单元的存储单元行称为故障行;然后在多个存储区域中每一存储区域中均选取m行存储单元行作为第一存储单元行;在多个存储区域中每一存储区域中均选取n行存储单元行作为第二存储单元行,其中,n为大于或等于2且小于m的整数,且第二存储单元行中不存在失效存储单元;针对所有第一存储单元行中存在的至少一行故障行,在故障行所在的存储区域中选择至少两行第二存储单元行作为故障行对应的修复行,其中不同故障行对应的修复行不相同;在驱动故障行时,同时驱动与该故障行对应的修复行。

27、需要说明的是,本技术失效存储单元是指存储单元由于retention导致的失效。

28、示例性的,多个存储区域中,不同存储区域中的m行第一存储单元行的排列位置均相同。例如,每一存储区域中,第1行至第m行的存储单元均为第一存储单元行,或者,每一存储区域中,第2行至第m+1行的存储单元均为第一存储单元行等。

29、示例性的,多个存储区域中,不同存储区域中的n行第二存储单元行的排列位置均相同。例如,每一存储区域中,第m+1行至第m+n行的存储单元均为第二存储单元行,或者,每一存储区域中,第m+2行至第m+n+1行的存储单元均为第二存储单元行等。

30、在具体实施时,例如第1个存储区域中存在多行故障行,针对其中两行故障行中的任意一行故障行,可以在第1个存储区域中的所有第二存储单元行中选择至少两行第二存储单元行作为该故障行对应的修复行,例如针对第一行故障行选择两行第二存储单元行作为该故障行对应的修复行,针对第二行故障行选择两行第二存储单元行作为该故障行对应的修复行,但是第一行故障行对应的两行修复行与第二行故障行对应的两行修复行是完全不相同的两行修复行。遵循采用尽量少的冗余资源修复尽量多的错误的原则,对于第1个存储区域中的其它故障行,也可以采用本技术提供的修复方法进行修复,或者也可能会采用其它的合适的修复方法进行修复,在此不作限定。

31、示例性的,在一种实施例中,在多个存储区域中,同一位置处属于不同存储区域的多个第一存储单元行中,故障行的数量小于或等于1。例如多个存储区域为x个存储区域,针对第一行第一存储单元行的位置,每一个存储区域存在一行第一行第一存储单元行,存储器存在x个第一行第一存储单元行,在该x个第一行第一存储单元行,故障行的数量不超过1,即该x个第一行第一存储单元行中均不存在失效存储单元,或者该x个第一行第一存储单元行中只能有一个存储区域中的第一行第一存储单元行中存在失效存储单元。这是因为,当该x个第一行第一存储单元行中有多个存储区域中的第一行第一存储单元行中存在失效存储单元,可以直接采用一行冗余的存储单元整行进行替换,而采用本技术提供的修复方法则需要至少两行第二存储单元行才能修复。因此,在本技术中,在选择第一存储单元行时,优选同一位置处属于不同存储区域的多个第一存储单元行中,故障行的数量小于或等于1。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183162.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表