低压存储单元读出锁存电路的制作方法

- 国知局

- 2024-07-31 19:39:03

本发明涉及半导体电路技术,特别是涉及一种低压存储单元读出锁存电路。

背景技术:

1、现有一种存储器读取灵敏放大器锁存电路(sa-latch)如图1所示,由于作为其差分比较锁存器的状态锁存管的第五nmos管nm5、第六nmos管nm6的阈值电压vth(约0.7v)较高,第五pmos管pm5、第六pmos管pm6、第五nmos管nm5、第六nmos管nm6的均需要栅极电压超过阈值电压vth(0.7v)才能正常工作,所以要求电源电压高于2个阈值vt(1.5v附近),当工作电压vdd较低时不能正常工作。

技术实现思路

1、本发明要解决的技术问题是提供一种存储单元读出锁存电路,在工作电压vdd较低时也能正常工作。

2、为解决上述技术问题,本发明提供的存储单元读出锁存电路,其使用在栅源电压小于0.1v时在源漏之间形成有导电沟道的native管作为差分比较锁存器的状态锁存管。

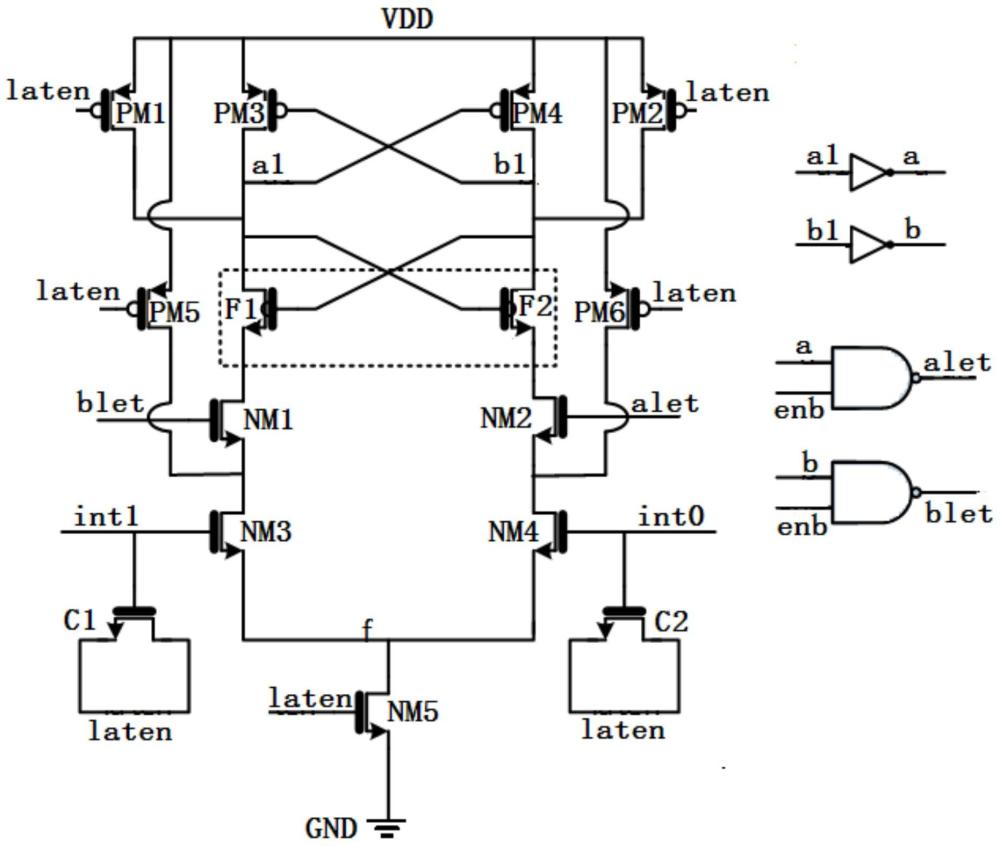

3、可选的,所述存储单元读出锁存电路,包括第一pmos管pm1、第二pmos管pm2、第三pmos管pm3、第四pmos管pm4、第五pmos管pm5、第六pmos管pm6、第一nmos管nm1、第二nmos管nm2、第三nmos管nm3、第四nmos管nm4、第零mos管m0、第一native管f1及第二native管f2;

4、所述第一pmos管pm1、第二pmos管pm2、第三pmos管pm3、第四pmos管pm4、第五pmos管pm5及第六pmos管pm6的源端接工作电压vdd;

5、所述第一pmos管pm1漏端、第三pmos管pm3漏端、第四pmos管pm4栅端、第一native管f1源漏一端、第二native管f2栅端同接a1节点;

6、所述第二pmos管pm2漏端、第四pmos管pm4漏端、第三pmos管pm3栅端、第二native管f2源漏一端、第一native管f1栅端同接b1节点;

7、所述第一nmos管nm1,其漏端接第一native管f1源漏另一端,其源端接第五pmos管pm5漏端及第三nmos管nm3漏端;

8、所述第二nmos管nm2,其漏端接第二native管f2源漏另一端,其源端接第六pmos管pm6漏端及第四nmos管nm4漏端;

9、所述第三nmos管nm3源端及第四nmos管nm4源端同接第零mos管m0源漏一端;

10、所述第零mos管m0源漏另一端接地;

11、所述第三nmos管nm3栅端用于接存储单元的存储状态电压int1;

12、所述第四nmos管nm4栅端用于接存储单元的参考状态电压int0;

13、所述第二nmos管nm2栅端接a锁存信号alat,a锁存信号alat是a1节点信号经反相后同工作模式选择信号enb进行与非运算得到;

14、所述第一nmos管nm1栅端接b锁存信号blat,b锁存信号blat是b1节点信号经反相后同工作模式选择信号enb进行与非运算得到;

15、第一pmos管pm1、第二pmos管pm2、第五pmos管pm5、第六pmos管pm6及第零mos管m0的栅端同接锁存使能信号laten;

16、在栅源电压小于0.1v时,第一native管f1、第二native管f2的源漏之间均形成有导电沟道。

17、可选的,所述存储单元读出锁存电路还包括第一电容c1及第二电容c2;

18、所述第一电容c1一端接存储单元的存储状态电压int1,另一端接锁存使能信号laten;

19、所述第二电容c2一端接存储单元的参考状态电压int0,另一端接锁存使能信号laten。

20、可选的,所述第一电容c1由第一mos管构成;

21、所述第二电容c2分别由第二mos管构成;

22、所述第一mos管的栅极作为第一电容c1的一端,所述第一mos管的源漏短接作为第一电容c1的另一端;

23、所述第二mos管的栅极作为第二电容c2的一端,所述第二mos管的源漏短接作为第二电容c2的另一端。

24、可选的,所述第一mos管、第二mos管均为nmos管。

25、可选的,所述第零mos管m0为nmos管,其源端接地,漏端接所述第三nmos管nm3源端及第四nmos管nm4源端。

26、可选的,所述第一native管f1、第二native管f2均为nmos管。

27、可选的,所述第一native管f1、第二native管f2均为耗尽型场效应管。

28、可选的,所述第一native管f1、第二native管f2均为耗尽型mos管。

29、可选的,所述第一native管f1、第二native管f2均为结型场效应管。

30、本发明的存储单元读出锁存电路,使用在栅源电压小于0.1v时在源漏之间形成有导电沟道的native管作为差分比较锁存器的状态锁存管。在锁存数据时,由于第一native管、第二native管栅源电压很低时的源漏之间均能形成有导电沟道,所以工作电压只要不低于0.9v便能保证存储单元读出锁存电路正常工作。

技术特征:1.一种存储单元读出锁存电路,其特征在于,使用在栅源电压小于0.1v时在源漏之间形成有导电沟道的native管作为差分比较锁存器的状态锁存管。

2.根据权利要求1所述的存储单元读出锁存电路,其特征在于,其包括第一pmos管(pm1)、第二pmos管(pm2)、第三pmos管(pm3)、第四pmos管(pm4)、第五pmos管(pm5)、第六pmos管(pm6)、第一nmos管(nm1)、第二nmos管(nm2)、第三nmos管(nm3)、第四nmos管(nm4)、第零mos管(m0)、第一native管(f1)及第二native管(f2);

3.根据权利要求2所述的存储单元读出锁存电路,其特征在于,

4.根据权利要求3所述的存储单元读出锁存电路,其特征在于,

5.根据权利要求4所述的存储单元读出锁存电路,其特征在于,

6.根据权利要求2所述的存储单元读出锁存电路,其特征在于,

7.根据权利要求2所述的存储单元读出锁存电路,其特征在于,

8.根据权利要求2所述的存储单元读出锁存电路,其特征在于,

9.根据权利要求2所述的存储单元读出锁存电路,其特征在于,

10.根据权利要求2所述的存储单元读出锁存电路,其特征在于,

技术总结本发明公开了一种存储单元读出锁存电路,使用在栅源电压小于0.1V时在源漏之间形成有导电沟道的native管作为差分比较锁存器的状态锁存管。在锁存数据时,由于第一native管、第二native管栅源电压很低时的源漏之间均能形成有导电沟道,所以工作电压只要不低于0.9V便能保证存储单元读出锁存电路正常工作。技术研发人员:罗光燕受保护的技术使用者:普冉半导体(上海)股份有限公司技术研发日:技术公布日:2024/2/19本文地址:https://www.jishuxx.com/zhuanli/20240731/183413.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表