输出驱动电路及存储器的制作方法

- 国知局

- 2024-07-31 19:46:58

本公开涉及半导体电路设计领域,特别涉及一种输出驱动电路及存储器。

背景技术:

1、动态随机存储器(dynamic random access memory,dram)由于其存储密度高、传输速度快等特点,广泛应用于现代电子系统中,由于存储器需要进行大量的数据输入和数据输出,因此对存储器输入电路或输出电路的性能改进对存储器的性能提升有着重要意义。

2、然而申请人发现:目前存储器的信号输出基于同一输出电路完成对不同数据的输出,造成了不必要的功耗浪费。

技术实现思路

1、本公开实施例提供一种输出驱动电路及存储器,以采用不同的输出通道实现对高速信号和低速信号的传输,保证输出数据准确性的同时,减小存储器的功耗。

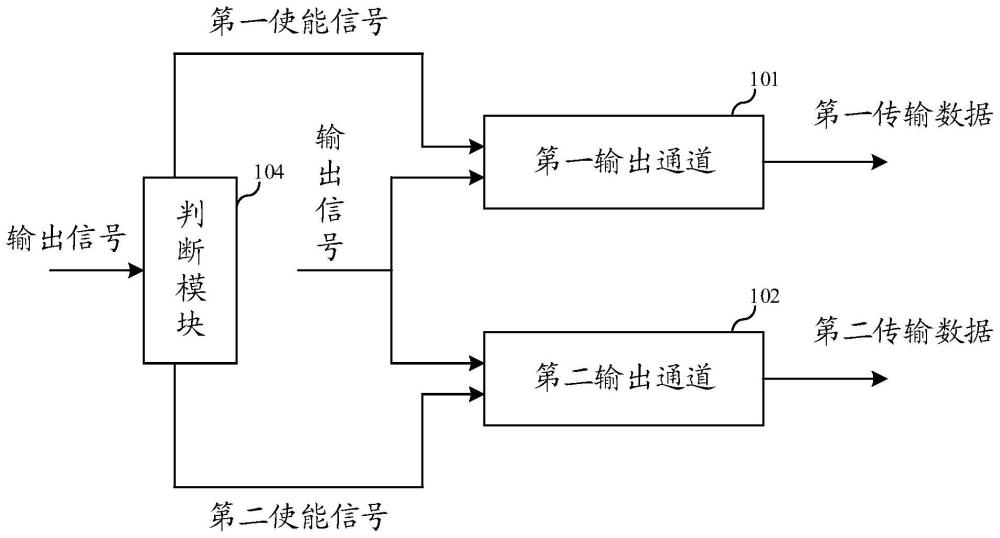

2、本公开一实施例提供了一种输出驱动电路,包括:判断模块,被配置为,判断待输出的输出信号是否为高速信号,若输出信号为高速信号,则生成第一使能信号,若输出信号为低速信号,则生成第二使能信号;第一输出通道,连接判断模块,被配置为,基于第一使能信号,传输输出信号,以输出第一传输数据;第二输出通道,连接判断模块,被配置为,基于第二使能信号,传输输出信号,以输出第二传输数据;其中,第一输出通道中驱动器的数量大于第二输出通道中驱动器的数量。

3、基于对输出信号的判断确认输出信号为高速信号或低速信号,然后通过第一输出通道对高速信号进行驱动以输出第一传输数据,通过第二输出通道对低速信号进行驱动以输出第二传输数据,而第一输出通道中驱动器的数量大于第二输出通道中驱动器的数量,通过对高速信号和低速信号设计不同的输出通道,减少第二输出通道中驱动器的数量,从而降低低速信号传输过程中存储器的功耗,并保证高速信号传输过程中的数据速率。

4、另外,第一输出通道,包括:第一驱动单元,包括串联的a级驱动器;第一导通单元,串联于第一驱动单元的传输路径中,被配置为,基于第一使能信号,导通第一驱动单元的传输路径;第二输出通道,包括:第二驱动单元,包括串联的b级驱动器;第二导通单元,串联于第二驱动单元的传输路径中,被配置为,基于第二使能信号,导通第二驱动单元的传输路径;其中,a和b为正整数,且a>b。

5、另外,第一输出通道包括驱动单元、选择单元和第一传输单元,第二输出通道包括驱动单元、选择单元和第二传输单元,且第二输出通道与第一输出通道共用驱动单元和选择单元;驱动单元包括串联的c级驱动器;选择单元的输入端连接驱动单元,一输出端连接第一传输单元,另一输出端连接第二传输单元,被配置为,基于第一使能信号导通第一传输单元,或基于第二使能信号导通第二传输单元;其中,c为正整数,第一传输单元中驱动器的数量大于第二传输单元中驱动器的数量。

6、另外,第二传输单元中驱动器的数量为0。

7、另外,第一输出通道,包括:第一上拉通路和第一下拉通路,第一上拉通路包括第一导通单元和串联的x级第一反相器,第一下拉通路包括第二导通单元和串联的x级第二反相器;第一导通单元被配置为,基于第一使能信号,导通第一上拉通路;第二导通单元被配置为,基于第一使能信号,导通第一下拉通路;第二输出通道,包括:第二上拉通路和第二下拉通路,第二上拉通路包括第三导通单元和串联的y级第三反相器,第二下拉通路包括第四导通单元和串联的y级第四反相器;第三导通单元被配置为,基于第二使能信号,导通第二上拉通路;第四导通单元被配置为,基于第二使能信号,导通第二下拉通路;其中,x和y为正整数,且x>y。

8、另外,第一导通单元基于第一三态门设置;第一三态门串联于x级第一反相器的传输通路上,控制端用于接收第一使能信号;第二导通单元基于第二三态门设置;第二三态门串联于x级第二反相器的传输通路上,控制端用于接收第一使能信号;第三导通单元基于第三三态门设置;第三三态门串联于y级第三反相器的传输通路上,控制端用于接收第二使能信号;第四导通单元基于第四三态门设置;第四三态门串联于y级第四反相器的传输通路上,控制端用于接收第二使能信号;其中,x和y为正奇数。

9、另外,x与y的差值为2、4、6或8。

10、另外,第一反相器中晶体管的阈值电压小于第三反相器中晶体管的阈值电压,且第二反相器中晶体管的阈值电压小于第四反相器中晶体管的阈值电压,以使得第二输出通道的开启程度减小,从而进一步减小存储器的功耗。

11、另外,第一反相器中晶体管的阈值电压与第二反相器中晶体管的阈值电压相同,第三反相器中晶体管的阈值电压与第四反相器中晶体管的阈值电压相同。

12、另外,第一导通单元和第三导通单元基于第一选择电路设置,第一选择电路的一输入端连接第一上拉通路,另一输入端连接第二上拉通路;第一选择电路被配置为,基于第一使能信号导通第一上拉通路,或基于第二使能信号导通第二上拉通路;第二导通单元和第四导通单元基于第二选择电路设置,第二选择电路的一输入端连接第一下拉通路,另一输入端连接第二下拉通路;第二选择电路被配置为,基于第一使能信号导通第一下拉通路,或基于第二使能信号导通第二下拉通路;其中,x和y为正偶数。

13、另外,输出驱动电路,还包括:第三输出通道,包括串联的d级驱动器,被配置为,传输输出信号对应的预加重指示信号;处理电路,连接第一输出通道、第二输出通道和第三输出通道的输出端,被配置为,基于预加重指示信号,对第一传输数据或第一传输数据以及第二传输数据进行预加重;d为正整数。在高速信号传输中,信号链路对高速信号和低速信号的传输存在一定的衰减,且对高频信号的衰减大于低频信号的衰减,从而导致了高速信号中高频和低频之间巨大的幅度差,通过第三输出通路对第一传输数据进行预加重,以平衡高频分量和低频分量,减少传输链路对高频分量衰减大于低频分量对最终结果的影响。

14、另外,预加重指示信号包括上拉加重指示信号和下拉加重指示信号,第三输出通道,包括:多个第三上拉通路,每一第三上拉通路中包括串联的d级驱动器,第三上拉通路用于传输上拉加重指示信号;多个第三下拉通路,每一第三下拉通路中包括串联的d级驱动器,第三下拉通路用于传输下拉加重指示信号。

15、另外,d的值与a的值相同,以使得输出驱动电路对于高速信号和高速信号相应的预加重指示信号的驱动能力相同,以确保对于第一输出通道输出的第一传输数据预加重的准确性。

16、另外,输出驱动电路还包括:控制模块,被配置为,在测试模式下获取第一传输数据所需上拉预加重的幅度和下拉预加重的幅度,并基于上拉预加重的幅度生成第一选择信号,第一选择信号用于选择导通第三上拉通路的数量,还基于下拉预加重的幅度生成第二选择信号,第二选择信号用于选择导通第三下拉通路的数量。

17、本公开又一实施例还提供了一种存储器,包括上述实施例提供的输出驱动电路,以采用不同的输出通道实现对高速信号和低速信号的传输,保证输出数据准确性的同时,减小存储器的功耗。

技术特征:1.一种输出驱动电路,其特征在于,包括:

2.根据权利要求1所述的输出驱动电路,其特征在于,包括:

3.根据权利要求1所述的输出驱动电路,其特征在于,包括:

4.根据权利要求3所述的输出驱动电路,其特征在于,所述第二传输单元中驱动器的数量为0。

5.根据权利要求1所述的输出驱动电路,其特征在于,包括:

6.根据权利要求5所述的输出驱动电路,其特征在于,包括:

7.根据权利要求6所述的输出驱动电路,其特征在于,所述x与所述y的差值为2、4、6或8。

8.根据权利要求5或6所述的输出驱动电路,其特征在于,所述第一反相器中晶体管的阈值电压小于所述第三反相器中晶体管的阈值电压,且所述第二反相器中晶体管的阈值电压小于所述第四反相器中晶体管的阈值电压。

9.根据权利要求8所述的输出驱动电路,其特征在于,所述第一反相器中晶体管的阈值电压与所述第二反相器中晶体管的阈值电压相同,所述第三反相器中晶体管的阈值电压与所述第四反相器中晶体管的阈值电压相同。

10.根据权利要求5所述的输出驱动电路,其特征在于,包括:

11.根据权利要求5所述的输出驱动电路,其特征在于,还包括:

12.根据权利要求11所述的输出驱动电路,其特征在于,所述预加重指示信号包括上拉加重指示信号和下拉加重指示信号,所述第三输出通道,包括:

13.根据权利要求11或12所述的输出驱动电路,其特征在于,所述d的值与所述a的值相同。

14.根据权利要求12所述的输出驱动电路,其特征在于,还包括:控制模块,被配置为,在测试模式下获取所述第一传输数据所需上拉预加重的幅度和下拉预加重的幅度,并基于所述上拉预加重的幅度生成第一选择信号,所述第一选择信号用于选择导通所述第三上拉通路的数量,还基于所述下拉预加重的幅度生成第二选择信号,所述第二选择信号用于选择导通所述第三下拉通路的数量。

15.一种存储器,其特征在于,包括权利要求1~14任一项所述的输出驱动电路。

技术总结本公开涉及半导体电路设计领域,特别涉及一种输出驱动电路及存储器,输出驱动电路包括:判断模块,被配置为,判断待输出的输出信号是否为高速信号,若输出信号为高速信号,则生成第一使能信号,若输出信号为低速信号,则生成第二使能信号;第一输出通道,连接判断模块,被配置为,基于第一使能信号,传输输出信号,以输出第一传输数据;第二输出通道,连接判断模块,被配置为,基于第二使能信号,传输输出信号,以输出第二传输数据;其中,第一输出通道中驱动器的数量大于第二输出通道中驱动器的数量,以采用不同的输出通道实现对高速信号和低速信号的传输,保证输出数据准确性的同时,减小存储器的功耗。技术研发人员:刘忠来受保护的技术使用者:长鑫存储技术有限公司技术研发日:技术公布日:2024/3/31本文地址:https://www.jishuxx.com/zhuanli/20240731/184024.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表