用于静态随机存取内存的输出控制接口的制作方法

- 国知局

- 2024-07-31 19:37:33

本发明涉及一种输出控制接口及输出控制方法,特别是涉及一种用于静态随机存取内存的输出控制接口及输出控制方法。

背景技术:

1、在asic设计中静态随机存取内存(static random access memory,sram)被广泛的使用。一般而言,在sram中,外部电路通过控制信号控制对sram进行读操作或写操作。由于sram属于挥发性内存,当电源停止供应时,sram储存的数据会消失。因此,当系统上电后,sram内部的数据是不可预期的。此外,在上电过程中,频率信号和控制信号尚未稳定前,也可能会造成sram输出不稳定,进而影响相关电路的运作。

2、在集成电路设计中的电路布局后仿真(post-layout simulation)阶段,上述的非预期输出在模拟过程中会被视为未知并且向后传递,造成模拟结果失败,在此阶段,除错通常需要花费大量时间来追踪网表(netlist),修正错误后也需要较长的时间重新执行闸位准模拟(gate-level simulation),造成不必要的除错时间。

技术实现思路

1、本发明所要解决的技术问题在于,针对现有技术的不足提供一种用于静态随机存取内存的输出控制接口及输出控制方法。

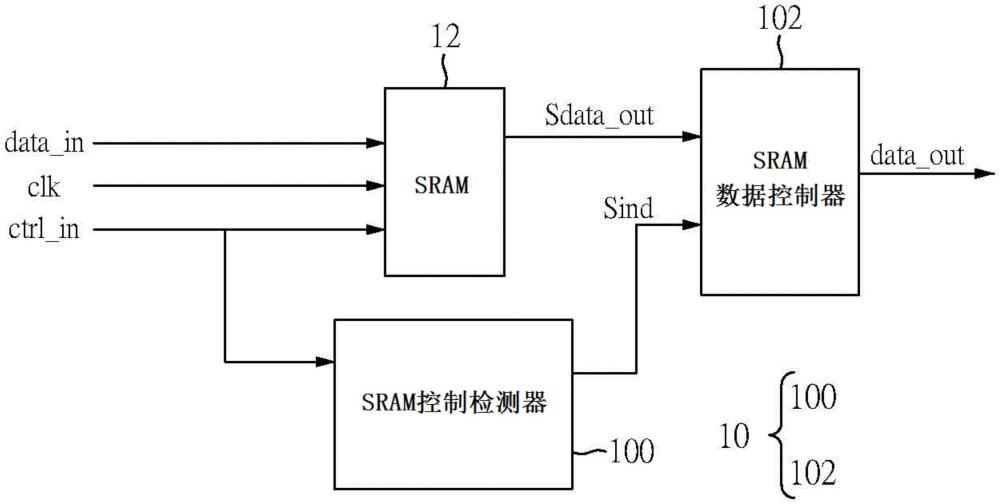

2、为了解决上述的技术问题,本发明所采用的其中一种技术方案是提供一种输出控制接口,适用于静态随机存取内存(static random access memory,sram),其包括sram控制检测器和sram数据控制器。sram控制检测器,接收输入该sram的控制信号,并被配置为判断该控制信号是否稳定,并对应输出指示信号。sram数据控制器,被配置为接收该指示信号和该sram控制检测器输出的sram输出数据信号并依据该指示信号输出输出数据信号。其中,响应于判断该控制信号并未稳定,该sram控制检测器输出该指示信号以指示该控制信号并未稳定,该sram数据控制器对应输出具有预设值的该输出数据信号。其中,响应于判断该控制信号已经稳定,该sram控制检测器输出该指示信号以指示该控制信号已经稳定,该sram数据控制器对应输出该sram输出数据信号作为该输出数据信号。

3、为了解决上述的技术问题,本发明所采用的另外一种技术方案是提供一种输出控制方法,适用于静态随机存取内存(static random access memory,sram),其包括:配置sram数据控制器接收该指示信号和该sram输出的sram输出数据信号;配置sram控制检测器接收输入该sram的控制信号,并判断该控制信号是否稳定,并对应输出指示信号;响应于判断该控制信号并未稳定,配置该sram控制检测器输出该指示信号以指示该控制信号并未稳定,且配置该sram数据控制器依据该指示信号对应输出具有预设值的该输出数据信号;以及响应于判断该控制信号已经稳定,该sram控制检测器输出该指示信号以指示该控制信号已经稳定,且配置该sram数据控制器依据该指示信号对应输出该sram输出数据信号作为该输出数据信号。

4、本发明的有益效果在于,本发明所提供的用于静态随机存取内存的输出控制接口及输出控制方法,可通过更好的控制方式消除sram尚未被使用前输出不稳定造成的影响,特别是可以在电路布局后仿真阶段中降低不必要的除错时间。

5、为使能更进一步了解本发明的特征和技术内容,请参阅以下有关本发明的详细说明与附图,然而所提供的附图仅用于提供参考与说明,并非用来对本发明加以限制。

技术特征:1.一种输出控制接口,适用于静态随机存取内存,其特征在于,所述输出控制接口包括:

2.如权利要求1所述的输出控制接口,其特征在于,所述sram控制检测器包括有限状态机电路。

3.如权利要求1所述的输出控制接口,其特征在于,所述sram数据控制器包括组合逻辑电路。

4.如权利要求1所述的输出控制接口,其特征在于,所述sram控制检测器通过检测所述控制信号是否在写操作之后出现第一次读操作以判断所述控制信号是否已经稳定。

5.如权利要求1所述的输出控制接口,其特征在于,所述sram控制检测器进一步接收系统重置信号和输入所述sram的第一频率信号,且被配置为在判断所述控制信号是否稳定之前先判断所述系统重置信号是否稳定,

6.如权利要求5所述的输出控制接口,其特征在于,在判断所述系统重置信号已经稳定后,但尚未判断所述控制信号是否稳定前,所述sram控制检测器输出所述指示信号以指示所述sram数据控制器输出具有所述预设值的所述输出数据信号。

7.如权利要求5所述的输出控制接口,其特征在于,所述sram控制检测器进一步接收第二频率信号,且被配置为通过所述第二频率信号检测所述系统重置信号是否稳定。

8.如权利要求7所述的输出控制接口,其特征在于,所述第二频率信号的频率高于所述第一频率信号。

9.如权利要求7所述的输出控制接口,其特征在于,所述sram控制检测器被配置为进一步在进入系统上电状态并经过预定时间后,判断所述系统重置信号是否稳定。

10.如权利要求9所述的输出控制接口,其特征在于,所述sram控制检测器进一步接收电源重置信号,且被配置为依据所述电源重置信号判断是否进入所述系统上电状态,以及依据所述第二频率信号判断是否经过所述预定时间。

技术总结本发明公开一种用于静态随机存取内存的输出控制接口。输出控制接口包括SRAM控制检测器和SRAM数据控制器。SRAM控制检测器接收输入SRAM的控制信号,并判断控制信号是否稳定,并对应输出指示信号。SRAM数据控制器接收指示信号和SRAM控制检测器输出的SRAM输出数据信号,并依据指示信号输出输出数据信号。其中,响应于判断该控制信号并未稳定,SRAM数据控制器对应输出具有预设值的输出数据信号。响应于判断该控制信号已经稳定,SRAM数据控制器对应输出SRAM输出数据信号作为输出数据信号。技术研发人员:吴国吉受保护的技术使用者:瑞昱半导体股份有限公司技术研发日:技术公布日:2024/2/1本文地址:https://www.jishuxx.com/zhuanli/20240731/183270.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。