面向高能效存内计算的低温准静态嵌入式DRAM

- 国知局

- 2024-07-31 19:52:29

本发明涉及一种低温准静态嵌入式存储器设计。

背景技术:

1、随着时间的推移,逻辑-存储器差距不断扩大,内存访问已成为数据密集型应用中计算性能的主要瓶颈[1-2]。一种有前景的解决方案是存内计算(cim),它通常用于减轻由于数据传输而导致的处理单元和存储之间的开销[3-4]。一般来说,为了实现能效高的cim,存储设计需要满足高速、高容量、高可靠性和低功耗的要求。图一展示了一个典型的cim框架,其中存储拓扑结构可以使用静态随机存取存储器(sram)、动态随机存取存储器(dram)或非易失性存储器模块(如电阻随机存取存储器(rram)和磁随机存取存储器(mram))来实现[5-8]。在已有存储器技术中,嵌入式dram(edram)由于其工艺兼容性和高密度而成为一个有吸引力的选择。然而,与交叉耦合sram电路不同,edram缺乏锁存器设计,这不可避免地导致数据浮动。因此,需要引入了强制刷新操作(刷新周期范围从微秒到毫秒)来保持数据的可靠性,这反过来造成了额外的功耗开销,并降低数据访问效率。因此,edram的动态存储特性限制了室温下基于dram构成cim的计算能效,特别是对于复杂的神经网络计算应用。

2、鉴于edram固有的动态存储特性是由泄漏引起的有限保留时间(范围从微秒到毫秒),以前的研究努力通过各种手段优化其性能[9]。例如,为了延长数据保留时间,提出了内部反馈来补偿存储节点的泄漏[10];同时,采用了字线电压增强技术来确保“1”或“0”的可靠存储,但这些策略会增加功耗并降低器件可靠性[11]。另一种选择是基于金属-氧化物-半导体场效应晶体管(mosfet)的工作原理(即edram的基本单元),亚阈值区域的泄漏电流isub与温度t呈指数关系(即,isub∝exp(-ev/kt),其中e为电子电荷,k为玻尔兹曼常数,v为晶体管的栅电压)。在这种情况下,低温下mosfet的低泄漏模式可以原则上显著增强edram单元中数据存储的稳定性,且无需进行刷新操作。因此,将这种低温准静态edram(cqs-edram)模块集成到cim架构(图1的b)中,不仅可以增加存储密度(由于简化的存储器电路),还可以提高系统的计算效率。

3、[1]mark horowitz.1.1 computing’s energy problem(and what we candoabout it).in 2014 ieee international solid-state circuits conference digestoftechnical papers(isscc),pages 10–14,2014.

4、[2]xiaowei xu,yukun ding,sharon xiaobo hu,michael niemier,jason cong,yu hu,and yiyu shi.scaling for edge inference of deep neuralnetworks.natureelectronics,1(4):216–222,2018.

5、[3]stefano ambrogio,pritish narayanan,hsinyu tsai,robert m shelby,iremboybat,carmelo di nolfo,severin sidler,massimo giordano,martina bodini,nathan cp farinha,et al.equivalent-accuracy accelerated neural-networktraining using analogue memory.nature,558(7708):60–67,2018.

6、[4]daniele ielmini and h-s philip wong.in-memory computingwithresistive switching devices.nature electronics,1(6):333–343,2018.

7、[5]chen,zhengyu,xi chen,and jie gu."15.3 a 65nm 3t dynamic analogram-based computing-in-memory macro and cnn accelerator withretentionenhancement,adaptive analog sparsity and 44tops/w systemenergyefficiency."2021 ieee international solid-state circuits conference(isscc).vol.64.ieee,2021.

8、[6]xie,shanshan,et al."16.2 edram-cim:compute-in-memory designwithreconfigurable embedded-dynamic-memory array realizing adaptivedataconverters and charge-domain computing."2021 ieee international solid-statecircuits conference(isscc).vol.64.ieee,2021.

9、[7]fujiwara,hidehiro,et al."a 5-nm 254-tops/w 221-tops/mm 2fully-digital computing-in-memory macro supporting wide-rangedynamic-voltage-frequency scaling and simultaneous mac and writeoperations."2022 ieeeinternational solid-state circuits conference(isscc).vol.65.ieee,2022.

10、[8]weier wan,rajkumar kubendran,clemens schaefer,sukru burceryilmaz,wenqiang zhang,dabin wu,stephen deiss,priyanka raina,he qian,bin gao,et al.acompute-in-memory chip based on resistive random-access memory.nature,608(7923):504–512,2022.

11、[9]a.agarwal,s.mukhopadhyay,a.raychowdhury,k.roy,and c.h.kim.leakagepower analysis and reduction for nanoscale circuits.ieee micro,26(2):68–80,mar.2006.

12、[10]robert giterman,alexander fish,andreas burg,and adam teman.a4-transistor nmos-only logic-compatible gain-cell embedded dram with over1.6-msretention time at 700mv in 28-nm fd-soi.ieee transactions on circuits andsystems i:regular papers,65(4):1245–1256,apr.2018.

13、[11]j.r.hoff,g.w.deptuch,guoying wu,and ping gui.cryogenic lifetimestudies of 130nm and 65nm nmos transistors for high-energy physics experi-ments.ieee transactions on nuclear science,62(3):1255–1261,jun.2015.

14、[12]theodore van duzer,lizhen zheng,stephen r.whiteley,hoki kim,jaewoo kim,xiaofan meng,and thomas ortlepp.64-kb hybrid josephson-cmos4kelvin ram with 400ps access time and 12mw read power.ieee transactions onapplied super-conductivity,23(3):1700504–1700504,jun.2013.

15、[13]masamitsu tanaka,masato suzuki,gen konno,yuki ito,akira fujimaki,and nobuyuki yoshikawa.josephson-cmos hybrid memory with nanocry-otrons.ieeetransactions on applied supercon-ductivity,27(4):1–4,jun.2017.

16、[14]gyu-hyeon lee,seongmin na,ilkwon byun,dong-moon min,and jangwookim.cryoguard:a near refresh-free robust dram design for cryogeniccomputing.in 2021acm/ieee 48th annual international symposium on computerarchitecture(isca),pages 637–650,jun.2021.

17、[15]rakshith saligram,suman datta,and arijit ray-chowdhury.cryomem:a4k-300k 1.3ghz edram macro with hybrid 2t-gain-cell in a 28nm logic pro-cessfor cryogenic applications.in 2021ieee cus-tom integrated circuits conference(cicc),pages 1–2,apr.2021.

技术实现思路

1、本发明的目的是:提供一种低温准静态edram(cqs-edram)模块,将其集成到cim架构后,增加存储密度(由于简化的存储器电路)的同时,提高系统的计算效率。

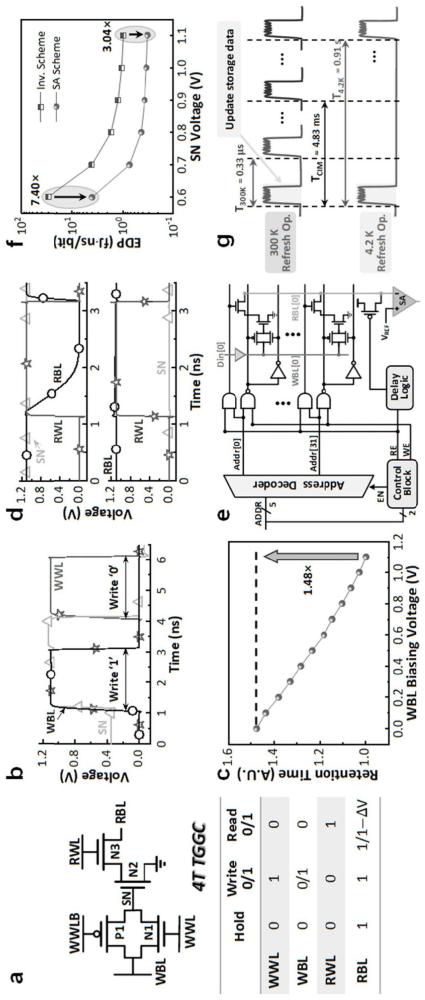

2、为了达到上述目的,本发明的技术方案是提供了一种面向高能效存内计算的低温准静态嵌入式dram,其特征在于,低温准静态嵌入式dram阵列由4ttggc存储单元组成,每个4t tggc存储单元由一个pmos晶体管p1以及三个nmos晶体管n1、n2、n3组成,其中:

3、平行配置的一个pmos晶体管p1以及一个nmos晶体管n1构成了基于传输门的写入端口拓扑结构,pmos晶体管由写入字线栏wwlb控制,nmos晶体管由写入字线wwl控制;

4、剩余两个nmos晶体管n2、n3构成了2t-nmos读取端口。

5、优选地,pmos晶体管p1的栅极与写入字线栏wwlb相连、源极连接写位线wbl、漏极连接nmos晶体管n2的栅极;nmos晶体管n1的漏极连接写位线wbl、源极连接nmos晶体管n2的栅极、栅极连接写入字线;nmos晶体管n2的源极接地、漏极连接nmos晶体管n3的源极;nmos晶体管n3的栅极连接读字线rwl、漏极连接读取比特线rbl。

6、优选地,利用dvs策略或drps策略优化所述低温准静态嵌入式dram的性能;或者利用dvs与drps的联合策略优化所述低温准静态嵌入式dram的性能。

7、优选地,所述低温准静态嵌入式dram的读取电路采用了带有附加参考电压的感应放大器。

8、本发明提出了利用cqs-edram实现高能效的cim应用的方法。基于精确的低温器件模型和工艺设计套件(pdk),本发明提出了一种低温四晶体管传输门增益单元(4t tggc)拓扑结构,通过充分利用其在降低泄漏和线传输延迟方面的优势,在低温下实现准静态存储操作。此外,本发明采用低温写入位线(wbl)偏置技术和专用的读出电路来优化读写操作的功耗。4kb cqs-edram芯片的实验数据显示,在4.2k的条件下,保留时间达到了66.50秒,并且保留时间分布更加均匀。准静态存储操作在执行resnet-18网络时,整体能效提升了2.63倍。此外,通过利用动态电压调节(dvs)和动态刷新周期调节(drps)技术,cqs-edram在可接受的数据错误率下实现了保留功耗的7.1%降低和动态功耗的13.6%降低。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184450.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表