一种闪存芯片高速测试中数据处理的方法和装置与流程

- 国知局

- 2024-07-31 20:01:23

本发明属于闪存芯片快速测试筛选,具体涉及一种闪存芯片高速测试中数据处理的方法和装置。

背景技术:

1、随着非易失存储芯片生产技术工艺的发展和应用需求的不断扩张,存储器在相同芯片面积上的存储密度越来越高,单位存储空间的成本越来越低。具体表现在二维平面上对晶体管进行微缩从而提高存储密度,每单元从存储1单元比特(slc)、2单元比特(mlc),到3/4单元比特(tlc/qlc),以获得更大容量,目前这种技术已接近达到极限。为了在维持性能的同时实现容量提升,科研人员研制新的3d nand技术,目前已经成为闪存的主流技术。在3d nand中,每单元仍然可以存储多个bit,包括slc、mlc、tlc、qlc几种类型,也称为3d-slc或3d-mlc等,堆叠层数目前已超过200层。但复杂的生产工艺和存储规则导致存储芯片的可靠性越来越分散,具体表现在存储单元上存在可擦除编程的耐久性次数和擦写时延的偏移等,以及在不同block中的原始误码分布不均衡等问题。

2、随着智能手机、笔记本电脑、个人移动存储、存储服务器市场上全闪存系列产品的推广,闪存芯片的使用量越来越大。作为存储产品中最重要的存储零器件,为了保证对用料的品质一致性、可靠性稳定的需求,生产厂家采用在生产前进行闪存芯片可靠性分级测试,包括对闪存进行坏块扫描、误码率测试、擦写时延等对一些性能参数进行存储、处理和基于一定规则的计算、定级。尤其是基于自动化系统的闪存测试高速分级技术。

3、现有通用的闪存等级筛选测试的实现方案是将测试参数存储到数据库里,然后上位机调用所需的参数数据值,进行初步处理(取整、转换、取平均等初步处理,再代入预设的等级计算公式进行计算得到最终等级结果),然后存储和输出。但这种方法存在如下问题,因为被测存储芯片的容量越来越大,测试过程中的数据量非常大(如单颗512gb的mlcnandflash,将全地址测试完的过程参数数据文件约为1500gb);受限于数据库的效率,上位机处理这部分工作的时候会影响接收其他测试进程,造成测试系统的不稳定和测试过程卡顿;对测试电脑的硬件配置要求也相对较高,在一定程度上增加了整体的测试成本。

技术实现思路

1、本发明要解决的技术问题是:提供一种闪存芯片高速测试中数据处理的方法和装置,用于高速自动化快速测试和筛选闪存芯片。

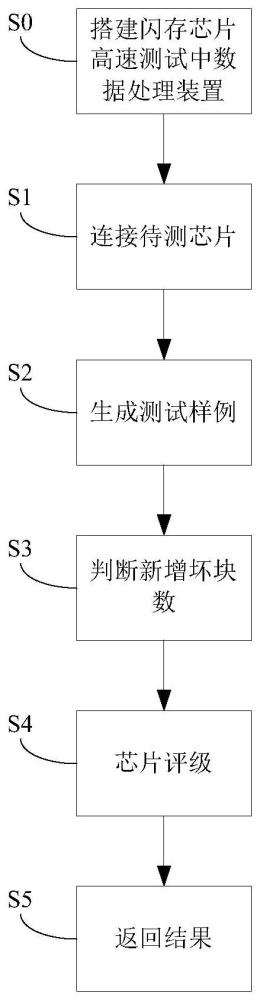

2、本发明为解决上述技术问题所采取的技术方案为:一种闪存芯片高速测试中数据处理的方法,包括以下步骤:

3、s0:搭建闪存芯片高速测试中数据处理装置,包括主控制单元和分控制单元;主控制单元以主从方式连接多个分控制单元;每个分控制单元连接多个待测芯片;分控制单元包括用于比对错误比特数的硬件加速模块、用于获取时间参数和电流参数的参数统计换算模块,以及用于分级待测芯片的等级筛选模块;硬件加速模块、参数统计换算模块和等级筛选模块均为硬件底层全过程处理模块;

4、s1:将待测芯片连接到分控制单元上,装置上电初始化,分控制单元适配待测芯片;

5、s2:分控制单元通过主控制单元接收上位机的工单命令,并生成指定的伪随机测试样例;

6、s3:分控制单元同时对每个适配过的待测芯片的指定存储地址进行对应的擦除、写入和读出操作,获取待测芯片的擦写时间和擦写电流测试数据;将读出测试样例与写入测试样例进行异或比对得到错误比特数,获取待测芯片的错误比特数测试数据;对获取到的测试数据进行大小比对和平均值计算;

7、s4:分控制单元通过步骤s3获取的测试数据、上位机下发的评级权重和预设的计算法则,按原始坏块数、新增坏块数、平均块擦除时间、平均页编程时间对待测芯片进行分级,并将分级结果返回给主控制单元;

8、s5:主控制单元再把分级结果返回给上位机,上位机将分级结果显示给用户。

9、按上述方案,待测芯片的测试数据包括原始坏块数、新增坏块数、擦除时间、编程时间以及时间和电流参数。

10、按上述方案,所述的步骤s3的具体步骤为:

11、s31:对适配过的待测芯片的指定存储地址即当前待测地址进行擦除操作,若成功则获取擦除时间、计算平均块擦除时间,并对当前待测地址进行编程;若擦除失败则偏移到下一个待测地址;

12、s32:若对当前待测地址进行编程成功则获取编程时间、计算平均页编程时间、对当前待测地址进行读取操作,并通过分控制单元的硬件异或器进行错误比特数比对;若编程失败则偏移到下一个待测地址;

13、s33:若对当前待测地址进行错误比特数比对成功则得到具体错误比特数,将具体错误比特数与上位机下发的阈值参数进行比较,并判断是否为新增坏块;若比对失败则偏移到下一个待测地址;

14、s34:判断当前待测地址是否为新增坏块完成后,偏移到下一个待测地址;若偏移成功或当前待测地址不为最后一个待测地址,则执行步骤s31;若偏移失败或当前待测地址为最后一个待测地址,则测试结束。

15、按上述方案,所述的步骤s4的具体步骤为:

16、s41:将上位机下发的评级权重r1乘以待测芯片的允许的最大原始坏块数n,得到待测芯片的原始坏块评级;以一个逻辑单元die为统计范围,允许的最大原始坏块数n为逻辑单元die内的总块数与有效块数nvb的差:

17、n=总块数die-nvb;

18、s42:将上位机下发的评级权重r2乘以待测芯片的允许的最大新增坏块数m,得到待测芯片的新增坏块评级;

19、s43:将上位机下发的评级权重r3乘以待测芯片的擦除时间典型值te,得到待测芯片的平均块擦除时间评级;

20、s44:将上位机下发的评级权重r4乘以待测芯片的编程时间典型值tp,得到待测芯片的平均页编程时间评级;

21、s45:在步骤s41到s44的评级结果中选出最劣项作为待测芯片的最终评级。

22、按上述方案,还包括以下步骤:当测试出现故障时,分控制单元通过主控制单元将故障信号上传给上位机并显示给用户。

23、一种闪存芯片高速测试中数据处理的装置,包括主控制单元和分控制单元;主控制单元以主从方式连接多个分控制单元,用于对分控制单元进行读写访问;每个分控制单元连接多个待测芯片,分控制单元用于向待测芯片发送测试指令并收集测试参数和结果;

24、分控制单元包括硬件加速模块,用于接收待测芯片工作状态的时间和电流数据,比对读取的数值与写入的样例,记录错误的比特个数;分控制单元包括参数统计换算模块,用于获取待测芯片工作状态的时间参数和电流参数;

25、分控制单元包括等级筛选模块,用于实时分类、计算、暂存收到的数据,并将计算得出的最终结果上传给上位机;

26、硬件加速模块、参数统计换算模块和等级筛选模块均在硬件底层处理全过程,并上传最终结果。

27、进一步的,还包括上位机,上位机通过包括串口和dma协议的方式连接主控制单元,用于向底板下发测试指令,接收并显示主控制单元返回的测试结果,或将测试结果上传给芯片自动分拣系统;主控制单元包括一个mcu;主控制单元通过iic口连接分控制单元,在分控制单元的接收端启动中断,用于随时接收主控制单元发来的指令。

28、进一步的,分控制单元包括应用层和驱动层;驱动层用于根据包括环境温度的条件动态调整硬件接口的时序;驱动层还包括驱动待测芯片的接口程序,用于根据待测芯片的型号调整相应的配置;应用层包括硬件加速模块和等级筛选模块。

29、进一步的,分控制单元还包括多通道测试控制器,用于对待测芯片的多通道同时下发命令;分控制单元还包括样例生成器,用于生成指定的伪随机测试样例;分控制单元还包括硬件异或器,用于将读出的数值与写入的样例值进行异或比对。

30、一种计算机存储介质,其内存储有可被计算机处理器执行的计算机程序,该计算机程序执行一种闪存芯片高速测试中数据处理的方法。

31、本发明的有益效果为:

32、1.本发明的一种闪存芯片高速测试中数据处理的方法和装置,通过统一下发上位机工单命令和接收测试结果,使用测试底板汇集、中转信号和测试数据,同时控制多个测试子板(即待测芯片颗粒)以提高测试效率;不经过数据库,直接由硬件进行多通道同时处理,边测试边对闪存测试过程的参数数据进行处理和计算分级,测试完毕直接输出测试等级,并直接传输给芯片自动分拣系统简洁的等级结果,实现了高速自动化快速测试和筛选闪存芯片的功能。

33、2.本发明使用硬件加速方案进行测试数据的处理和实时计算,比通用方案先存储再调用计算节省了数据库存取流程,数据处理时间更短、更快捷,占用测试主机资源更少,降低了测试成本,提高了测试效率。

34、3.本发明通过硬件底层处理全过程,只上传每一个待测芯片的最终等级结果,节省了常规系统中多种类大批量数据流传递、存储、计算的时间,减少了测试系统的信息传输压力,大幅度提高了测试速度,在大批量同时测试的时候系统稳定性更高。

35、4.本发明是一种面向量产的、大批量闪存快速等级筛选方案,通过快速无缝衔接实现批量化生产,特别适用于不需要对测试失败的存储芯片进行单个分析的、大批量快速测试的应用场景。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185070.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。