一种优化非易失SRAM单元及其控制方法

- 国知局

- 2024-07-31 20:02:11

本发明涉及集成电路设计,尤其是涉及一种优化非易失sram单元及其控制方法。

背景技术:

1、静态随机存取存储器(static random access memory,sram)是一种由半导体材料制成的随机存储器,具有超快的读写速度以及超高的耐久性。但sram具有易失特性,数据在电源关闭后立即丢失。随着半导体工艺节点的进步,晶体管漏电导致的静态功耗在整个片上系统的功耗占比越来越大。特别是在物联网等应用场景中,器件低工作频率、长时间待机的特点,使得静态功耗的问题更加凸显。

技术实现思路

1、本发明的目的就是为了克服传统的sram的易失特性,降低片上系统的功耗而提供的一种优化非易失sram单元及其控制方法。

2、本发明的目的可以通过以下技术方案来实现:

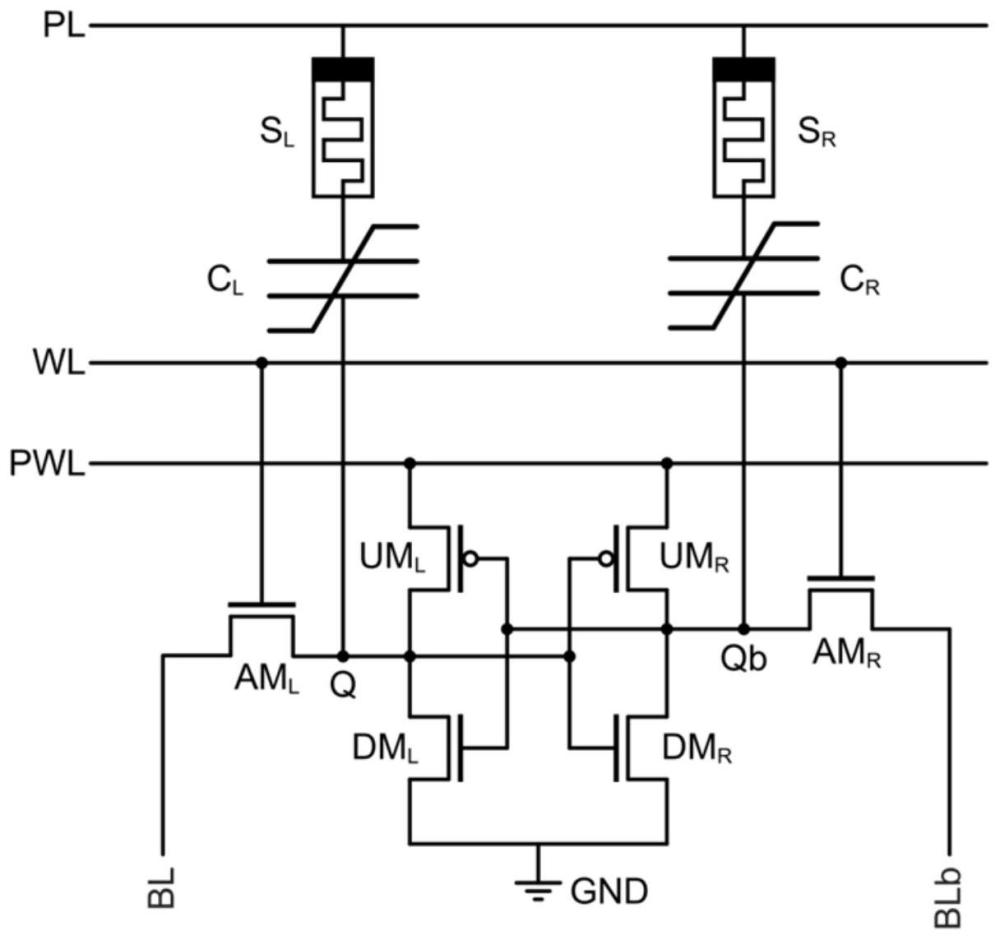

3、一种优化非易失sram单元,sram单元包括两个1s1c结构的非易失数据存储单元、两个晶体管单元、字线wl、第一位线bl、第二位线blb和电源电压线pwl,所述两个1s1c结构的非易失数据存储单元分别为第一单元和第二单元,所述第一单元由选通管sl和铁电电容cl串联构成,所述第二单元由选通管sr和铁电电容cr串联构成;

4、所述选通管sl的阳极和选通管sr的阳极均与控制线pl连接,选通管sl的阴极连接数据节点q,选通管sr的的阴极连接数据节点qb;

5、所述两个晶体管单元分别为第一晶体管单元和第二晶体管单元,所述第一晶体管单元包括晶体管uml、晶体管dml和存取晶体管aml,所述第二晶体管单元包括晶体管umr、晶体管dmr和存取晶体管amr;

6、晶体管uml和晶体管umr的源极连接电源电压线pwl;

7、晶体管uml的漏极、晶体管umr的栅极、晶体管dml的漏极、晶体管dmr的栅极和存取晶体管aml的源极均连接至数据节点q;

8、晶体管uml的栅极、晶体管umr的漏极、晶体管dml的栅极、晶体管dmr的漏极和存取晶体管amr的源极均连接至数据节点qb;

9、存取晶体管aml和存取晶体管amr的栅极均连接字线wl;存取晶体管aml的漏极连接第一位线bl,存取晶体管amr的漏极连接第二位线blb;

10、晶体管dml和晶体管dmr的源极连接地线gnd。

11、进一步地,晶体管uml和晶体管umr为p型晶体管,晶体管dml、存取晶体管aml、晶体管dmr和存取晶体管amr为n型晶体管。

12、进一步地,晶体管uml、晶体管umr、晶体管dml和晶体管dmr构成两个交叉耦合反相器。

13、本发明的另一方面,还提出一种基于上述的优化非易失sram单元的控制方法,方法包括数据恢复、数据存储、读数据和写数据,其中,

14、数据恢复具体为:将控制线pl电位上升至操作电压vdd,控制选通管sl和选通管sr导通,控制铁电电容cl和铁电电容cr的极化,其极化方向是否翻转由初始剩余极化强度决定,此时:

15、数据节点q恢复数据“0”,数据节点qb恢复数据“1”;或数据节点q恢复数据“1”,数据节点qb恢复数据“0”;

16、数据存储具体为:

17、电源电压线pwl保持高电位vdd,字线wl、第一位线bl、第二位线blb保持零电位;

18、调节控制线pl电位,然后:

19、将数据节点q中的“0”存入铁电电容cl,并将数据节点qb中的“1”存入铁电电容cr;或

20、将数据节点q中的“1”存入铁电电容cl,并将数据节点qb中的“0”存入铁电电容cr。

21、进一步地,数据节点q恢复数据“0”,数据节点qb恢复数据“1”的具体步骤为:

22、初始状态下铁电电容cl剩余极化为正、铁电电容cr剩余极化为负,电源电压线pwl电位为0后,调节控制线pl电位上升至操作电压vdd,调节控制线pl电位上升的过程中导通选通管sl和sr,铁电电容cl极化方向保持正向、铁电电容cr极化由负向翻转为正向,此时数据节点qb电位上升,高于数据节点q;

23、电源电压线pwl电位上升至操作电压vdd,sram单元电源恢复,晶体管uml、晶体管umr、晶体管dml和晶体管dmr构成的两个交叉耦合反相器将电位差放大,所述电位差为数据节点qb和数据节点q之间的电位差,电位差放大过程中关断选通管sr;

24、控制线pl电位下降至vdd/2,关断选通管sl,sram进入待机状态。

25、进一步地,数据节点q恢复数据“1”,数据节点qb恢复数据“0”的具体步骤为:

26、初始状态下铁电电容cl剩余极化为负、铁电电容cr剩余极化为正,电源电压线pwl电位为0后,调节控制线pl电位上升至操作电压vdd,调节控制线pl电位上升的过程中导通选通管sl和sr,铁电电容cl极化由负向翻转为正向、铁电电容cr极化方向保持正向,此时数据节点q电位上升,高于数据节点qb;

27、电源电压线pwl电位上升至操作电压vdd,sram单元电源恢复,晶体管uml、晶体管umr、晶体管dml和晶体管dmr构成的两个交叉耦合反相器将电位差放大,所述电位差为数据节点qb和数据节点q之间的电位差,电位差放大过程中关断选通管sl;

28、控制线pl电位下降至vdd/2,关断选通管sr,sram进入待机状态。

29、进一步地,调节控制线pl电位,然后将数据节点q中的“0”存入铁电电容cl,并将数据节点qb中的“1”存入铁电电容cr具体步骤为:

30、数据节点q中数据为“0”,qb中的数据为“1”的情况下,待机状态下控制线pl电位处于vdd/2,调节控制线pl电位上升至高电位vdd,此时第一单元两极电位差为vdd,第二单元的两极电位差为0,选通管sl导通,铁电电容cl极化翻转、数据节点q中的“0”数据存入铁电电容cl;

31、调节控制线pl电位,由高电位vdd下降至零电位,第一单元两极电位差下降为0,并关断选通管sl,第二单元两极电位差下降为-vdd,导通选通管sr,铁电电容cr极化翻转,数据节点qb中的“1”存入铁电电容cr。

32、进一步地,调节控制线pl电位,然后将数据节点q中的“1”存入铁电电容cl,并将数据节点qb中的“0”存入铁电电容cr具体步骤为:

33、数据节点q中数据为“1”,qb中的数据为“0”的情况下,待机状态下控制线pl电位处于vdd/2,调节控制线pl电位上升至高电位vdd,此时第一单元两极电位差为0,第二单元的两极电位差为vdd,选通管sr导通,铁电电容cr极化翻转、数据节点qb中的“0”存入铁电电容cr;

34、调节控制线pl电位,由高电位vdd下降至零电位,第二单元两极电位差下降为0,并关断选通管sr,第一单元两极电位差下降为-vdd,导通选通管sl,铁电电容cl极化翻转,数据节点q中的“1”存入铁电电容cl。

35、进一步地,所述读数据具体包括:读“1”操作和读“0”操作,

36、读“0”操作具体为:

37、初始状态下q中数据为“0”,qb中数据为“1”,将第一位线bl和第二位线blb预充至vdd,之后将字线wl电位上升至vdd,使存取晶体管aml和存取晶体管amr打开,由于第一位线bl电位低于数据节点q电位,第一位线bl端电荷流入数据节点q,导致第一位线bl电位下降,而第二位线blb和数据节点qb电位相同,无电荷移动,由此导致第一位线bl电位小于第二位线blb电位,第一位线bl电位输出为“0”;

38、读“1”操作具体为:

39、初始状态下q中数据为“1”,qb中数据为“0”,将第一位线bl和第二位线blb预充至vdd,之后将字线wl电位上升至vdd,使存取晶体管aml和存取晶体管amr打开,由于第二位线blb电位低于数据节点qb电位,第二位线blb端电荷流入数据节点qb,导致第二位线blb端电位下降,而第一位线bl和数据节点q电位相同,无电荷移动,由此第一位线bl电位大于第二位线blb电位,第一位线bl电位输出为“1”。

40、进一步地,所述写数据具体包括:写“1”操作和写“0”操作,

41、写“1”操作具体为:

42、初始状态下数据节点q和qb电位分别为0和vdd,将第一位线bl和第二位线blb电位分别设定为vdd和0,之后将wl电位上升至vdd,使存取晶体管aml和存取晶体管amr打开,数据节点q电位由0翻转为vdd,数据节点qb电位由vdd翻转为0,实现数据写入“1”,最后将wl恢复为零电位,aml和amr关闭;

43、写“0”操作具体为:

44、初始状态下数据节点q和qb电位分别为vdd和0,将第一位线bl和第二位线blb电位分别设定为0和vdd,之后将wl电位上升至vdd,使存取晶体管aml和存取晶体管amr打开,数据节点q电位由vdd翻转为0,数据节点qb电位由0翻转为vdd,实现数据写入“0”,最后将wl恢复为零电位,aml和amr关闭。与现有技术相比,本发明具有以下有益效果:

45、基于传统易失性sram单元,本发明通过增加两个选通管和铁电电容构成的1s1c非易失存储单元,使sram具有断电保持数据和上电恢复数据的非易失特性,扩展了sram器件的应用场景,有效降低了器件的静态功耗。由于选通管s的开关特性,在sram的读写操作时保持1s1c单元关闭,阻断了与数据节点的连接,极大程度降低了1s1c单元对sram读写性能的干扰;同时根据电阻分压,电位差集中于选通管s两端,有效缓解了铁电电容c中持续电应力对材料的介电损耗。

46、本发明的双1s1c的互补排布提高了数据存储和恢复的准确率,增强了对制备工艺的容错率。选通管在sram读写操作过程中阻断了铁电电容与数据节点的连接,减小了非易失存储单元对sram常规操作的干扰,同时有效降低了器件功耗,并减少了操作过程中持续电应力对铁电电容的介电损耗,提高了非易失性sram单元寿命。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185141.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。