具有掩模写入功能性的锁存器阵列的制作方法

- 国知局

- 2024-07-31 20:17:14

本公开的各方面整体涉及存储器电路,并且具体地涉及具有掩模写入功能性的锁存器阵列。

背景技术:

1、静态随机存取存储器(sram)和动态随机存取存储器(dram)通常在电路中采用,诸如包括片上系统(soc)型ic的集成电路(ic)。sram和dram存储器电路通常在相对高的存储器电压域下操作以确保满足数据传递裕度。也存储数据的锁存器阵列正变得越来越流行,因为其通常在相对低的逻辑电压域下操作,这使得其与sram和dram相比是更功率有效的。因此,在诸如ic和soc的电路的设计中,已经存在通过锁存器阵列交换或替换sram和dram的推动力。

技术实现思路

1、以下内容呈现了对一个或多个具体实施的简化概括,以便提供对此类具体实施的基本的理解。该概括不是对全部设想的具体实施的详尽概述,并且不旨在标识全部具体实施的关键或重要元素,也不旨在描绘任何或全部具体实施的范围。其唯一的目的是以简化的形式呈现一个或多个具体实施的一些概念,作为随后呈现的更详细的描述的序言。

2、wo 2023/136925a1

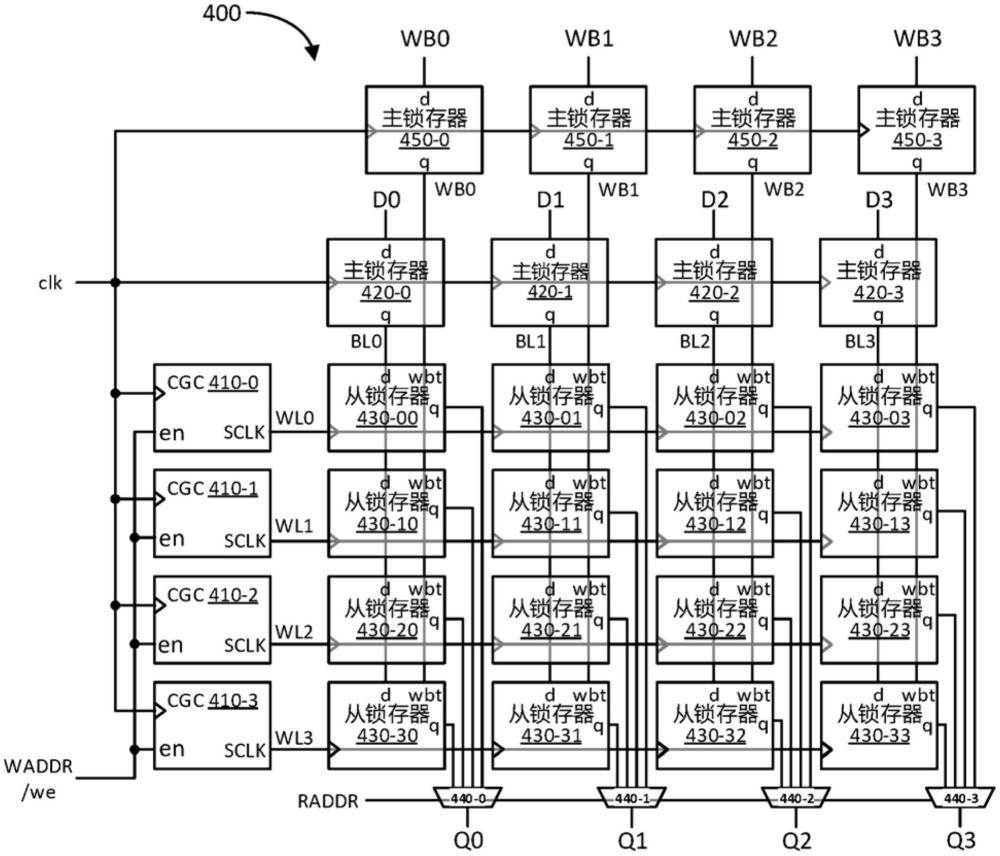

3、本公开的一方面涉及一种锁存器阵列。该锁存器阵列包括:第一组主锁存器,该第一组主锁存器包括被配置为接收主时钟的第一组时钟输入、被配置为接收第一组数据的第一组数据输入、以及分别耦合到一组位线的第一组数据输出;第二组主锁存器,该第二组主锁存器包括被配置为接收该主时钟的第二组时钟输入、被配置为接收一组写入位信号的第一组写入位输入、以及分别耦合到一组写入位线的一组写入位输出;和从锁存器阵列,该从锁存器阵列被布置成列和行,其中该阵列的该列中的该从锁存器包括耦合到该组位线的第二组数据输入、以及分别耦合到该组写入位线的第二组写入位输入。

4、本公开的另一方面涉及一种方法。该方法包括:向一组从锁存器中的目标从锁存器提供已解除断言的写入位信号;分别向该组从锁存器提供第一组数据信号;向该组从锁存器提供第一从时钟以分别基于该第一组数据信号中的一者或多者将数据写入到该组从锁存器中的一者或多者;以及在该从时钟正分别基于该第一组数据信号中的该一者或多者来致使将数据写入到该组从锁存器中的该一者或多者时,响应于该已解除断言的写入位信号而操作该目标从锁存器以保留先前存储的数据。

5、本公开的另一方面涉及一种装置。该装置包括:用于向一组从锁存器中的目标从锁存器提供已解除断言的写入位信号的构件;用于分别向该组从锁存器提供第一组数据信号的构件;用于向该组从锁存器提供第一从时钟以分别基于该第一组数据信号中的一者或多者将数据写入到该组从锁存器中的一者或多者的构件;和用于在该第一从时钟正分别基于该第一组数据信号中的该一者或多者来致使将数据写入到该组从锁存器中的该一者或多者时,响应于该已解除断言的写入位信号而操作该目标从锁存器以保留先前存储的数据的构件。

6、本公开的另一方面涉及一种无线通信设备。该无线通信设备包括:至少一个天线;收发器,所述收发器耦合到所述至少一个天线;一个或多个信号处理核,所述一个或多个信号处理核耦合到所述收发器;和锁存器阵列,该锁存器阵列耦合到该一个或多个信号处理核,其中该锁存器阵列包括:第一组主锁存器,该第一组主锁存器包括被配置为接收主时钟的第一组时钟输入、被配置为分别接收一组数据的第一组数据输入、以及分别耦合到一组位线的第一组数据输出;第二组主锁存器,该第二组主锁存器包wo 2023/136925a1

7、括被配置为接收该主时钟的第二组时钟输入、被配置为接收一组写入位信号的第一组写入位输入、以及分别耦合到一组写入位线的一组写入位输出;和从锁存器阵列,该从锁存器阵列被布置成列和行,其中该阵列的该列中的该从锁存器包括耦合到该组位线的第二组数据输入、以及分别耦合到该组写入位线的第二组写入位输入。

8、为了实现前述目的和相关目的,一个或多个具体实施包括下文中充分地描述的以及在权利要求中具体指出的特征。以下描述和所附插图详细阐述了这一个或多个具体实施的某些例示性方面。然而,这些方面仅仅是指示了可采用各个具体实施的原理的各种方式中的若干种,并且说明书具体实施旨在包括所有此类方面及其等效方案。

技术特征:1.一种锁存器阵列,包括:

2.根据权利要求1所述的锁存器阵列,还包括一组时钟门控电路,所述一组时钟门控电路包括被配置为接收所述主时钟的第三组时钟输入、以及耦合到一组字线的一组时钟输出,其中所述阵列的所述行中的所述从锁存器包括分别耦合到所述一组字线的第四组时钟输入。

3.根据权利要求2所述的锁存器阵列,其中所述阵列的每个从锁存器包括:

4.根据权利要求2所述的锁存器阵列,其中所述阵列的每个从锁存器包括:

5.根据权利要求4所述的锁存器阵列,其中所述第一fet、所述第二fet、所述第五fet和所述第六fet分别是p沟道金属氧化物半导体场效应晶体管(pmos fet),并且所述第三fet、所述第四fet、所述第七fet和所述第八fet分别是n沟道金属氧化物半导体场效应晶体管(nmos fet)。

6.根据权利要求2所述的锁存器阵列,其中所述阵列的每个从锁存器包括:

7.根据权利要求2所述的锁存器阵列,其中所述阵列的每个从锁存器包括:

8.根据权利要求7所述的锁存器阵列,其中所述第一fet、所述第二fet、所述第三fet、所述第七fet和所述第一对并联fet分别包括p沟道金属氧化物半导体场效应晶体管(pmosfet),并且其中所述第四fet、所述第五fet、所述第六fet、所述第八fet和所述第二对并联fet分别包括n沟道金属氧化物半导体场效应晶体管(nmos fet)。

9.根据权利要求2所述的锁存器阵列,其中所述阵列的每个从锁存器包括:

10.根据权利要求2所述的锁存器阵列,其中所述阵列的每个从锁存器包括:

11.根据权利要求10所述的锁存器阵列,其中所述第一fet、所述第二fet、所述第五fet和所述第六fet分别包括p沟道金属氧化物半导体场效应晶体管(pmos fet),并且其中所述第三fet、所述第四fet、所述第七fet和所述第八fet分别包括n沟道金属氧化物半导体场效应晶体管(nmos fet)。

12.根据权利要求2所述的锁存器阵列,其中所述一组时钟门控电路包括被配置为接收写入地址的一组启用输入。

13.根据权利要求1所述的锁存器阵列,还包括一组多路复用器,所述一组多路复用器包括分别耦合到所述各列从锁存器的第二组数据输出的各组输入、被配置为接收读取地址的一组选择输入、以及被配置为分别产生第二组数据的第三组数据输出。

14.一种方法,包括:

15.根据权利要求14所述的方法,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中操作所述目标从锁存器包括响应于所述已解除断言的写入位信号而门控所述第一从时钟使其不被施加到所述数据门控电路和所述数据锁存电路。

16.根据权利要求14所述的方法,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中操作所述目标从锁存器包括响应于所述已解除断言的写入位信号而将所述数据门控电路维持在门控状态并且将所述数据锁存电路维持在闭合状态。

17.根据权利要求14所述的方法,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中操作所述目标从锁存器包括响应于所述已解除断言的写入位信号和所述第一从时钟而经由所述数据门控电路将所述先前存储的数据从数据输出反馈到所述数据锁存电路的数据输入。

18.根据权利要求14所述的方法,还包括:

19.根据权利要求18所述的方法,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中操作所述目标从锁存器以存储所述数据包括响应于所述已断言的写入位信号而将所述第二从时钟传递到所述数据门控电路和所述数据锁存电路。

20.根据权利要求18所述的方法,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中操作所述目标从锁存器以存储所述数据包括响应于所述已断言的写入位信号和所述第二从时钟而将所述数据门控电路设置在非门控状态并且将所述数据锁存电路设置在打开状态。

21.根据权利要求18所述的方法,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中操作所述目标从锁存器以存储所述数据wo 2023/136925a1

22.一种装置,包括:

23.根据权利要求22所述的装置,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中用于操作所述目标从锁存器的所述构件包括用于响应于所述已解除断言的写入位信号而门控所述第一从时钟使其不被施加到所述数据门控电路和所述数据锁存电路的构件。

24.根据权利要求22所述的装置,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中用于操作所述目标从锁存器的所述构件包括用于响应于所述已解除断言的写入位信号而将所述数据门控电路维持在门控状态并且将所述数据锁存电路维持在闭合状态的构件。

25.根据权利要求22所述的装置,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中用于操作所述目标从锁存器的构件包括用于响应于所述已解除断言的写入位信号和所述第一从时钟而经由所述数据门控电路将所述先前存储的数据从数据输出反馈到所述数据锁存电路的数据输入的构件。

26.根据权利要求22所述的装置,还包括:

27.根据权利要求26所述的装置,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中用于操作所述目标从锁存器以存储所述数据的所述构件包括响应于所述已断言的写入位信号而将所述第二从时钟传递到所述数据门控电路和所述数据锁存电路。

28.根据权利要求26所述的装置,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中用于操作所述目标从锁存器以存储所述数据的所述构件包括用于响应于所述已断言的写入位信号和所述第二从时钟而将所述数据门控电路设置在非门控状态并且将所述数据锁存电路设置在打开状态的构件。

29.根据权利要求26所述的装置,其中所述目标从锁存器包括数据门控电路和数据锁存电路,其中用于操作所述目标从锁存器以存储所述数据的所述构件包括用于响应于所述已断言的写入位信号而将所述第二组数据信号中的所述对应一者传递到所述数据门控电路的构件。

30.一种无线通信设备,所述无线通信设备包括:

技术总结具有掩模写入功能性的锁存器阵列包括:第一组主锁存器,该第一组主锁存器包括被配置为接收主时钟的第一组时钟输入、被配置为接收第一组数据的第一组数据输入、以及分别耦合到一组位线的第一组数据输出;第二组主锁存器,该第二组主锁存器包括被配置为接收该主时钟的第二组时钟输入、被配置为接收一组写入位信号的第一组写入位输入、以及分别耦合到一组写入位线的一组写入位输出;和从锁存器阵列,其中该阵列的该列中的该从锁存器包括耦合到该组位线的第二组数据输入、以及分别耦合到该组写入位线的第二组写入位输入。技术研发人员:李睿,鲁德,V·纳拉亚南受保护的技术使用者:高通股份有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/185697.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表