RF相邻堆叠的可变宽度的制作方法

- 国知局

- 2024-08-02 15:08:19

本公开内容涉及集成电路设备,并且更具体地涉及用于在存在相邻堆叠时处理rf开关堆叠中的电压分布的方法和装置。

背景技术:

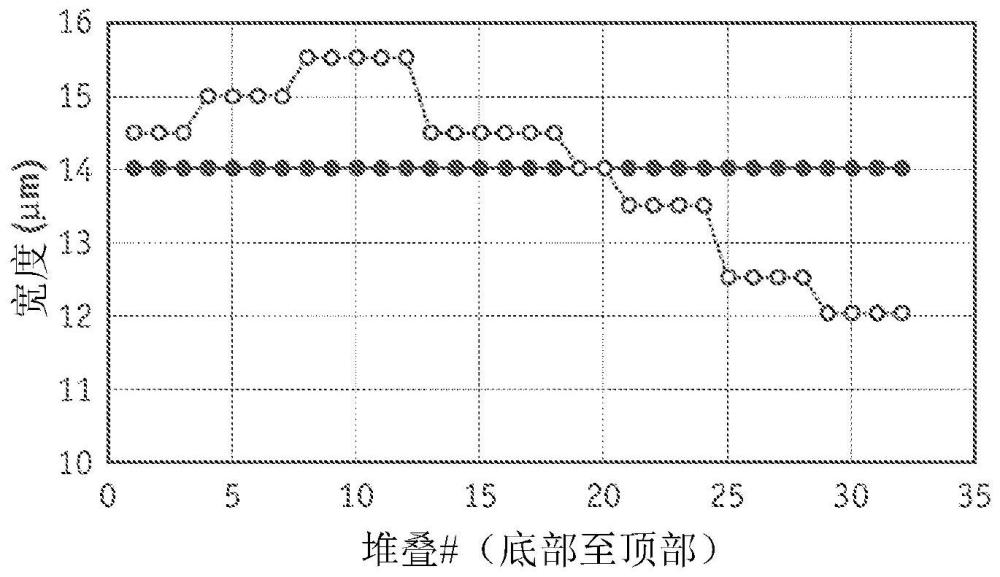

1、如图1所示,开关堆叠(诸如其全部内容通过引用并入本文的us 6,804,502中所示的开关堆叠)中的fet两端的电压分布是不均匀的。顶部fet(图中的fet#32)通常比堆叠中的任何其他fet承受更大比例的总施加开关电压。因此,这样的承受压力最大的fet具有首先失效的趋势,从而致使其他fet以类似多米诺骨牌效应的方式失效。这样的电压分布不均等通常由寄生电容引起。解决此问题的已知方法是使堆叠的晶体管从底部至顶部逐渐变大,以代替或附加地在堆叠的晶体管之间增加离散电容。关于fet开关堆叠中的电容补偿,可以参考例如pct公开申请wo 2008/133621,该pct公开申请的全部内容通过引用并入本文。

技术实现思路

1、本申请描述了用于在存在相邻堆叠时处理rf开关堆叠中的电压分布的新的装置和方法,如在所附图中详细描述的。

2、根据第一方面,提供了一种集成电路,包括:第一堆叠,其包括从第一堆叠的底部fet至第一堆叠的顶部fet的堆叠式fet;以及第二堆叠,其包括从第二开关堆叠的底部fet至第二堆叠的顶部fet的堆叠式fet,第二堆叠与第一堆叠相邻,其中,第一堆叠或第二堆叠的每个fet具有在第一堆叠或第二堆叠的顶部至底部或底部至顶部方向上延伸的fet宽度,并且第一堆叠的顶部fet的fet宽度小于第一堆叠的底部fet的fet宽度。

3、根据第二方面,提供了一种集成电路,包括:第一堆叠,其包括从第一堆叠的底部fet至第一堆叠的顶部fet的堆叠式fet;以及第二堆叠,其包括从第二开关堆叠的底部fet至第二堆叠的顶部fet的堆叠式fet,第二堆叠与第一堆叠相邻,其中,第一堆叠或第二堆叠的每个fet具有在第一堆叠或第二堆叠的顶部至底部或底部至顶部方向上延伸的fet宽度,并且第一堆叠的顶部fet的fet宽度小于第一堆叠的至少第一下部fet的fet宽度。

4、根据第三方面,提供了一种处理fet的堆叠中电压不平衡的方法,包括:形成fet的堆叠,所述堆叠包括从堆叠的底部fet至堆叠的顶部fet的堆叠式fet,堆叠的每个fet具有在堆叠的顶部至底部方向上延伸的fet宽度,其中,fet的堆叠的顶部fet具有比fet的堆叠的底部fet的fet宽度小的fet宽度;以及将fet的堆叠靠近同一集成电路中的相邻fet堆叠放置。

5、在附图和以下描述中阐述了本发明的一个或更多个实施方式的细节。本发明的其他特征、目的和优点将根据说明书和附图以及权利要求书变得明显。

技术特征:1.一种集成电路(ic),包括

2.根据权利要求1所述的ic,其中

3.根据权利要求2所述的ic,其中

4.根据权利要求2所述的ic,其中

5.根据权利要求4所述的ic,其中

6.根据权利要求4或5所述的ic,其中

7.根据权利要求6所述的ic,其中

8.一种rf开关电路,包括根据权利要求1所述的ic,所述第一堆叠是第一开关堆叠,并且所述第二堆叠是第二开关堆叠。

9.一种集成电路(ic),包括

10.根据权利要求9所述的ic,其中

11.根据权利要求9所述的ic,其中

12.根据权利要求11所述的ic,其中

13.根据权利要求9所述的ic,其中

14.根据权利要求13所述的ic,其中

15.一种处理fet的堆叠中的电压不平衡的方法,包括:

16.根据权利要求15所述的方法,其中,所述放置在所述形成发生的同时发生。

17.根据权利要求15所述的方法,其中

18.根据权利要求17所述的方法,其中

19.根据权利要求17所述的方法,其中

20.根据权利要求19所述的方法,其中

技术总结描述了用于在存在相邻FET开关堆叠时制造FET开关堆叠的设备和方法。FET开关堆叠被设计或制造成使得至少其顶部FET具有比其底部FET的宽度小的宽度。描述了其他电压处理配置和宽度的分布。技术研发人员:沙希·沙马尔,马特·阿莉森受保护的技术使用者:派赛公司技术研发日:技术公布日:2024/7/15本文地址:https://www.jishuxx.com/zhuanli/20240801/245078.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表