降低SRAM泄漏电流的方法与流程

- 国知局

- 2024-08-02 15:40:45

本发明涉及半导体,特别是涉及一种降低sram泄漏电流的方法。

背景技术:

1、sram(随机静态存储器)的泄漏电流对整个芯片的泄漏功耗起着决定性的作用。因此降低sram的泄漏电流已经成为集成电路设计中必须要考虑的关键问题。

2、增加栅厚度可以有效降低sram泄漏电流,p管与n管相比漏电流小一个数量级以上,因此通过增加n管栅氧化层厚度可以实现漏电改善。

3、为解决上述问题,需要提出一种新型的降低sram泄漏电流的方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种降低sram泄漏电流的方法,用于解决现有技术中需要一种新方法来增加n管栅氧化层厚度以实现漏电改善的问题。

2、为实现上述目的及其他相关目的,本发明提供一种降低sram泄漏电流的方法,包括:

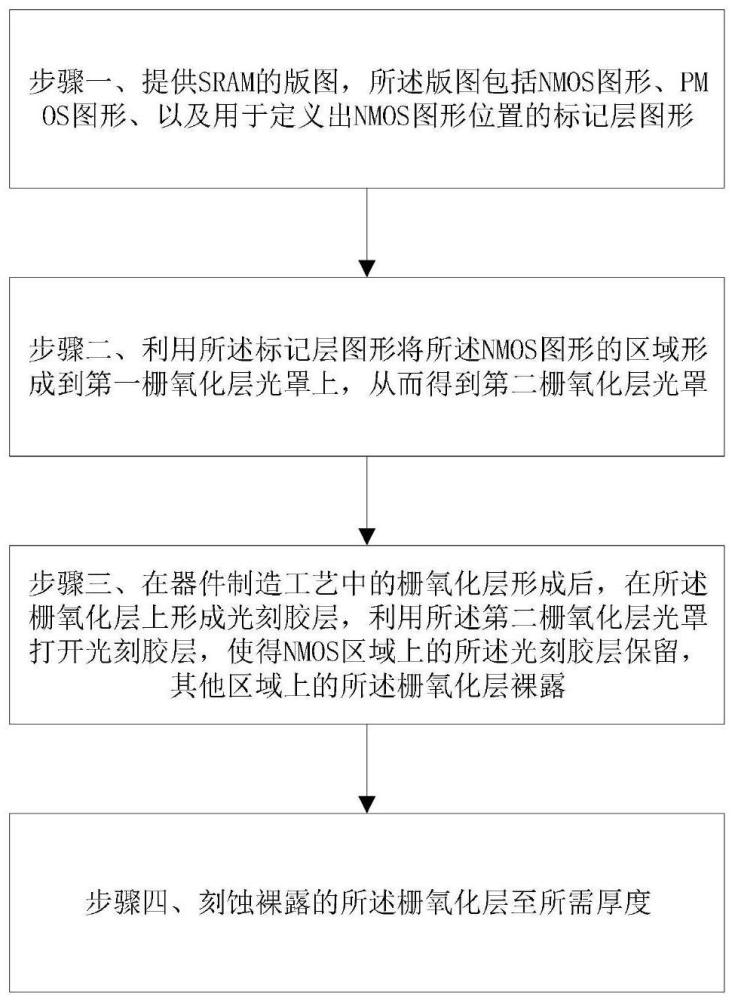

3、步骤一、提供sram的版图,所述版图包括nmos图形、pmos图形、以及用于定义出nmos图形位置的标记层图形;

4、步骤二、利用所述标记层图形将所述nmos图形的区域形成到第一栅氧化层光罩上,从而得到第二栅氧化层光罩;

5、步骤三、在器件制造工艺中的栅氧化层形成后,在所述栅氧化层上形成光刻胶层,利用所述第二栅氧化层光罩打开光刻胶层,使得nmos区域上的所述光刻胶层保留,其他区域上的所述栅氧化层裸露;

6、步骤四、刻蚀裸露的所述栅氧化层至所需厚度。

7、优选地,步骤一中的所述sram的版图用于任意数量晶体管sram的制造。

8、优选地,步骤二中利用掩膜制具表将所述nmos图形的区域形成到第一栅氧化层光罩上。

9、优选地,步骤三中的所述栅氧化层形成于衬底上。

10、优选地,步骤三中的所述衬底包括块状半导体衬底或绝缘体上硅(soi)衬底。

11、优选地,步骤三中利用热氧化的方法形成所述栅氧化层。

12、优选地,步骤四中的所述刻蚀的方法为干法刻蚀。

13、如上所述,本发明的降低sram泄漏电流的方法,具有以下有益效果:

14、本发明无需修改原始数据,无需新增光罩,即可通过栅氧化层光罩实现nmos管区域的栅氧化层厚度调整。

技术特征:1.一种降低sram泄漏电流的方法,其特征在于,至少包括:

2.根据权利要求1所述的降低sram泄漏电流的方法,其特征在于:步骤一中的所述sram的版图用于任意数量晶体管sram的制造。

3.根据权利要求2所述的降低sram泄漏电流的方法,其特征在于:步骤二中利用掩膜制具表将所述nmos图形的区域形成到第一栅氧化层光罩上。

4.根据权利要求1所述的降低sram泄漏电流的方法,其特征在于:步骤三中的所述栅氧化层形成于衬底上。

5.根据权利要求4所述的降低sram泄漏电流的方法,其特征在于:步骤三中的所述衬底包括块状半导体衬底或绝缘体上硅(soi)衬底。

6.根据权利要求1所述的降低sram泄漏电流的方法,其特征在于:步骤三中利用热氧化的方法形成所述栅氧化层。

7.根据权利要求1所述的降低sram泄漏电流的方法,其特征在于:步骤四中的所述刻蚀的方法为干法刻蚀。

技术总结本发明提供一种降低SRAM泄漏电流的方法,提供SRAM的版图,版图包括NMOS图形、PMOS图形、以及用于定义出NMOS图形位置的标记层图形;利用标记层图形将NMOS图形的区域形成到第一栅氧化层光罩上,从而得到第二栅氧化层光罩;在器件制造工艺中的栅氧化层形成后,在栅氧化层上形成光刻胶层,利用第二栅氧化层光罩打开光刻胶层,使得NMOS区域上的光刻胶层保留,其他区域上的栅氧化层裸露;刻蚀裸露的栅氧化层至所需厚度。本发明无需修改原始数据,无需新增光罩,即可通过栅氧化层光罩实现NMOS管区域的栅氧化层厚度调整。技术研发人员:曹玉荣,田志受保护的技术使用者:上海华力集成电路制造有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240801/247196.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表