一种用于存储芯片FT测试机的校准板卡方法与流程

- 国知局

- 2024-08-05 12:11:18

本发明涉及芯片测试,具体涉及一种用于存储芯片ft测试机的校准板卡方法。

背景技术:

1、存储芯片具有众多数字引脚的特性,这导致在存储芯片ft(final test,最终测试)测试设备中需要使用到大量的数字信号板卡。从数字信号板卡到待测芯片接口板的整条链路中,板卡内部走线、不同连接器与线束差异等因素将会导致所使用到的数字板卡中的不同通道差异化显著。这种通道差异化直观的体现在驱动器到测试端的时间差异上,便会影响到测试的结果与良率。所以我们不得不采用适当的方法将不同通道之间这种时间的差异进行补偿,这就是所有自动测试设备中所需要做的交变信号校准,下面称之为ac校准。

2、目前大部分自动测试设备所采用的ac校准方案存在以下几点问题:

3、传统ac校准方案中的结构单一,是一整块的校准板与机台进行连接,无法在相同机台不同配置下重复使用,具有较差的兼容性,在同公司同系列机台中使用也不得不进行板卡的重新设计与更换,这无疑增加了设计的成本。

4、传统ac校准方案中,使用到的信号发生器成本高昂,使用不便;只对单一的上升沿或者下降沿进行校准,并且大部分校准方案中在面对多板卡多通道校准时间过长。

5、传统ac校准方案中的功能单一,仅针对数字板卡进行校准,但面对机台中电源板卡或者其他功能项需要的额外检查时便不得不增加其他的板卡来实现对应的功能,传统ac校准板卡中没有增加额外的可以扩展的功能选择,这无形中增加了额外设计板卡的工作量与时间成本。

技术实现思路

1、本发明的目的在于提供一种用于存储芯片ft测试机的校准板卡方法,解决以下技术问题:

2、传统ac校准方案中的结构和功能较为单一,成本高昂且面对多板卡多通道校准时间过长,且仅针对数字板卡进行校准,面对机台中电源板卡或者其他功能项需要的额外检查时便不得不增加其他的板卡来实现对应的功能。

3、本发明的目的可以通过以下技术方案实现:

4、一种用于存储芯片ft测试机的校准板卡方法,基于测试机台中的母板、校准板卡、数字板卡、电源板卡,包括:

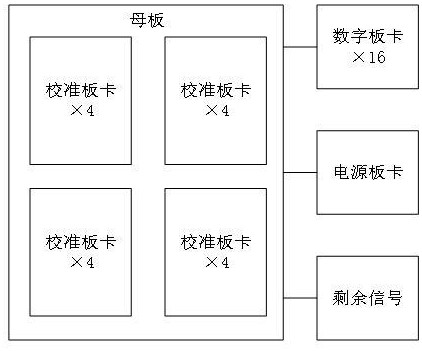

5、所述测试机台分4块区域,每块区域包括8块数字板卡和1块母板,所述母板作为数字、电源等板卡与校准板的转接板,用于信号汇总,每块区域的母板与4块校准板卡连接,每个校准板卡对应2个数字板卡,所述校准板卡用于对数字板卡进行ac校准;

6、每个校准板卡包括8个连接器j1-j8和1个fpga组成,校准板卡中的连接器与母板通过线束连接,将数字板卡与电源板卡与校准板卡联通,每4块连接器对应1块数字板卡的通道,电源板卡和剩余的信号通道分别与每个连接器均匀连接,所述fpga用于发出校准与检查的控制命令;

7、对于任一校准板卡对应的两块数字板卡,校准板卡使用spi总线对gpio进行编程,通过switch的切换设定其中一块数字板卡为master板卡,另一块数字板卡设定为slaver板卡,对master板卡和slaver板卡进行同步校准;

8、每块数字板卡内部设有tg模块,所述tg模板用于生成校准时需要的数字信号,通过pe芯片传输给校准板卡中的fpga进行采集,fpga将数字信号与校准参考时钟信号对比,对数字信号进行修正;

9、校准板卡内部的fpga发送所需要的数字信号进行strobe,传输到数字板卡内部进行信号采集,与参考时钟信号对比,对仍然有误差的数字通道再次补偿,完成校准。

10、作为本发明进一步的方案:校准参考时钟波形采用20ns的周期,数字板卡内部的tg模块在驱动20ns的rz波形给所有的数字通道后,校准板使用校准参考时钟进行采集,以参考点为基准修正所有的数字信号时钟偏差。

11、作为本发明进一步的方案:所述参考信号的校准周期设置为20ns,校准板发送相同20ns的rz波形后,以参考时钟为基准进行strobe,以参考点为基准,补偿所有仍有误差的数字通道。

12、作为本发明进一步的方案:所述校准板卡还用于对校准完成后的数字信号进行检查、对电源板卡中的通道进行通断检查、对整个测试机台的power进行检查。

13、作为本发明进一步的方案:对校准完成后的数字信号进行检查的过程为:

14、当数字信号被修正后,数字板卡中的tg模块再次生成任意被测信号通过pe芯片被校准板中fpga采集,将参考信号的上升沿和下降沿与被测信号的上升沿和下降沿进行比对,将对比结果通过映射关系呈现至用户界面;

15、当strobe时,校准板中的fpga输出任意被测信号被数字板卡采集,将参考信号的上升沿与被测信号的上升沿进行对比,将对比结果通过映射关系呈现至用户界面。

16、作为本发明进一步的方案:所述映射关系为:

17、低电平采用预设第一符号表示,高电平采用预设第二符号表示,当被测信号的上升沿或者下降沿在参考信号范围内时,用户界面中的字体为白色;当被测信号的上升沿或者下降沿不在参考信号范围内时,用户界面中的字体变成红色,并且被统计在fail的通道数中。

18、作为本发明进一步的方案:所述通断检查为:

19、将来自母板中同一块电源板卡的force信号和sense信号短接在一起通过一个10欧姆电阻接地,通过fpga控制电源板卡中的继电器的切换来判断整条路径的通断,输出结果呈现至用户界面。

20、作为本发明进一步的方案:power检查为:

21、user power的信号到校准板之后通过模数转换将转换后的数字信号发送给fpga,判断user power的信号是否出现问题,判断的结果呈现至用户界面

22、本发明的有益效果:

23、(1)本发明通过数字板卡与校准板内部的fpga输出与采集信号,并对采集到的信号进行诊断;单块校准板卡同时连接两块数字板卡,并将两块数字板卡划分为master和slaver,使用spi总线的方法确认master和slaver板卡后,使用drive与strobe的方法对来自数字板卡与校准板的信号进行上升沿与下降沿的校准,使得校准结果更加准确;

24、(2)本发明中摒弃了一整块的校准板结构,而是做出较为创新的可拼接结构,可单板使用给一块或者两块数字板卡进行校准;可多板卡组合使用对多块数字板卡进行校准;可用于同一个机台但是使用不同数字板卡配置的情况下任意组合使用;可用于同系列不同尺寸机台中组合使用。

技术特征:1.一种用于存储芯片ft测试机的校准板卡方法,其特征在于,基于测试机台中的母板、校准板卡、数字板卡、电源板卡,包括:

2.根据权利要求1所述的一种用于存储芯片ft测试机的校准板卡方法,其特征在于,所述校准参考时钟波形采用20ns的周期,数字板卡内部的tg模块在驱动20ns的rz波形给所有的数字通道后,校准板使用校准参考时钟进行采集,以参考点为基准修正所有的数字信号时钟偏差。

3.根据权利要求1所述的一种用于存储芯片ft测试机的校准板卡方法,其特征在于,所述参考信号的校准周期设置为20ns,校准板发送相同20ns的rz波形后,以参考时钟为基准进行strobe,以参考点为基准,补偿所有仍有误差的数字通道。

4.根据权利要求1所述的一种用于存储芯片ft测试机的校准板卡方法,其特征在于,所述校准板卡还用于对校准完成后的数字信号进行检查、对电源板卡中的通道进行通断检查、对整个测试机台的power进行检查。

5.根据权利要求4所述的一种用于存储芯片ft测试机的校准板卡方法,其特征在于,对校准完成后的数字信号进行检查的过程为:

6.根据权利要求5所述的一种用于存储芯片ft测试机的校准板卡方法,其特征在于,所述映射关系为:

7.根据权利要求4所述的一种用于存储芯片ft测试机的校准板卡方法,其特征在于,所述通断检查为:

8.根据权利要求4所述的一种用于存储芯片ft测试机的校准板卡方法,其特征在于,power检查为:

技术总结本发明公开了一种用于存储芯片FT测试机的校准板卡方法,属于芯片测试技术领域,具体包括:对于任一校准板卡对应的两块数字板卡,校准板卡使用SPI总线对GPIO进行编程,通过switch的切换设定其中一块数字板卡为Master,另一块为Slaver,对二者进行同步校准;数字板卡内部的TG模板生成校准时需要的数字信号,通过PE芯片传输给校准板卡中的FPGA进行采集,FPGA将数字信号与校准参考时钟信号对比进行修正;校准板卡FPGA发送所需要的数字信号进行Strobe,传输到数字板卡内部与参考时钟信号对比,对仍有误差的数字通道再次补偿,完成校准;本发明实现了对校准板卡功能和效率的提升。技术研发人员:徐茂强,宋秀良,朱超,刘金海,薛如军受保护的技术使用者:悦芯科技股份有限公司技术研发日:技术公布日:2024/8/1本文地址:https://www.jishuxx.com/zhuanli/20240802/261424.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表