基体的背面处理方法和半导体器件的形成方法与流程

- 国知局

- 2024-08-08 16:57:16

本申请涉及半导体制造领域,具体而言,涉及一种基体的背面处理方法和半导体器件的形成方法。

背景技术:

1、目前市面上的半导体结构为了提升射频和漏电流失效的性能,需要在去除半导体结构的阻挡层的过程中,在快速热退火之前去除在炉管中生长的背面氮化硅层,单纯的进行溶液法将氮化硅层刻蚀去除会影响到用于提升半导体结构应力沉积的氮化硅层,目前大多数半导体结构生产采用背面刻蚀机去除半导体结构背面的氮化硅层,该方法费用较高,提高了半导体结构的制作成本。

技术实现思路

1、本申请提供一种基体的背面处理方法和半导体器件的形成方法,以解决相关技术中半导体结构在去除基体背面绝缘层的过程中产生较高成本的问题。

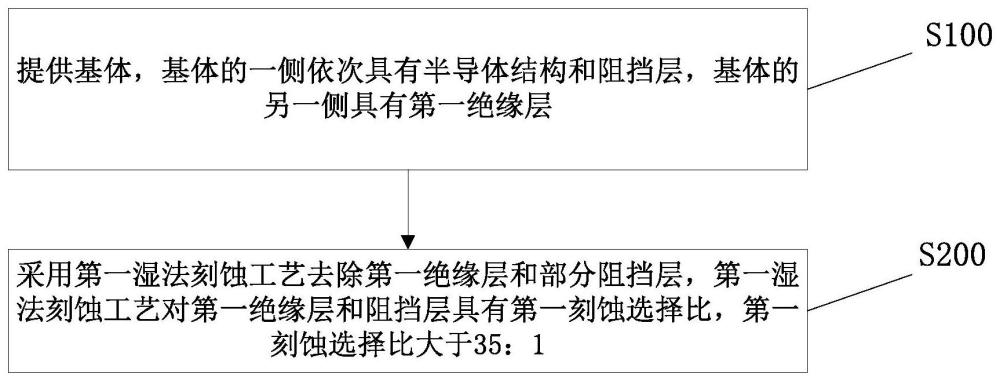

2、根据本申请的一个方面,提供了一种基体的背面处理方法,包括以下步骤:提供基体,基体的一侧依次具有半导体结构和阻挡层,基体的另一侧具有第一绝缘层;采用第一湿法刻蚀工艺去除第一绝缘层和部分阻挡层,第一湿法刻蚀工艺对第一绝缘层和阻挡层具有第一刻蚀选择比,第一刻蚀选择比大于35:1。

3、可选地,阻挡层包括氧化硅,第一绝缘层包括氮化硅。

4、可选地,第一湿法刻蚀工艺中采用的刻蚀剂包括磷酸。

5、可选地,第一刻蚀选择比为(40~50):1。

6、可选地,第一湿法刻蚀工艺中采用的刻蚀剂的体积分数为50%~85%。

7、可选地,在半导体结构远离第一绝缘层的一侧形成阻挡层的步骤之前,方法还包括:在半导体结构上形成第二绝缘层,第二绝缘层的应力范围为1gpa~2gpa。

8、可选地,在采用第二湿法刻蚀工艺去除剩余阻挡层的步骤之前,基体的背面处理方法还包括:对半导体结构进行退火处理,以将第二绝缘层的应力释放到半导体结构中。

9、可选地,采用第二湿法刻蚀工艺去除剩余阻挡层,第二湿法刻蚀工艺中采用的刻蚀剂的ph值为1~3。

10、可选地,退火处理温度范围为900℃~1100℃。

11、根据本申请的另一个方面,提供了一种半导体器件的形成方法,包括以下步骤:提供基体,基体的一侧具有半导体器件,基体的另一侧具有第一绝缘层;在半导体器件的一侧形成阻挡层;采用上述的背面处理方法,去除基体另一侧的第一绝缘层,得到最终的半导体器件。

12、通过本申请提供的一种基体的背面处理方法和半导体器件的形成方法,其中,通过在去除基体另一侧的第一绝缘层的过程中,采用第一湿法刻蚀工艺去除半导体结构背面的第一绝缘层部分阻挡层,第一湿法刻蚀工艺对第一绝缘层和阻挡层具有较大的刻蚀选择比,可以在完全去除第一绝缘层的基础上会保留部分阻挡层,以使得到的半导体器件的正面部分不被刻蚀破坏,进而省去了购买半导体结构背面刻蚀机的费用,降低了半导体器件的制造成本。

技术特征:1.一种基体的背面处理方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的基体的背面处理方法,其特征在于,所述阻挡层包括氧化硅,所述第一绝缘层包括氮化硅。

3.根据权利要求2所述的基体的背面处理方法,其特征在于,所述第一湿法刻蚀工艺中采用的刻蚀剂包括磷酸。

4.根据权利要求1所述的基体的背面处理方法,其特征在于,所述第一刻蚀选择比为(40~50):1。

5.根据权利要求3所述的基体的背面处理方法,其特征在于,所述第一湿法刻蚀工艺中采用的刻蚀剂的体积分数为50%~85%。

6.根据权利要求1至4中任一项所述的基体的背面处理方法,其特征在于,在所述半导体结构远离所述第一绝缘层的一侧形成阻挡层的步骤之前,所述基体的背面处理方法还包括:

7.根据权利要求6所述的基体的背面处理方法,其特征在于,在采用第二湿法刻蚀工艺去除剩余所述阻挡层的步骤之前,所述基体的背面处理方法还包括:

8.根据权利要求6所述的基体的背面处理方法,其特征在于,采用第二湿法刻蚀工艺去除剩余所述阻挡层,所述第二湿法刻蚀工艺中采用的刻蚀剂的ph值为1~3。

9.根据权利要求7所述的基体的背面处理方法,其特征在于,所述退火处理温度范围为900℃~1100℃。

10.一种半导体器件的形成方法,其特征在于,包括以下步骤:

技术总结本申请公开了一种基体的背面处理方法和半导体器件的形成方法。该基体的背面处理方法包括以下步骤:提供基体,基体的一侧依次具有半导体结构和阻挡层,基体的另一侧具有第一绝缘层;采用第一湿法刻蚀工艺去除第一绝缘层和部分阻挡层,第一湿法刻蚀工艺对第一绝缘层和阻挡层具有第一刻蚀选择比,第一刻蚀选择比大于35:1;采用该背面处理方法可以使半导体器件正面部分不被刻蚀破坏,进而省去了购买半导体结构背面刻蚀机的费用,降低了半导体结构的制造成本。技术研发人员:封贻杰,李万发,陈野,丁超,张京晶受保护的技术使用者:江苏卓胜微电子股份有限公司技术研发日:技术公布日:2024/8/5本文地址:https://www.jishuxx.com/zhuanli/20240808/271415.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表