一种抗总剂量高压NMOS结构的制作方法

- 国知局

- 2024-08-08 16:55:42

本发明涉及半导体器件,特别涉及一种抗总剂量高压nmos结构。

背景技术:

1、随着半导体器件在航空航天的电子系统等的应用越来越广泛,针对栅驱动、电源管理等电路的抗辐射加固技术成为研究人员的研究重点。总剂量辐射效应是由于器件长期积累的辐射能量,使器件功能和性能参数发生退化的效应。电离辐射会在sio2材料中产生电子空穴对,空穴与电子以漂移与扩散的形式运输,电子迁移率高,室温下能快速漂移出氧化层;而空穴则输运较慢,有可能被陷阱中心俘获,同时由于外界电场的作用,空穴向界面处跃迁,被界面处深能级俘获形成界面态,界面态还会形成感生电子。

2、高压cmos工艺已广泛应用于栅驱动等电路及模块的应用中。常规高压nmos结构源体使用sti进行隔离,在总剂量辐照下很容易产生感应电荷,源漏通过场区形成回路引发漏电。与常规cmos工艺不同,高压cmos工艺栅压和漏压均较高,高栅压使得器件的栅氧较于常规cmos工艺更厚,器件的总剂量效应也越严重,加固难度显著增大。

技术实现思路

1、本发明的目的在于提供一种抗总剂量高压nmos结构,以解决现有高压cmos中的总剂量漏电的问题。

2、为解决上述技术问题,本发明提供了一种抗总剂量高压nmos结构,包括:nmos器件栅端、源端、漏端、漂移区、阱、体区、场区、加固区、衬底、栅氧、和岛状场区;其中,

3、所述栅端为nmos晶体管的栅压控制端,用于控制晶体管沟道的导通和关闭;

4、所述源端和所述漏端为n型杂质的高掺杂区,在其上打孔并制作金属电极,分别作为源极s和漏极d;

5、所述漂移区为n型轻杂质掺杂区,用于提升nmos器件的耐压;

6、所述阱为p型轻掺杂区,用于形成沟道及隔离;

7、所述体区为p型杂质的高掺杂区,在其上打孔并制作金属电极,作为体电位的引出;

8、所述场区为浅槽隔离sti区域,用于隔离及耐压;

9、所述加固区为p型杂质的高掺杂区,用于抑制场区产生的总剂量效应;

10、所述衬底为体硅衬底,所述栅氧为sio2介质层;所述岛状场区与场区一致,为浅槽隔离区域。

11、在一种实施方式中,所述源端和所述漏端与所述场区分离,间隔距离为0.2μm~10μm;将所述体区的p型杂质的高掺杂注入在所述场区边缘,在保持高耐压的情况下抑制所述源端和所述漏端与所述场区之间的漏电通道。

12、在一种实施方式中,所述栅端非沟道区域进行p型重掺加固,抑制源漏之间的漏电通道,提升器件的抗总剂量能力。

13、在一种实施方式中,所述岛状场区位于所述栅端下方且介于所述场区和所述漂移区之间,用于多晶电极的引出,减少所述栅端下非沟道区域的面积,降低源漏之间非沟道区域的漏电,提升器件的抗总剂量能力。

14、在一种实施方式中,所述岛状场区周围注入所述体区的p型重掺和所述加固区的p型重掺,双重加固抑制场区之间以及场区与多晶下非沟道区的漏电通道,提升器件的抗总剂量能力。

15、在一种实施方式中,所述nmos器件为体硅器件或soi器件,所述衬底为p型衬底或n型衬底。

16、在一种实施方式中,所述源端和所述漏端的注入剂量为1e14cm-3~1e16cm-3,所述漂移区的注入剂量为1e11cm-3~1e13cm-3,所述阱的注入剂量为1e12cm-3~1e14cm-3,所述体区的注入剂量为1e14cm-3~1e16cm-3,所述场区为浅槽隔离sti,槽的深度为20nm~1000nm,所述加固区的注入剂量为1e12cm-3~1e15cm-3。

17、在一种实施方式中,所述栅氧的厚度大于等于10nm。

18、本发明提供的一种抗总剂量高压nmos结构,包括nmos器件的栅端、源端、漏端、体区、衬底、场区、阱、漂移区、加固区、衬底、栅氧和岛状场区。本发明将体区与源漏端分离,抑制源漏与场区之间的漏电通道;用岛状场区将多晶引出,减少多晶下非沟道区域的面积;将多晶下非沟道区及岛状场区周围进行高剂量p型重掺,抑制源漏之间和场区之间的漏电通道,有效的提升高压nmos器件的抗总剂量能力。

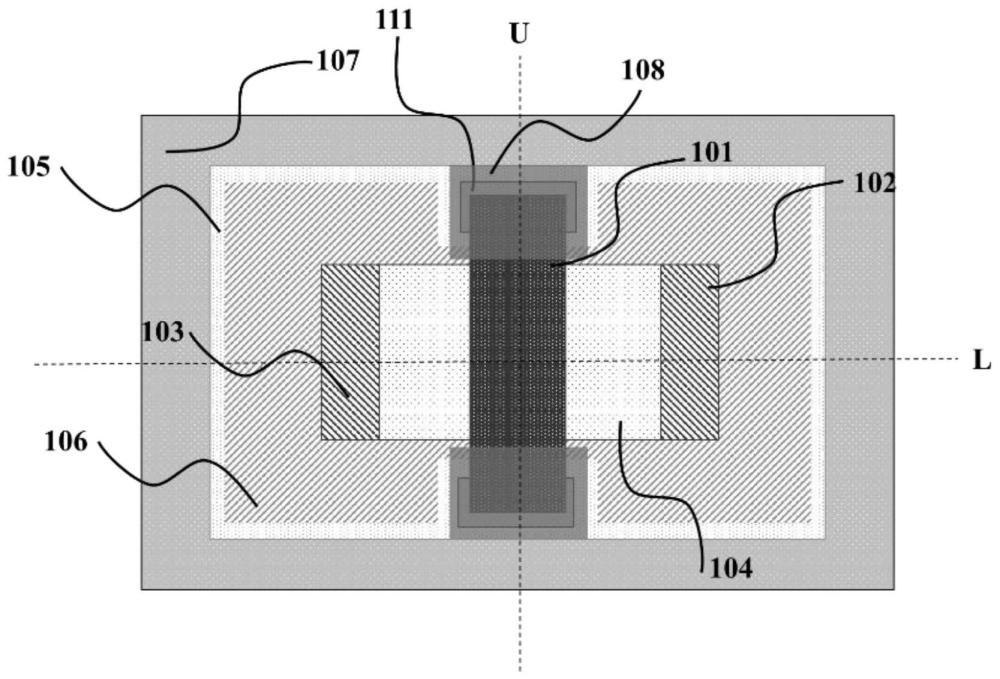

技术特征:1.一种抗总剂量高压nmos结构,其特征在于,包括:nmos器件栅端(101)、源端(102)、漏端(103)、漂移区(104)、阱(105)、体区(106)、场区(107)、加固区(108)、衬底(109)、栅氧(110)、和岛状场区(111);其中,

2.如权利要求1所述的抗总剂量高压nmos结构,其特征在于,所述源端(102)和所述漏端(103)与所述场区(107)分离,间隔距离为0.2μm~10μm;将所述体区(106)的p型杂质的高掺杂注入在所述场区(107)边缘,在保持高耐压的情况下抑制所述源端(102)和所述漏端(103)与所述场区(107)之间的漏电通道。

3.如权利要求1所述的抗总剂量高压nmos结构,其特征在于,所述栅端(101)非沟道区域进行p型重掺加固,抑制源漏之间的漏电通道,提升器件的抗总剂量能力。

4.如权利要求1所述的抗总剂量高压nmos结构,其特征在于,所述岛状场区(111)位于所述栅端(101)下方且介于所述场区(107)和所述漂移区(104)之间,用于多晶电极的引出,减少所述栅端(101)下非沟道区域的面积,降低源漏之间非沟道区域的漏电,提升器件的抗总剂量能力。

5.如权利要求1所述的抗总剂量高压nmos结构,其特征在于,所述岛状场区(111)周围注入所述体区(106)的p型重掺和所述加固区(108)的p型重掺,双重加固抑制场区之间以及场区与多晶下非沟道区的漏电通道,提升器件的抗总剂量能力。

6.如权利要求1所述的抗总剂量高压nmos结构,其特征在于,所述nmos器件为体硅器件或soi器件,所述衬底(109)为p型衬底或n型衬底。

7.如权利要求1所述的抗总剂量高压nmos结构,其特征在于,所述源端(102)和所述漏端(103)的注入剂量为1e14cm-3~1e16cm-3,所述漂移区(104)的注入剂量为1e11cm-3~1e13cm-3,所述阱(105)的注入剂量为1e12cm-3~1e14cm-3,所述体区(106)的注入剂量为1e14cm-3~1e16cm-3,所述场区(107)为浅槽隔离sti,槽的深度为20nm~1000nm,所述加固区(108)的注入剂量为1e12cm-3~1e15cm-3。

8.如权利要求8所述的抗总剂量高压nmos结构,其特征在于,所述栅氧(110)的厚度大于等于10nm。

技术总结本发明公开一种抗总剂量高压NMOS结构,属于半导体器件技术领域。所述发明包括NMOS器件的栅端、源端、漏端、体区、衬底、场区、阱、漂移区、加固区、衬底、栅氧和岛状场区。本发明将体区与源漏端分离,抑制源漏与场区之间的漏电通道;用岛状场区将多晶引出,减少多晶下非沟道区域的面积;将多晶下非沟道区及岛状场区周围进行高剂量P型重掺,抑制源漏之间和场区之间的漏电通道,有效的提升高压NMOS器件的抗总剂量能力。技术研发人员:彭洪,李燕妃,谢儒彬,王蕾,刘丹受保护的技术使用者:中国电子科技集团公司第五十八研究所技术研发日:技术公布日:2024/8/5本文地址:https://www.jishuxx.com/zhuanli/20240808/271249.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表