功率器件结构及制造方法与流程

- 国知局

- 2024-08-22 14:43:42

本技术内容涉及半导体系统、处理、及设备。更特定而言,本技术内容涉及用于改善高深宽比(aspect ratio)功率器件的缩放的处理与系统。

背景技术:

1、集成电路通过在基板表面上产生错综复杂地图案化的材料层的处理来实现的。在基板上产生图案化材料需要受控的方法以形成与移除材料。随着器件尺寸持续减小,集成电路内的特征可能会变得更小,结构的深宽比可能会增加,并且在处理操作期间保持这些结构的尺寸可能会受到挑战。一些处理可能造成材料中有凹陷特征,由于处理期间增加的暴露,这些凹陷特征的侧壁可能会不均匀或呈锥形。具有笔直侧壁的材料的显影可能会变得更加困难。再者,以材料回填凹陷特征而无任何接缝和/或空隙可能也变得更为困难。

2、因此,需要能够用于生产高品质器件和结构的改良系统与方法。本技术解决了这些和其他需求。

技术实现思路

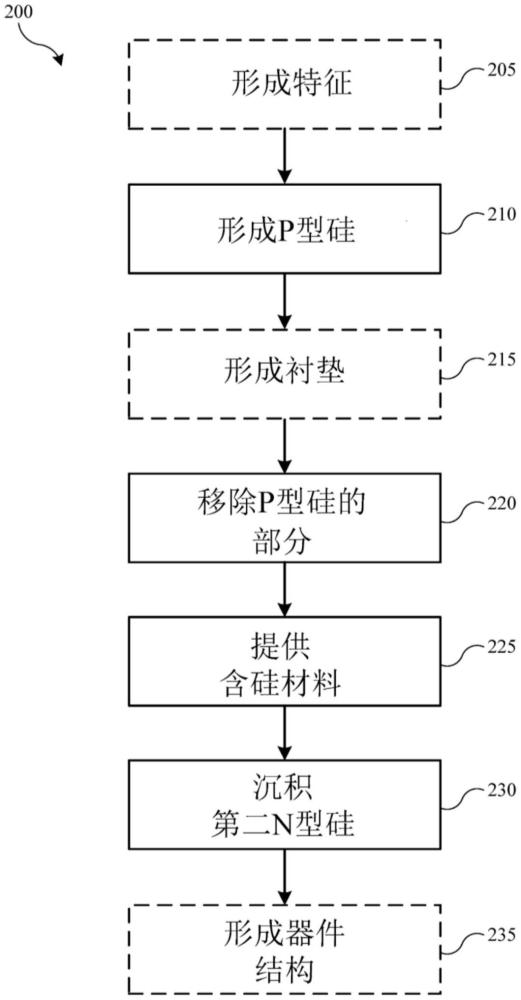

1、示例性半导体处理方法可包括在基板上形成p型含硅材料,所述基板包括界定一个或多个特征的第一n型含硅材料。所述p型含硅材料可沿着在所述第一n型含硅材料中所界定的所述一个或多个特征的至少一部分延伸。所述方法可包括移除所述p型含硅材料的一部分。可从所述一个或多个特征的底部移除所述p型含硅材料的所述部分。所述方法可包括提供含硅材料。所述方法可包括在所述基板上沉积第二n型含硅材料。所述第二n型含硅材料可填充在所述第一n型含硅材料中形成的所述一个或多个特征,并且可分隔剩余的p型含硅材料的区域。

2、在一些实施方式中,所述一个或多个特征的特征可在于大于或约1.5μm的宽度。所述p型含硅材料的特征可在于约5nm与约250nm之间的厚度。在所述基板上形成所述p型含硅材料的同时,半导体处理腔室内的温度可保持在大于或约600摄氏度。方法可包括提供含氧前驱物以及在所述p型含硅材料的至少一部分上面形成含氧材料。所述含氧前驱物可使所述p型含硅材料的至少一部分钝化。方法可包括在沉积所述第二n型含硅材料之前从所述p型含硅材料移除所述含氧材料。所述第一n型含硅材料和所述第二n型含硅材料可掺杂在磷、砷或上述两者的组合中。所述p型含硅材料可掺杂在硼中。所述第二n型含硅材料的宽度与所述p型含硅材料的宽度的比值可大于或约为15。所述p型含硅材料的特征可在于大于或约50的深宽比。方法可包括移除所述第二n型含硅材料的延伸到所述第一n型含硅材料、所述p型含硅材料或上述两者上方的一部分。在一些实施方式中,所述p型含硅材料可以是第一p型含硅材料。方法可进一步包括在所述基板上形成第二p型含硅材料。所述第二p型含硅材料可连接所述第一p型含硅材料的各个部分。

3、本技术的一些实施方式可涵盖多种半导体处理方法。方法可包括在基板上形成p型含硅材料。所述p型含硅材料可沿着基板上的在第一n型含硅材料中所界定的一个或多个特征的至少一部分延伸。方法可包括移除所述p型含硅材料的一部分。移除的所述p型含硅材料的所述部分可位于所述一个或多个特征的底部。方法可包括在所述基板上沉积第二n型含硅材料。所述第二n型含硅材料可填充所述一个或多个特征。

4、在一些实施方式中,所述一个或多个特征的特征可在于大于或约40的深宽比。所述p型含硅材料的特征可在于小于或约150nm的厚度。所述第一n型含硅材料或所述第二n型含硅材料的宽度与所述p型含硅材料的宽度的比值可大于或约为15。所述p型硅含硅材料可沿着在所述第一n型含硅材料中所界定的所述一个或多个特征的侧壁共形地形成。方法可包括在所述p型含硅材料的至少一部分上面形成含氧材料。含氧前驱物可使所述p型含硅材料的至少一部分钝化。方法可包括使所述含氧材料与蚀刻试剂接触。所述蚀刻试剂可移除所述含氧材料。所述第二n型含硅材料可填充所述一个或多个特征而无任何空隙并且没有间断性的蚀刻。

5、本技术的一些实施方式可涵盖功率器件。器件可包括第一含硅材料和第二含硅材料。所述第一含硅材料可界定特征在于深宽比大于或约50的一个或多个特征。所述第一含硅材料可以是或包括n型硅。所述第二含硅材料可设置在由所述第一含硅材料界定的所述一个或多个特征中。所述第二含硅材料可以是或包括p型硅。所述第二含硅材料可以共形地填充所述一个或多个特征。所述第二含硅材料可在所述一个或多个特征中没有空隙。

6、这样的技术可提供优于传统方法和技术的许多优点。例如,处理可容许在基板材料中形成更宽的特征,同时产生更高深宽比的结构。此外,通过增加初始特征宽度,可通过基板材料产生改善的蚀刻轮廓,此举可改善器件均匀性与填充。这些和其他实施方式连同其诸多优点和特征将结合下文的描述和所附附图更详细地描述。

技术特征:1.一种半导体处理方法,包括:

2.根据权利要求1所述的半导体处理方法,其中:

3.根据权利要求1所述的半导体处理方法,其中:

4.根据权利要求1所述的半导体处理方法,其中:

5.根据权利要求1所述的半导体处理方法,进一步包括:

6.根据权利要求5所述的半导体处理方法,进一步包括:

7.根据权利要求1所述的半导体处理方法,其中:

8.根据权利要求1所述的半导体处理方法,其中:

9.根据权利要求1所述的半导体处理方法,其中:

10.根据权利要求1所述的半导体处理方法,进一步包括:

11.根据权利要求10所述的半导体处理方法,其中:

12.一种半导体处理方法,包括:

13.根据权利要求12所述的半导体处理方法,其中所述一个或多个特征的特征在于大于或约40的深宽比。

14.根据权利要求12所述的半导体处理方法,其中:

15.根据权利要求12所述的半导体处理方法,其中:

16.根据权利要求15所述的半导体处理方法,其中:

17.根据权利要求12所述的半导体处理方法,进一步包括:

18.根据权利要求17所述的半导体处理方法,进一步包括:

19.根据权利要求12所述的半导体处理方法,其中:

20.一种功率器件,包括:

技术总结示例性半导体处理方法可包括在基板上形成p型含硅材料,该基板包括界定一个或多个特征的第一n型含硅材料。该p型含硅材料可沿着该第一n型含硅材料中所界定的该一个或多个特征的至少一部分延伸。方法可包括移除该p型含硅材料的一部分。可从该一个或多个特征的底部移除该p型含硅材料的该部分。方法可包括提供含硅材料。方法可包括在该基板上沉积第二n型含硅材料。该第二n型含硅材料可填充在该第一n型含硅材料中形成的该一个或多个特征,并且可分隔剩余的p型含硅材料的区域。技术研发人员:阿米尔哈桑·努尔巴赫什,拉曼·盖尔,泰勒·谢尔伍德,于澜,罗杰·奎恩,西达斯·克里希南受保护的技术使用者:应用材料公司技术研发日:技术公布日:2024/8/20本文地址:https://www.jishuxx.com/zhuanli/20240822/279625.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表