一种基于FPGA的大规模图像拼接加速方法、装置及介质

- 国知局

- 2024-09-05 14:27:10

本发明涉及图像处理,尤其是一种基于fpga的大规模图像拼接加速方法、装置及介质。

背景技术:

1、随着科技的发展,人类对视觉感知的需求不断提高,追求更清晰、更远和更广的视觉体验。高清摄像设备、长焦镜头和广角镜头的发明,使得人们能够以前所未有的清晰度和广度捕捉视觉信息,这极大地丰富了对世界的认知,推动了科学技术的发展。尤其在ai时代,人们对图像质量的要求越来越高。安全监控、机器人视觉和卫星遥感等领域都需要支持远距、大视场角和高分辨率图像的设备。

2、在当前的相机技术水平和成本限制下,视场角、探测距离和分辨率之间存在相互制约。

3、在图像拼接处理计算平台方面,主流方案可以分为以下三大类:

4、(1)以cpu为核心的计算平台:

5、将多个相机采集的图像经过cpu串行软件算法进行拼接。cpu因其灵活性高、通用性强、开发周期短,适合广泛应用。然而,cpu在处理海量高速图像数据时无法满足速度要求,成为其主要限制。

6、(2)以gpu为核心的计算平台:

7、将多个相机采集的图像经过gpu并行软件算法进行拼接。gpu擅长处理高数据量并行的图像数据,已经在许多应用中得到广泛使用。其并行处理能力强,适合大规模图像处理任务。然而,gpu的高功耗特性使其难以部署在边缘设备上,限制了应用场景。

8、(3)以fpga为核心的计算平台:

9、将多个相机直接与fpga平台相连,fpga负责相机控制、图像采集与拼接。fpga(现场可编程门阵列)具有实时性强、灵活性高且功耗低的优点,能够将硬件与软件相结合,并行处理多路图像数据。fpga方案的实物体积小、功耗低,方便部署到各种应用场景。然而,基于fpga的开发门槛高、开发周期长,需要较高的专业知识和技术。

10、当前基于cpu和gpu通用计算平台的图像拼接系统存在以下几个主要缺点:

11、(1)拼接速度慢、实时性低:cpu和gpu虽然在灵活性和通用性方面表现出色,但在处理超高分辨率图像时,由于数据量巨大,处理速度相对较慢,难以实现实时拼接。这对于需要即时反馈的应用场景,如安全监控和机器人视觉,是一个显著的限制。

12、(2)功耗高、体积大:gpu在处理大规模并行计算时表现出色,但其高功耗和体积大的特点,使其不适合部署在需要低功耗的边缘设备或便携设备中。cpu虽然功耗相对较低,但在处理高分辨率图像拼接时,其性能不足,难以满足实际需求。

13、现有的基于专用芯片或fpga的图像拼接方法和系统也存在一定的局限性:

14、适用性有限:尽管fpga在图像处理中的并行计算能力和低功耗特性使其成为一种理想的解决方案,但现有的fpga图像拼接系统多用于中等分辨率和视场的应用,对于超高分辨率、大视场、远视距的多个相机图像拼接,尚无成熟的解决方案。

技术实现思路

1、有鉴于此,本发明实施例提供一种低功耗且高效率的基于fpga的大规模图像拼接加速方法、装置及介质。

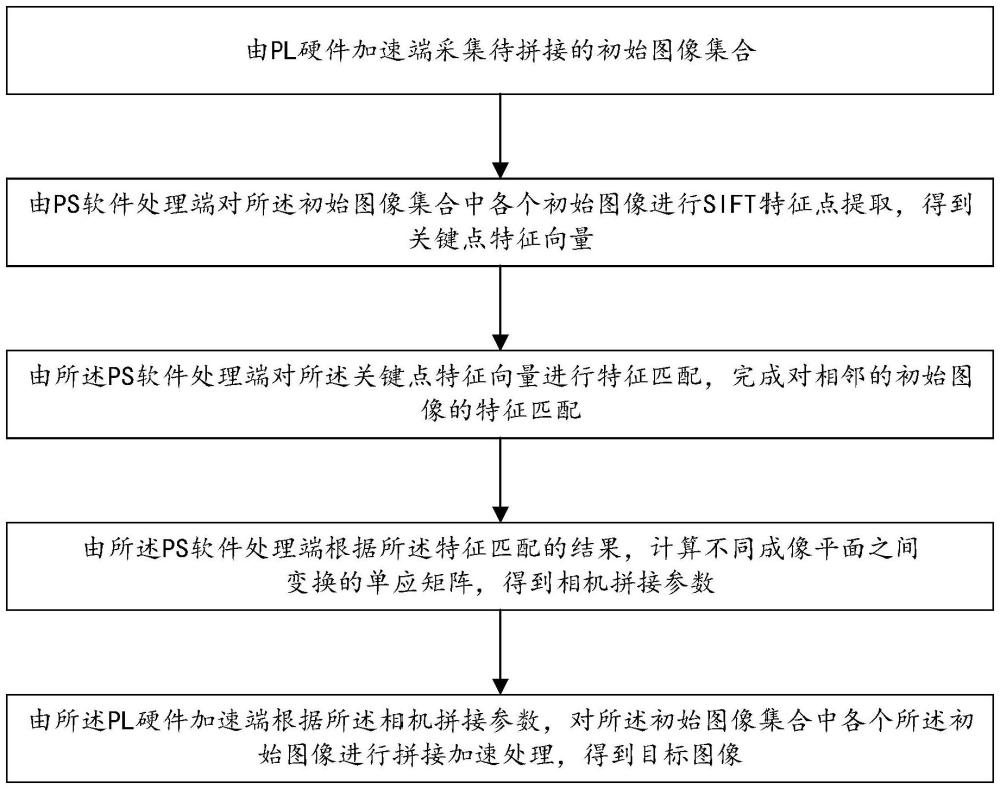

2、本发明实施例的一方面提供了一种基于fpga的大规模图像拼接加速方法,包括以下步骤:

3、由pl硬件加速端采集待拼接的初始图像集合;

4、由ps软件处理端对所述初始图像集合中各个初始图像进行si ft特征点提取,得到关键点特征向量;

5、由所述ps软件处理端对所述关键点特征向量进行特征匹配,完成对相邻的初始图像的特征匹配;

6、由所述ps软件处理端根据所述特征匹配的结果,计算不同成像平面之间变换的单应矩阵,得到相机拼接参数;

7、由所述pl硬件加速端根据所述相机拼接参数,对所述初始图像集合中各个所述初始图像进行拼接加速处理,得到目标图像。

8、可选地,所述由所述pl硬件加速端根据所述相机拼接参数,对所述初始图像集合中各个所述初始图像进行拼接加速处理,得到目标图像,包括以下步骤:

9、由所述pl硬件加速端的参数传输模块获取所述相机拼接参数,并将所述相机拼接参数发送到映射模块;

10、根据所述相机拼接参数,由所述映射模块根据拼接参数指示的拼接图与源图的映射关系,通过拼接图像素坐标计算源图像素坐标;

11、根据所述源图像素坐标,通过图像数据预取模块读取源图像素;

12、将所述源图像素进行加权得到拼接图像素,并将所述拼接图像素传入所述ps软件处理端,直至完成所有拼接图像素的传输,拼接得到所述目标图像。

13、可选地,所述根据所述相机拼接参数,由所述映射模块根据拼接参数指示的拼接图与源图的映射关系,通过拼接图像素坐标计算源图像素坐标,包括以下步骤:

14、根据所述相机拼接参数,生成所述拼接图像素坐标;

15、根据所述拼接图像素坐标读取存在ps软件处理端ddr内存的像素掩膜查找表;其中,所述像素掩膜查找表用于在图像拼接时,确定在拼接图像之间的重合区域的源像素来源;

16、根据所述像素掩膜查找表,通过所述拼接图像素坐标反向映射到所述源图像素坐标。

17、可选地,所述方向映射这一过程的表达式为:

18、

19、

20、其中,x、y、z为基准世界坐标;ki、ri分别为第i个相机的内参和相对基准世界的旋转矩阵;si为第i个相机尺度;tix、tiy、tiz为第i个相机相对坐标偏移;u、v为拼接图像素坐标;x、y为源图像素坐标。

21、可选地,所述方法还包括以下步骤:

22、将所述拼接图像素坐标的生成过程、所述方向映射的过程以及所述将所述源图像素进行加权得到拼接图像素的过程配置为流水线化模式,以使得各个过程在单个时钟周期执行并行操作。

23、可选地,所述方法还包括以下步骤:

24、在将所述相机拼接参数发送到映射模块之前,将所述相机拼接参数的浮点型数据格式进行定点化处理。

25、可选地,所述方法还包括以下步骤:

26、在得到所述源图像素坐标之后,检查所述图像数据预取模块内缓存的图块是否包含了所述源图像素坐标对应的像素,若是,则提取相应bayer数据,再经过插值后输出rgb像素数据;若否,则根据所述源图像素坐标从pl硬件加速端的内存中读取相匹配的图像块作为所述源图像素;

27、将存储在内存的图像格式从rgb格式改为bayer格式,以使得每次读取的图像块都是bayer格式;并且,在所述图像数据预取模块中加入bayer插值模块,以使得最终输出rgb像素数据。

28、本发明实施例的另一方面还提供了一种基于fpga的大规模图像拼接加速装置,包括:

29、第一模块,用于由pl硬件加速端采集待拼接的初始图像集合;

30、第二模块,用于由ps软件处理端对所述初始图像集合中各个初始图像进行si ft特征点提取,得到关键点特征向量;

31、第三模块,用于由所述ps软件处理端对所述关键点特征向量进行特征匹配,完成对相邻的初始图像的特征匹配;

32、第四模块,用于由所述ps软件处理端根据所述特征匹配的结果,计算不同成像平面之间变换的单应矩阵,得到相机拼接参数;

33、第五模块,用于由所述pl硬件加速端根据所述相机拼接参数,对所述初始图像集合中各个所述初始图像进行拼接加速处理,得到目标图像。

34、本发明实施例的另一方面还提供了一种电子设备,包括处理器以及存储器;

35、所述存储器用于存储程序;

36、所述处理器执行所述程序实现如前面所述的方法。

37、本发明实施例的另一方面还提供了一种计算机可读存储介质,所述存储介质存储有程序,所述程序被处理器执行实现如前面所述的方法。

38、本发明实施例还公开了一种计算机程序产品或计算机程序,该计算机程序产品或计算机程序包括计算机指令,该计算机指令存储在计算机可读存储介质中。计算机设备的处理器可以从计算机可读存储介质读取该计算机指令,处理器执行该计算机指令,使得该计算机设备执行前面的方法。

39、本发明的实施例由pl硬件加速端采集待拼接的初始图像集合;由ps软件处理端对所述初始图像集合中各个初始图像进行si ft特征点提取,得到关键点特征向量;由所述ps软件处理端对所述关键点特征向量进行特征匹配,完成对相邻的初始图像的特征匹配;由所述ps软件处理端根据所述特征匹配的结果,计算不同成像平面之间变换的单应矩阵,得到相机拼接参数;由所述pl硬件加速端根据所述相机拼接参数,对所述初始图像集合中各个所述初始图像进行拼接加速处理,得到目标图像。本发明实施例提高了图像拼接速度,并且降低了计算功耗。

本文地址:https://www.jishuxx.com/zhuanli/20240905/286518.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。