一种可综合真随机数发生器及可综合真随机数发生方法与流程

- 国知局

- 2024-09-11 14:57:40

本发明涉及信息安全,特别是涉及一种可综合真随机数发生器及可综合真随机数发生方法。

背景技术:

1、目前,物联网应用预计市场规模已经超过百亿,但新兴技术时代已为硬件攻击提供了良好的环境。因为在硬件设计过程中,为了避免错过推出新产品时机黄金机会,或者在激烈的市场竞争中降低产品成本,在一些边缘节点或功耗敏感节点,安全仍然是一个次要考虑或被主动忽视的问题。2018年,著名芯片供应商intel被爆出芯片的安全漏洞,该漏洞允许恶意程序窃取内存信息,多家著名芯片供应商(英特尔、amd、arm等)深陷芯片安全漏洞的危机中。一旦这些信息被恶意获取,将导致大量用户敏感信息泄密。

2、为了防止此类事件的发生,提高信息的安全性,现代密码学经常被应用在安全系统中,在现代密码学应用中,随机数有非常重要的地位,因此真随机数发生器在国内外已成为该领域的研究热点。

3、对于制造真随机数发生器(true random number generator,简写为:trng),热噪声是一个很好的随机熵源,因为它的频谱分布相对均匀且不随互补金属氧化物半导体(complementary metal oxide semiconductor,简写为:cmos)工艺变化而变化。早期集成电路里面,大多采用这种方式提取随机数。但是热噪声通常都是非常微弱的,因此需要一个超宽带宽、高增益的放大器来放大噪声达到可以量化的目的。而这种宽频放大器不仅需要很大的芯片面积,也会消耗大量的功耗。最近韩国首尔大学提出了一种利用共模比较器和d触发器的采样误差来放大热噪声来产生随机数的集成电路,其码速可达3gb/s,但它的功耗高达5mw,不适合低功耗的物联网(internet of things,简写为:iot)设备。其次,它还需外部提供一个高速采样时钟(3ghz),普通设备很难满足这样的条件。

4、另外,利用处于亚稳态的锁存器或者静态随机存储器(static random accessmemory,简写为:sram)也可以来产生真随机数,这种熵源的随机输出序列一般都需要一个很复杂的后处理单元。譬如英特尔公司花了近十年时间研制的一款高速真随机发生器,它不仅仅需要在芯片布局上严格对称,还需要后续数字处理来满足统计的均匀性。

5、第三种是利用环形振荡器(ring oscillatior,简写为:ro)的抖动(jitter)噪声来产生真随机数。这类设计的优势在于可以很方便、灵活地在现场可编程门阵列(fieldprogrammable gate array,简写为:fpga)或者专用集成电路(application specificintegrated circuit,简写为:asic)上实现。其原理是利用时钟或信号来采样另一时钟,采样得到的数据包含了随机jitter噪声。美国密西根大学提出一种基于双注入环形振荡器电路的真随机数发生器,利用两个布局对称环形振荡器中的抖动竞争来产生随机数。其表现出很好的随机性和对工艺、电压和温度(process、voltage、temperature,简写为:pvt)的稳定性。但它的缺点在于需要手动不断的去选择振荡器的参数,达到最稳定的性能。同时,为了达到高稳定性,它还要剔除大量不稳定的输出数据,导致实际效率有所下降。

6、最后一种真随机数是基于确定性描述的混沌系统方程。利用混沌图(chaos map),这些真随机数可以提供高熵值的随机输出序列,它们对初始条件极为敏感,导致长期的不可预测性。

7、在以上的trng设计中,较少有设计可以直接进行综合。即使是基于ro设计trng,也会存在需要手动布局布线的情况。

8、有鉴于此,如何克服现有技术所存在的缺陷,如何实现一种综合的纯数字trng架构,使其可以灵活部署于各种应用中,是本技术领域待解决的难题。

技术实现思路

1、针对现有技术中的缺陷或改进需求,本发明提供一种可综合真随机数发生器及可综合真随机数发生方法,通过数字逻辑的开发便捷性,提高trng电路设计的通用性、便捷性,使其实现综合的纯数字trng架构,使其可以灵活部署于各种应用中。

2、本发明采用如下技术方案:

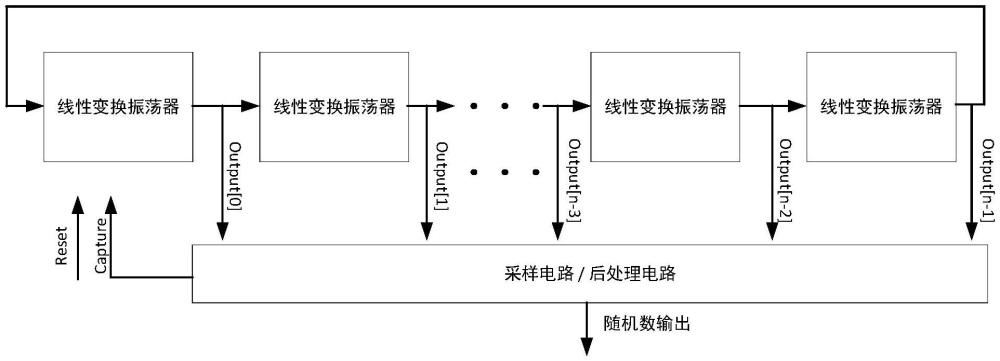

3、第一方面,本发明提供了一种可综合真随机数发生器,包括多个依次串联的线性变换振荡器以及与多个所述线性变换振荡器分别连接的熵采样电路;其中:

4、所述线性变换振荡器用于提供震荡信号;

5、所述熵采样电路用于对所述线性变换振荡器产生的振荡信号进行采样,以获得原始随机序列。

6、在一些实施例中,所述线性变换振荡器包括线性变换单元、反馈单元以及延迟单元,其中:

7、所述线性变换单元提供线性变换函数,包括组合逻辑运算、sbox以及杂凑算法中的一种或多种;

8、所述反馈单元用于接收上一级线性变换振荡器的输出以及本级线性变换单元的输出,并通过运算后,提供本级线性变换单元的输入;

9、所述延迟单元用于提供时延,延迟所述线性变换单元的输出。

10、在一些实施例中,所述反馈单元与所述线性变换单元之间设置有第一级mux,所述反馈单元将所述线性变换振荡器的输入加一之后与输出结果一起送到第一级mux,所述第一级mux通过reset信号控制;当reset为高电平时,所述线性变换振荡器复位,输入值被reset值锁定;当reset为低电平时,所述反馈单元的输出被传输到所述线性变换单元的输入。

11、在一些实施例中,所述线性变换单元与所述延迟单元之间设置有第二级mux,所述线性变换单元的输出被接到所述第二级mux,所述第二级mux使用capture信号进行控制;当capture为高电平时,所述延迟单元输入为output,此时为提取状态,振荡器停止振荡;当capture为低电平时,所述线性变换单元的输出经过延迟单元被输出到output端口,output数据输出到下一级线性变换振荡器以及本级反馈单元。

12、在一些实施例中,所述线性变换振荡器的反馈单元包括三级逻辑,第一级逻辑包括一个加法器,对输入信号进行加一;第二级逻辑包括异或电路,将上一级输出与线性变换振荡器输入进行异或,将反馈单元引入的扰动融合进线性变换振荡器的振荡中;第三级逻辑包括一个由偶数个反相器构成的延迟单元,提供振荡器工作所需要的信号延迟。

13、在一些实施例中,所述熵采样电路的熵采样频率,即capture信号频率远低于所述线性变换振荡器的振荡频率;所述capture信号使用一个可配置的时钟源提供,所述capture信号的频率以及高电平脉宽可调。

14、在一些实施例中,还包括与所述熵采样电路连接的后处理电路,所述后处理电路用于矫正原始随机序列中存在的随机缺陷,提高输出熵值和随机性;所述后处理电路根据输出数据特征选择不同的后处理算法,包括异或、lfsr、奇偶分组、vn后处理中的一种或多种。

15、在一些实施例中,还包括振荡监测电路,所述振荡检测电路对所述线性变换振荡器的振荡状态进行监测,若出现线性变换函数输出锁定的情况,即对外报警并切断熵源输出。

16、在一些实施例中,所述振荡监测电路实时监测所述线性变换振荡器的输出,并与上一周期输出进行对比,若n个线性变换振荡器的输出均与上一周期输出一致,则判断线性变换振荡器锁死,振荡监测电路向外发出报警信号,并切断熵源数据输出。

17、第二方面,本发明提供了一种可综合真随机数发生方法,包括:

18、通过多个依次串联的线性变换振荡器提供震荡信号;

19、通过熵采样电路对所述线性变换振荡器产生的振荡信号进行采样,以获得原始随机序列;

20、通过后处理电路矫正原始随机序列中存在的随机缺陷,提高输出熵值和随机性。

21、与现有技术相比,本发明的有益效果在于:

22、1、本发明基于一种新型的串联线性变换振荡器实现trng,其中线性变换函数、反馈函数都可以使用组合逻辑实现。例如线性变换函数为一个sbox,可直接使用查找表实现;例如反馈函数可以使用加法器、异或门以及反相器组成的延迟单元实现。由于本发明所使用的结构都是数字集成电路的基本单元,因此本设计是可综合的。该特点大大提高了所提出trng架构的通用性、可移植性。

23、2、本发明可以通过选用不同的线性变换配置改变占用面积、输出速率,例如使用的sbox每个采样周期可以输出8比特数据,若将这个sbox改为sm3算法,每个采样周期可以提供256比特数据。可根据应用场景选用不同的函数,配置轻量级或高速率的trng。

24、3、在本发明的工作状态下(reset信号为低电平),由于本发明中的可配置时钟源控制了线性变换振荡器的振荡启停、振荡时间,通过可控时钟源的配置,可以在实际使用过程中动态配置输出速率,方便系统动态控制功耗。

本文地址:https://www.jishuxx.com/zhuanli/20240911/292677.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表