半导体装置的制作方法

- 国知局

- 2024-09-14 14:27:44

本发明涉及半导体装置。

背景技术:

1、在专利文献1中,记载了在同一半导体基板设置有igbt区和二极管区的半导体装置。

2、现有技术文献

3、专利文献

4、专利文献1:日本特开2020-72137号公报

技术实现思路

1、技术问题

2、提供一种维持晶体管特性,并且降低反向恢复损耗的半导体装置。

3、技术方案

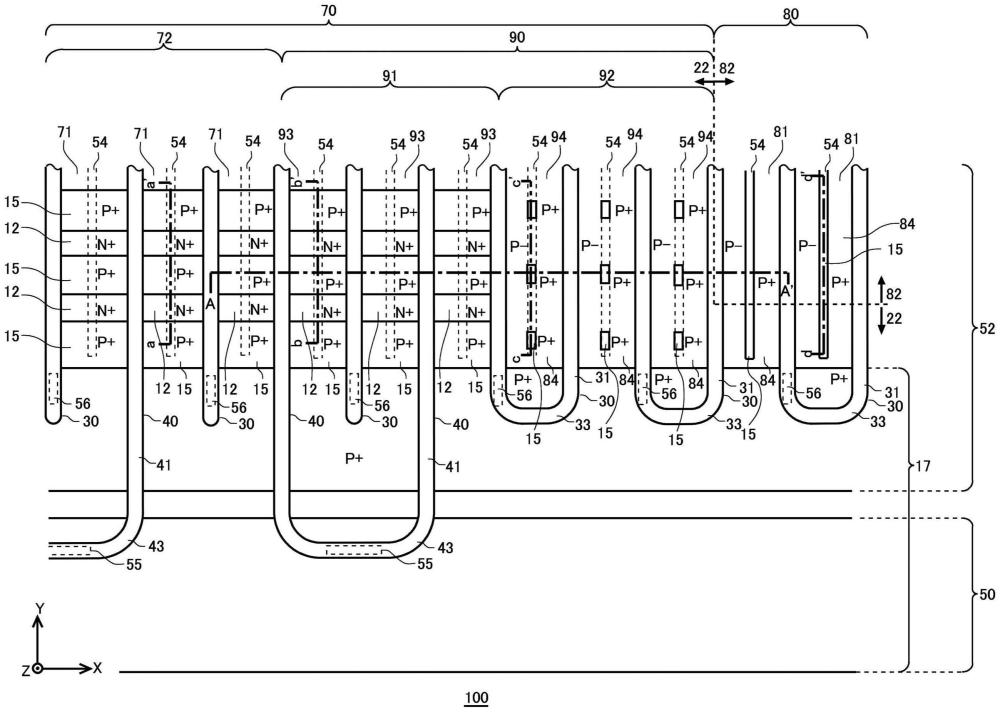

4、在本发明的第一方式中,提供一种具备半导体基板的半导体装置,所述半导体基板具有晶体管部和二极管部。所述半导体基板具有:多个沟槽部,其设置于所述半导体基板的正面,并且包括栅极沟槽部;第一导电型的漂移区,其设置于所述半导体基板;第二导电型的基区,其在所述晶体管部中设置于所述漂移区的上方;第一导电型的发射区,其设置于所述半导体基板的正面,且掺杂浓度比所述漂移区的掺杂浓度高;第二导电型的接触区,其设置于所述半导体基板的正面,且掺杂浓度比所述基区的掺杂浓度高;以及第二导电型的阳极区,其在所述二极管部中设置于所述漂移区的上方,且掺杂浓度比所述接触区的掺杂浓度低,所述晶体管部具有:主区,其与所述二极管部分离地设置;以及边界区,其与所述二极管部邻接地设置,所述边界区具有:第一边界部,其具有所述发射区;以及第二边界部,其具有所述阳极区和所述接触区,所述第一边界部具有第二导电型的注入抑制区,所述第二导电型的注入抑制区在沟槽延伸方向上与所述发射区交替地设置,并且抑制第二导电型载流子的注入。

5、所述注入抑制区的平均掺杂浓度可以比所述基区的掺杂浓度高,可以比所述接触区的掺杂浓度低。

6、所述注入抑制区可以具有所述基区和所述接触区。

7、在所述半导体基板的正面,所述注入抑制区中的所述接触区的面积比率可以为所述主区中的所述接触区的面积比率的5%以上且80%以下。

8、所述边界区的沟槽排列方向上的宽度可以为50μm以上且200μm以下。

9、所述边界区的沟槽排列方向上的宽度可以为所述半导体基板的厚度的0.5倍以上且2倍以下。

10、所述第一边界部的沟槽排列方向上的宽度可以为50μm以上且150μm以下。

11、所述第一边界部可以具有所述栅极沟槽部。

12、所述第二边界部的所述接触区可以包含在沟槽延伸方向上分散地设置的多个接触区。

13、在所述半导体基板的正面,所述第二边界部的所述接触区的面积比率可以比所述二极管部的所述接触区的面积比率小。

14、所述第二边界部的沟槽排列方向上的宽度可以为20μm以上且100μm以下。

15、所述多个沟槽部可以具有虚设沟槽部,所述第二边界部可以具有所述虚设沟槽部,并且不具有所述栅极沟槽部。

16、所述发射区可以包括在沟槽延伸方向上分散地设置的多个发射区,所述注入抑制区可以包括在沟槽延伸方向上设置在所述多个发射区之间的多个注入抑制区。

17、所述注入抑制区的所述接触区的下端可以具有在所述半导体基板的深度方向上凹陷的凹部。

18、在所述半导体基板的正面,所述注入抑制区的所述基区的沟槽延伸方向上的两端可以与所述接触区相接。

19、在所述半导体基板的正面,所述第一边界部的所述发射区的沟槽延伸方向上的两端可以与所述注入抑制区的所述接触区相接。

20、所述第二边界部的所述接触区可以设置为,在沟槽排列方向上从一条沟槽部延伸到对置的另一条沟槽部。

21、在所述半导体基板的正面,所述注入抑制区可以具有第一区,所述第一区包含从一条沟槽部延伸到对置的另一条沟槽部而设置的所述接触区,所述第一区可以与所述发射区相接地设置。

22、在所述半导体基板的正面,所述注入抑制区可以具有第二区,所述第二区包括与对置的两条沟槽部的侧壁相接地设置的所述接触区以及与所述对置的两条沟槽部分离地设置的所述基区,所述第二区可以与所述第一区相接地设置。

23、在所述半导体基板的正面,所述注入抑制区可以具有第三区,所述第三区包括从一条沟槽部延伸到对置的另一条沟槽部而设置的所述基区。

24、所述第一边界部的所述发射区的沟槽延伸方向上的宽度可以比所述主区的所述发射区的沟槽延伸方向上的宽度小。

25、所述第一边界部的所述发射区的沟槽延伸方向上的宽度在沟槽排列方向上可以随着靠近所述二极管部而变小。

26、所述第一边界部的所述发射区在沟槽延伸方向上的节距可以与所述主区的所述发射区在沟槽延伸方向上的节距相同。

27、所述二极管部可以具有沿沟槽延伸方向延伸而设置的所述接触区。

28、所述接触区的掺杂浓度可以为1e18cm-3以上且1e21cm-3以下。

29、所述基区的掺杂浓度可以为1e16cm-3以上且1e18cm-3以下。

30、所述阳极区的掺杂浓度可以与所述基区的掺杂浓度相同。

31、所述阳极区的掺杂浓度可以比所述基区的掺杂浓度低。

32、在所述半导体基板,在比所述半导体基板的深度方向上的中心更靠正面侧的位置,可以不设置包含寿命抑制剂的寿命控制区。

33、应予说明,上述的技术实现要素:并未列举出本发明的全部特征。另外,这些特征组的子组合也能够成为发明。

技术特征:1.一种半导体装置,其特征在于,具备半导体基板,所述半导体基板具有晶体管部和二极管部,

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求1所述的半导体装置,其特征在于,

4.根据权利要求3所述的半导体装置,其特征在于,

5.根据权利要求1所述的半导体装置,其特征在于,

6.根据权利要求1所述的半导体装置,其特征在于,

7.根据权利要求1所述的半导体装置,其特征在于,

8.根据权利要求1所述的半导体装置,其特征在于,

9.根据权利要求1所述的半导体装置,其特征在于,

10.根据权利要求9所述的半导体装置,其特征在于,

11.根据权利要求1所述的半导体装置,其特征在于,

12.根据权利要求1所述的半导体装置,其特征在于,

13.根据权利要求1所述的半导体装置,其特征在于,

14.根据权利要求4所述的半导体装置,其特征在于,

15.根据权利要求2所述的半导体装置,其特征在于,

16.根据权利要求5所述的半导体装置,其特征在于,

17.根据权利要求15所述的半导体装置,其特征在于,

18.根据权利要求1所述的半导体装置,其特征在于,

19.根据权利要求18所述的半导体装置,其特征在于,

20.根据权利要求17或18所述的半导体装置,其特征在于,

21.根据权利要求1所述的半导体装置,其特征在于,

22.根据权利要求21所述的半导体装置,其特征在于,

23.根据权利要求21所述的半导体装置,其特征在于,

24.根据权利要求1所述的半导体装置,其特征在于,

25.根据权利要求1所述的半导体装置,其特征在于,

26.根据权利要求1所述的半导体装置,其特征在于,

27.根据权利要求1所述的半导体装置,其特征在于,

28.根据权利要求1所述的半导体装置,其特征在于,

29.根据权利要求1所述的半导体装置,其特征在于,

技术总结本发明提供一种半导体装置,该半导体装置具备半导体基板,该半导体基板具有晶体管部和二极管部,晶体管部具有:主区,其与二极管部分离地设置;以及边界区,其与二极管部邻接地设置,边界区具有:第一边界部,其具有发射区;以及第二边界部,其具有阴极区和接触区,第一边界部具有第二导电型的注入抑制区,所述第二导电型的注入抑制区在沟槽延伸方向上与发射区交替地设置,并且抑制第二导电型载流子的注入。技术研发人员:吉川功受保护的技术使用者:富士电机株式会社技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/294195.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表