开关转换器的异步状态机的制作方法

- 国知局

- 2024-09-14 14:54:46

本公开总体上涉及电子电路,并且具体地,涉及开关转换器的有限状态机(fsm),即,用于向开关转换器的截止开关供应控制信号的有限状态机。

背景技术:

1、开关转换器是在大量应用中用于将转换器的输入电压(例如直流(dc)电压)转换成转换器的输出电压(例如dc输出电压)的电路,其中输出电压的值由设定点确定。

2、图1非常示意性地图示了这样的开关转换器1的示例。

3、转换器1包括高压侧开关hss和低压侧开关lss。

4、开关hss将转换器1的节点100耦接到转换器1的连接节点(或开关节点)102。节点100被配置为接收电源电势vdd。

5、开关lss将转换器1的节点104耦接到节点102。节点104被配置为接收参考电势,例如,地gnd电势。

6、以参考电势gnd为参考的电势vdd对应于转换器1的输入电压或电源电压。

7、转换器1还包括电感器l。电感器l将节点102耦接到转换器1的输出端out。在转换器1的输出端out上可得输出电压vout。

8、作为示例,每个开关hss、lss由一个或多个mos晶体管实现。

9、为了控制截止开关hss和lss,转换器包括有限状态机fsm,或者换句话说,实现有限状态机的电路fsm。电路fsm被配置为控制开关hss和lss中的每一个处于导通和截止状态。

10、更特别地,状态机fsm被配置为供应第一二进制信号cmdh,其具有控制开关hss处于截止状态的第一二进制状态和控制该开关hss控制处于导通状态的第二二进制状态。类似地,状态机fsm被配置为供应第二二进制信号cmdl,其具有控制开关lss处于截止状态的第一二进制状态和控制该开关lss处于导通状态的第二二进制状态。

11、作为示例,信号cmdh被直接地或经由驱动器电路driverh供应到开关hss的控制端子,例如,供应到实现该开关的mos晶体管的栅极。作为示例,信号cmdl被直接地或经由驱动器电路driverl供应到开关lss的控制端子,例如,供应到实现该开关的mos晶体管的栅极。

12、信号cmdh和cmdl的二进制状态由状态机fsm的当前状态来确定。

13、状态机fsm包括通过转变而耦接在一起的多种状态。为了确定状态机fsm是应该还是不应该实现两种状态之间的转换,例如,在状态机fsm的当前状态与状态机fsm的下一状态之间的转换,电路fsm接收输入信号sig-in。信号sig-in指示针对转换器1的信号的条件是否通过验证。例如,信号sig-in指示在电感器l中流动的电流是否具有零值,输出电压vout是大于还是小于至少一个阈值等。

14、通常,当电路fsm被同步地实现时,即,当状态机fsm的当前状态和状态机fsm的输出cmdh和cmdl被以周期时钟信号的频率更新时,电路fsm包括:状态寄存器,其具有指示状态机fsm的当前状态的输出和接收状态机fsm的下一状态的指示的输入;以及组合电路,其将信号sig-in和状态寄存器的输出当作输入,并且供应状态机的下一状态的指示。

15、在这种情况下,状态机fsm的状态寄存器在周期时钟信号的每个周期被更新。

16、作为示例,例如,基于状态机fsm的当前状态的指示,即,基于状态寄存器的输出来确定输出cmdh和cmdl。作为替代示例,电路fsm还包括:供应输出cmdh和cmdl的输出寄存器和接收输出cmdh和cmdl的下一个值的指示的输入端;以及组合电路,其接收状态机fsm的当前状态的指示和信号sig-in,并且供应输出cmdh和cmdl的下一个值的指示。

17、在该替代示例中,在周期时钟信号的每个周期,输出寄存器和状态寄存器被同时更新。

18、然而,电路fsm的同步实现的缺点在于,周期时钟信号的频率必须比开关lss和hss的开关频率或控制频率大得多,例如,至少大100倍,从而以足够准确的方式调节电压vout的值。这带来了各种问题。例如,这使转换器1不适用于期望使功耗最小化的应用。

19、为了克服同步实现有限状态机的缺点,已提供实现纯异步有限状态机,即没有时钟信号。那么,这些纯异步状态机借助于诸如穆勒单元(muller cell)之类的专用电子组件来实现。

20、然而,纯异步状态机的设计需要特定的开发工具,这些开发工具通常与开发由周期时钟信号额定的数字电路的工具不兼容。另外,纯异步状态机通常与由周期时钟信号额定的数字电路不兼容。

21、为了克服同步实现的有限状态机和纯异步有限状态机固有的缺点,还提供了实现全局异步-本地同步(gals)状态机的方法。

22、gals型状态机的实现类似于上述替代示例的纯同步状态机,不同之处在于:gals型状态机不包括控制其状态和输出寄存器更新的周期性时钟信号;gals型状态机包括用于存储其输入信号的电路,如此存储的信号被供应到提供状态机的下一状态的指示和状态机的输出的下一个值的指示的组合电路;并且gals型状态机包括本地时钟生成电路,该本地时钟生成电路被配置为基于状态机的下一状态的指示和状态机的当前状态的指示来供应本地时钟信号,该本地时钟信号控制状态机的输入信号的存储,同时控制状态和输出寄存器的更新(只有当其可用时),由此本地时钟信号不是周期性的。

23、在gals型状态机中,寄存器和存储电路由诸如触发器或锁存器之类的常见同步组件来实现。

24、然而,gals型状态机通常慢,因为本地时钟信号可以达到的最大频率受到输入信号存储电路中的亚稳态解析时间和状态机的下一状态指示的计算时间的限制。

25、需要克服开关转换器的已知有限状态机的全部或部分缺点。

技术实现思路

1、一个实施例提供了不是由专用异步组件实现和/或通过使用专用异步开发工具来实现的异步有限状态机。

2、例如,一个实施例提供了一种异步有限状态机,该异步有限状态机不包括状态寄存器,进而不包括提供状态机的下一状态的指示的组合电路。例如,这使得异步状态机能够比gals型状态机或由专用异步组件实现的异步状态机更快速地操作。

3、例如,一个实施例提供了与同步状态机相比具有降低的功耗的异步有限状态机。

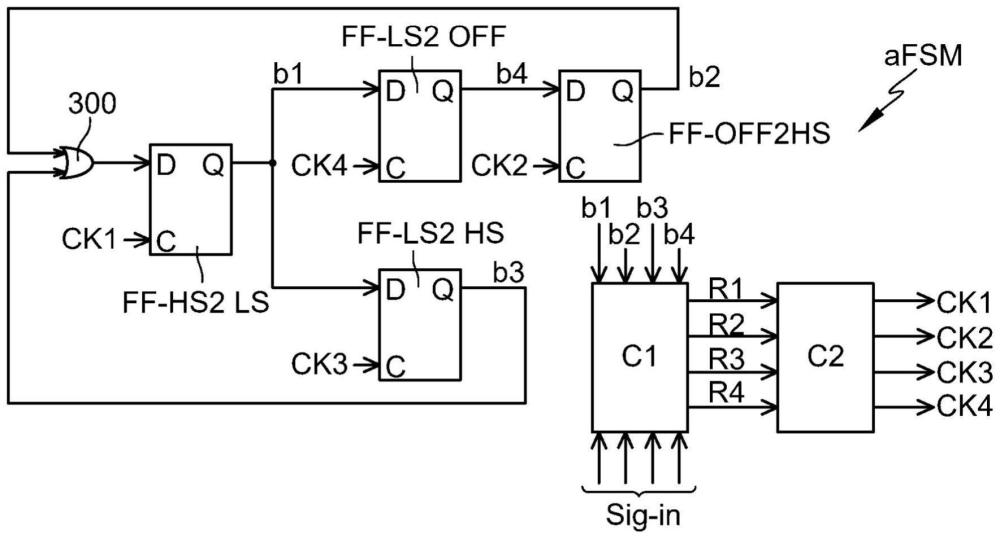

4、一个实施例提供了一种用于控制开关转换器的高压侧开关和低压侧开关的异步有限状态机,其中:所述状态机包括通过转变连接在一起的多种状态,每个转变由d触发器来实现;每个触发器具有输出端、数据输入端和控制输入端,所述输出端被配置为供应表示所述状态机的状态的比特,所述状态是由所述触发器实现的转变的到达状态,所述数据输入端被配置为接收表示由所述触发器实现的转变的初始状态的比特,所述控制输入端被配置为接收专用于所述触发器的第一二进制脉冲信号;第一组合电路,所述第一组合电路被配置为基于所述状态机的输入信号和由所述触发器的输出端供应的比特,针对每个转变,供应对应于所述转变并且指示是否需要实现所述转变的第二二进制信号;和第二电路,所述第二电路被配置为基于所述第二信号,在每次请求实现转变时并且在没有所述第一信号的脉冲的情况下,产生专用于实现所述转变的触发器的所述第一信号的脉冲和专用于其输出端被配置为向实现所述转变的触发器的所述数据输入端供应比特的每个触发器的所述第一信号的脉冲。

5、根据一个实施例,每个触发器被配置为使得专用于所述触发器的所述第一信号的每个脉冲的开始引起所述触发器的更新。

6、根据一个实施例,所述第二电路被配置为在每次请求实现转变时并且在没有所述第一信号的脉冲的情况下,仅产生专用于实现所述转变的触发器的所述第一信号的脉冲和专用于其输出端被配置为向实现所述转变的所述触发器的数据输入端供应比特的每个触发器的所述第一信号的脉冲。

7、根据一个实施例,所述第一组合电路不包括状态寄存器并且不包括用于存储所述状态机的输入信号的电路。

8、根据一个实施例,所述状态机包括:具有相同初始状态的至少一对转变;并且对于具有相同初始状态的每一对转变,所述第一组合电路包括互斥电路,该互斥电路被配置为基于所述状态机的多个所述输入信号,供应指示是否需要实现所述一对转变中的第一转变的第二二进制信号和指示是否需要实现所述一对转变中的第二转变的第二二进制信号,使得这些第二信号当中只有一个指示需要对应于该第二信号的转变。

9、根据一个实施例,所述第二电路包括:对于每个转变,与所述转变相关联的脉冲发生器,并且脉冲发生器被配置为:接收对应于所述转变的第二信号;并且在每次请求实现所述转变时且在没有所述第一信号的脉冲的情况下,产生输出脉冲;以及第三组合电路,所述第三组合电路被配置为基于所述发生器的输出脉冲来传送所述第一信号。

10、根据一个实施例,所述第三组合电路还被配置为仅当所述第一信号中的至少一个表现出脉冲时才供应处于第一电平的二进制信号,否则供应处于第二电平的二进制信号,每个脉冲发生器被配置为在所述二进制信号处于所述第一电平时不传送输出脉冲。

11、根据一个实施例,每个脉冲发生器被配置为在由所述脉冲发生器传送的每个输出脉冲处,使得实现与所述发生器相关联的转变的触发器的输出端的切换和/或实现与所述发生器相关联的转变的触发器的数据输入端的切换结束所述输出脉冲。

12、根据一个实施例,所述第二电路被配置为使得所述第一信号的每个脉冲具有由所述触发器的保持时间确定的相同的恒定持续时间。

13、根据一个实施例,所述第二电路被配置为使得在每次请求实现转变时,所述第二电路产生专用于实现所述转变的触发器的所述第一信号的脉冲以及专用于其输出端被配置为向实现所述转变的触发器的数据输入端供应比特的每个触发器的所述第一信号的脉冲,并且实现所述转变的触发器的输出端的切换和/或实现所述转变的触发器的数据输入端的切换结束所述脉冲。

14、根据一个实施例,所述状态机被配置为实现:第一阶段,所述第一阶段控制开关转换器的高压侧开关处于导通状态并且控制所述转换器的低压侧开关处于截止状态;第二阶段,所述第二阶段分别控制所述低压侧开关处于导通状态,所述高压侧开关处于截止状态;和第三阶段,所述第三阶段控制这两个开关处于截止状态,并且对于每种状态,所述状态机被配置为实现所述第一阶段、所述第二阶段和所述第三阶段中的一个。

15、根据一个实施例,所述状态机被配置为以连续导通模式和不连续导通模式交替地控制所述转换器,所述连续导通模式包括所述第二阶段、所述第三阶段和所述第一阶段的连续过程的一个或多个实现,并且所述连续导通模式包括所述第二阶段和所述第一阶段的连续过程的一个或多个实现。

16、根据一个实施例,所述触发器精确地包括第一触发器、第二触发器、第三触发器和第四触发器,所述第一触发器、第二触发器、第三触发器和第四触发器被配置为使得:所述第一触发器的数据输入端接收由所述第二触发器的输出端供应的比特和由所述第三触发器的输出端供应的比特;所述第三触发器和所述第四触发器的数据输入端各自接收由所述第一触发器的输出端供应的比特;并且所述第二触发器的数据输入端接收由所述第四触发器的输出端供应的比特。

17、根据一个实施例:由所述第二触发器的输出端供应的比特和由所述第三触发器的输出端供应的比特表示所述状态机的第一状态;由所述第一触发器的输出端供应的比特表示所述状态机的第二状态;由所述第四触发器的输出端供应的比特表示所述状态机的第三状态;并且所述状态机被配置为分别在所述第一状态、所述第二状态和所述第三状态中实现所述第一阶段、所述第二阶段和所述第三阶段。

18、一个实施例提供了一种开关转换器,所述开关转换器包括:高压侧开关,所述高压侧开关将连接节点耦接到被配置为接收电源电势的节点;低压侧开关,所述低压侧开关将所述连接节点耦接到被配置为接收参考电势的节点;电感器,所述电感器将所述连接节点耦接到所述转换器的输出端;以及诸如上述的状态机。

本文地址:https://www.jishuxx.com/zhuanli/20240914/296347.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表