具有提高的视频带宽的紧凑型多赫蒂放大器的制作方法

- 国知局

- 2024-09-19 14:26:53

本发明涉及一种放大器以及包括该放大器的多赫蒂(doherty)放大器。更具体地,本发明涉及一种射频(rf)功率放大器,该rf功率放大器配置成在介于0.1ghz至60ghz之间的频率下输出超过1瓦的功率。

背景技术:

1、通常,用于移动电信基站的rf功率放大器包括基于多赫蒂拓扑的功率放大器。在多赫蒂放大器中,首先通过多赫蒂分路器将待放大的信号分成主信号和峰值信号。然后,分别通过主放大器和峰值放大器对这些信号进行放大。主放大器通常偏置为ab类或b类,而峰值放大器通常偏置为c类。因此,对于低输入功率,将只有主放大器对信号进行放大,而在高输入功率下,主放大器和峰值放大器均会促成输出信号。

2、通过多赫蒂组合器将由主放大器和峰值放大器放大的信号组合成输出信号。通常,多赫蒂组合器包括阻抗逆变器,阻抗逆变器配置成在主放大器的输出处引入负载调制。更具体地,由于峰值放大器在低输入功率下关闭,因此由主放大器在低输入功率下看到的阻抗比在高输入功率下看到的阻抗高。可使用四分之一波长传输线或其电等效物来实现阻抗逆变器。负载调制使得多赫蒂放大器能够在低输入功率和高输入功率下均实现良好的效率。

3、已知各种替代的多赫蒂配置,例如并联多赫蒂或倒置多赫蒂,它们的不同之处在于阻抗逆变器连接的方式。此外,多赫蒂分路器通常会产生相位偏移,使得由主放大器和峰值放大器放大的信号在输出处同相相加。

4、图1a和图1b示出了本领域已知的放大器的电路。在这两个图中,示出了具有输出端子1和输入端子2的放大器的电路。作为有源元件,放大器包括具有特定输出电容cds和特定输入电容cgs的fet 3。为了在操作频率范围内减轻cds对rf性能的影响,提供输出谐振网络,输出谐振网络包括电感l3和输出匹配电容cout的串联连接。该网络配置成使得在fet 3的操作频率下或接近fet 3的操作频率时,网络表现为与cds谐振的电感。因此,cds与输出谐振网络的并联组合在fet 3的操作频率下或接近fet 3的操作频率时,起到开路的作用。此外,输出匹配电容cout防止直流(dc)路径接地,并在放大器的操作带宽内起到rf短路的作用。

5、fet 3的漏极还使用电感l7连接到输出端子1。在图1a中,示出了连接到输出端子1的dc偏置网络。该网络包括由电感ldfeed(ld馈送)形成的偏置线,输出端子1通过电感ldfeed连接到电压源vd。提供电容cdfeed(cd馈送),电容cdfeed在rf频率下提供短路。电感ldfeed通常使用四分之一波长传输线来实现。这条线将由cdfeed引起的rf频率下的短路转变成输出端子1处的开路。类似地,放大器的输入2连接到偏置网络,该偏置网络包括偏置源vg、由电感lgfeed(lg馈送)形成的偏置线(通常实现为四分之一波长传输线)和rf解耦电容cgfeed(cg馈送)。此外,形成包括输入匹配电容cin、电感l5和l4的输入匹配网络。

6、寄生电容cgs、cds分别在基带频率下与偏置线lgfeed和偏置线ldfeed谐振,偏置线lgfeed和偏置线ldfeed布置在其中实现fet 3的封装的外部。偏置线的电感无法自由选择,并因此谐振频率无法自由选择,因为这些线的长度对应于放大器的操作频率下的四分之一波长。随着寄生输入和输出电容增加和/或操作频率减小,谐振朝向晶体管的基带带宽下降。

7、输出基带谐振频率的影响在本领域中是众所周知的。解决该问题的已知解决方案是通过如图1b所示的包括电感l1、电阻r1和电容c1的谐振电路来消除由ldfeed和cds引入的基带谐振,应注意,偏置网络本身未在图1b中示出。通过使用谐振电路,可以在基带频率下获得平坦的低欧姆输出阻抗,从而使互调产物没有谐振。

8、由于lgfeed与cgs谐振,导致在设备的输入侧发生类似的谐振。在设备的输入侧,可使用rgfeed(rg馈送)从外部将谐振抑制到可接受的水平。然而,已发现:cgs的强非线性行为会导致被抑制的基带响应对输入信号激励vgs的调制。这会引起强的记忆效应,导致高侧和低侧之间由输入诱导的互调失真不对称,并对功率放大器的线性化能力提出挑战。图1b示出了解决该问题的已知解决方案。更具体地,包括电感l2、电阻r2和电容c2的另一谐振电路连接到fet 3的栅极。该网络抑制了在相对低频率下阻抗的振荡行为,否则该振荡行为会减小放大器的视频带宽。此外,图1b示出了包括电感l4至l6和电容cin、cin2的两级输入匹配网络,但是同样可使用单级输入匹配网络。

9、除了效率之外,功率放大器的稳定性也很重要。放大器的各个元件之间的电磁耦合,尤其是输入处的元件和输出处的元件之间的电磁耦合,通常会对稳定性产生不利影响。

10、本领域中对于实现具有相同或提高的输出功率和效率、但具有更小占地空间的功率放大器存在持续的需求。然而,减小占地空间会增加放大器在至少一些操作条件下不稳定的风险。

技术实现思路

1、本发明的目的在于提供一种对这种问题提出解决方案的放大器。

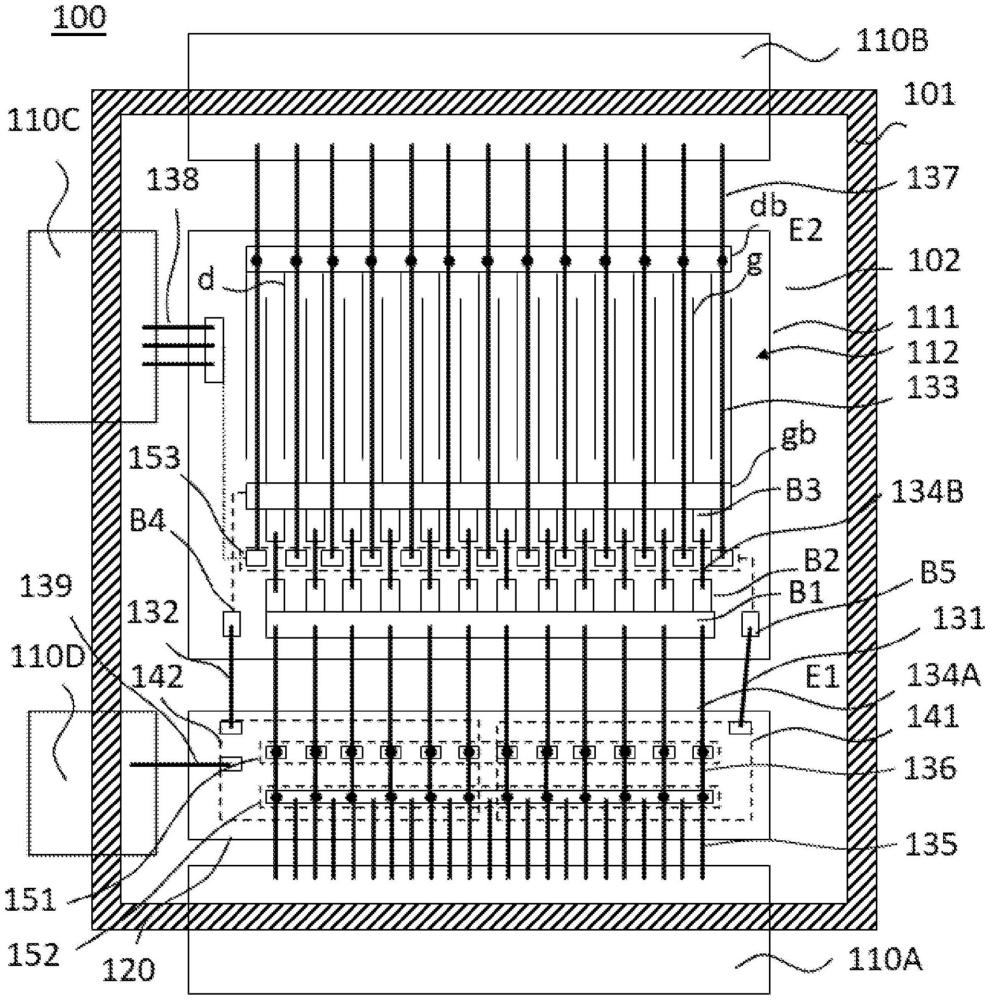

2、根据本发明,该目的使用如权利要求1所限定的放大器来实现,该放大器包括具有衬底的封装以及布置在该封装中的至少一个放大器单元。每个放大器单元包括输入端子、输出端子以及有源半导体管芯,大功率晶体管例如场效应晶体管fet集成在有源半导体管芯上。有源半导体管芯安装在衬底上并具有第一边缘和第二边缘,第一边缘布置在大功率晶体管和输入端子之间,第二边缘布置在大功率晶体管和输出端子之间。

3、每个放大器单元还包括输入匹配电容、输出匹配电容、第三电感以及第四电感,第三电感将大功率晶体管的输出连接到输出匹配电容,第四电感将大功率晶体管的输入连接到输入匹配电容。每个放大器单元额外包括输出谐振网络,输出谐振网络包括第一电感和第一电容的串联连接,并通过第三电感连接在地和大功率晶体管的输出之间。

4、根据本发明,每个放大器单元包括至少一个无源半导体管芯,至少一个无源半导体管芯安装在衬底上、位于有源半导体管芯和输入端子之间,其中,输入匹配电容和第一电容集成在至少一个无源半导体管芯上,并且其中,输出匹配电容集成在有源半导体管芯上、相比第二边缘更靠近第一边缘。

5、申请人发现:上文提到的配置使得电连接在放大器的输出附近的第一电容能够靠近放大器的输入的元件布置,但不会降低放大器的稳定性。

6、为了进一步提高放大器的稳定性,第三电感可以与第四电感电磁耦合,以至少部分地对第一电感和第四电感之间的电磁耦合进行补偿。这种耦合可能是由于第一电容和第四电感所连接到的输入匹配电容靠近放置而引起,从而导致放大器的输入电路和输出电路之间发生耦合。申请人发现:可通过确保第三电感和第四电感之间足够的电磁耦合,来减轻这种耦合。例如,这些电感可以彼此靠近布置,且可以以至少部分平行的方式或至少部分重叠的方式延伸。

7、为了提高放大器的紧凑性,输入匹配电容和第一电容可集成在相同的无源半导体管芯上。

8、输出谐振网络还可包括与第一电感和第一电容串联布置的第一电阻。第一电阻优选地与第一电容集成在相同的无源半导体管芯上,和/或第一电阻至少部分地由第一电容的电阻形成。

9、放大器还可包括输入谐振网络,输入谐振网络包括第二电感和第二电容的串联连接,并连接在大功率晶体管的输入和地之间。输入谐振网络还可包括与第二电感和第二电容串联布置的第二电阻,其中,第二电阻优选地与第二电容集成在相同的无源半导体管芯上,和/或第二电阻至少部分地由第二电容的电阻形成。附加地或替代地,第一电容和第二电容可集成在相同的无源半导体管芯上。

10、第一电阻和第二电阻可配置成抑制在谐振网络中发生的任何谐振和/或由于谐振网络而导致的任何谐振。替代地或附加地,第一电阻和/或第二电阻可使用沉积在相关无源半导体管芯上的电阻材料薄层来形成。

11、第一电容和第二电容中的每一个可包括相应的非接地端子和接地端子,其中,第一电容的接地端子和第二电容的接地端子电连接和/或一体地连接,并且其中,第一电容由第一深沟槽电容形成,和/或其中,第二电容由第二深沟槽电容形成。

12、通常,深沟槽电容包括多个沟槽,每个沟槽的内壁由第一金属层覆盖。沟槽包括布置在第一金属层和第二金属层之间的介电层。

13、为了实现上文提到的第一电容和第二电容,可使用深沟槽电容,深沟槽电容还包括第一互连和第二互连,第一互连用于电连接第一组沟槽的第二金属层,第二互连用于电连接第二组沟槽的第二金属层,第二组不包括第一组的沟槽。在这种情况下,第一互连连接到第一电容的非接地端子,和/或至少部分地形成第一电容的非接地端子,且第二互连连接到第二电容的非接地端子,和/或至少部分地形成第二电容的非接地端子。此外,至少一个无源半导体管芯的半导体衬底可以是导电衬底,使得布置在沟槽中的第一金属层和衬底之间能够实现电连接。

14、放大器单元还可包括输入导体,输入匹配电容通过输入导体连接到输入端子,输入导体包括多条输入键合线。此外,放大器单元还可包括第二输入匹配电容以及形成中间电感的多条中间键合线,第二输入匹配电容优选地与输入匹配电容布置在相同的无源半导体管芯上,其中,输入键合线电连接输入端子和第二输入匹配电容,并且其中,中间键合线电连接第二输入匹配电容和输入匹配电容。

15、输入匹配电容可由第一金属-绝缘体-金属电容形成,和/或,第二输入匹配电容可由第二金属-绝缘体-金属电容形成,和/或,输出匹配电容可由第三金属-绝缘体-金属电容形成。

16、放大器单元可包括将大功率晶体管的输出连接到输出端子的输出电感。该输出电感可包括多条输出键合线。

17、第一电感可包括一条或多条第一键合线,一条或多条第一键合线电连接输出匹配电容和第一电容。该连接可以是直接连接,其中,一条或多条第一键合线物理地连接到第一电容的非接地端子。替代地,由于第一电阻布置在一条或多条第一键合线和第一电容的非接地端子之间,因此该连接可以是间接连接。

18、类似地,第二电感可包括一条或多条第二键合线,一条或多条第二键合线电连接大功率晶体管的输入和第二电容。该连接可以是直接连接,其中,一条或多条第二键合线物理地连接到第二电容的非接地端子。替代地,由于第二电阻布置在一条或多条第二键合线和第二电容的非接地端子之间,因此该连接可以是间接连接。

19、第四电感可包括多条第四键合线,多条第四键合线电连接大功率晶体管的输入和输入匹配电容。第四电感的一部分可配置成与第三电感的一部分电磁耦合,以至少部分地对一条或多条第一键合线和一条或多条第四键合线之间的电磁耦合进行补偿。

20、第三电感可包括多条第三键合线。在这种情况下,多条第四键合线可包括第一组第四键合线和第二组第四键合线,第一组第四键合线在有源半导体管芯上的第一键合焊盘组件和输入匹配电容之间延伸,以及第二组第四键合线在第二键合焊盘组件和第三键合焊盘组件之间延伸。第一键合焊盘组件可与第二键合焊盘组件一体地形成,和/或第一键合焊盘组件可电连接到第二键合焊盘组件,第一键合焊盘组件可布置成比第二键合焊盘组件和第三键合焊盘组件更靠近第一边缘。此外,第二键合焊盘组件可布置成比第三键合焊盘组件更靠近第一边缘,第二组第四键合线可与多条第三键合线相邻且基本上平行于多条第三键合线延伸。

21、可实现第四键合线和第三键合线之间的耦合的另一种方式是:第四键合线在有源半导体管芯上的第一键合条组件和输入匹配电容之间延伸,以及第三键合线在大功率晶体管的输出和第二键合条组件之间延伸。在这种情况下,第二键合条组件可布置成比第一键合条组件更靠近第一边缘。

22、在上文描述的两种配置中,第一键合焊盘组件、第二键合焊盘组件和/或第三键合焊盘组件可以彼此独立地包括多个间隔开的键合焊盘或者一个或多个键合条。

23、可实现第四键合线和第三键合线之间的耦合的又一种方式是:第三电感包括第三耦合部分,且第四电感包括第四耦合部分,其中,第三耦合部分和第四耦合部分作为耦合线集成在有源半导体管芯上。耦合线的示例是耦合传输线,例如宽边耦合线或边缘耦合线。

24、每个放大器单元可包括第一视频端子,第一视频端子电连接到输出匹配电容,优选地使用一条或多条键合线电连接到输出匹配电容。附加地或替代地,每个放大器单元可包括第二视频端子,第二视频端子电连接到第二电容,优选地使用一条或多条键合线电连接到第二电容。

25、至少一个放大器单元可包括一对放大器单元,这一对放大器单元的输入端子相邻地布置,且这一对放大器单元的输出端子相邻地布置。这些放大器单元在饱和输出功率、偏置、布局等方面可以相同或不相同。

26、这一对放大器单元的输入匹配电容可以电连接,例如使用一条或多条键合线来电连接。类似地,这一对放大器单元的第二输入匹配电容可以电连接,例如使用一条或多条键合线来电连接。

27、该封装可包括基于引线框架的封装、模制封装、双边扁平无引线封装、或四边扁平无引线封装。大功率晶体管可以是硅基横向扩散金属氧化物半导体晶体管或氮化镓基场效应晶体管。

28、根据另一方面,本发明提供一种多赫蒂放大器,该多赫蒂放大器包括印刷电路板、安装在印刷电路板上的主放大器和峰值放大器。此外,多赫蒂放大器包括多赫蒂分路器,多赫蒂分路器用于将输入rf信号分成待馈送到主放大器的主信号和待馈送到峰值放大器的峰值信号。多赫蒂放大器还包括至少一个如上文所限定的放大器,至少一个放大器安装在印刷电路板上,其中,至少一个放大器的放大器单元共同形成主放大器和/或峰值放大器。多赫蒂放大器还包括多赫蒂组合器,多赫蒂组合器用于组合由主放大器放大的主信号以及由峰值放大器放大的峰值信号。至少一个放大器可包括单个放大器,单个放大器的一个放大器单元形成主放大器,单个放大器的另一放大器单元形成峰值放大器。因此,在这种情况下,主放大器和峰值放大器在相同的封装中实现。

29、在至少一个放大器包括第一视频引线的情况下,多赫蒂放大器还可包括连接在第一视频引线和地之间的dc解耦电容。

本文地址:https://www.jishuxx.com/zhuanli/20240919/298153.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表