一种CPLD芯片GPIO资源池化方法与流程

- 国知局

- 2024-10-09 16:04:18

本发明涉及gpio资源池化,特别是一种cpld芯片gpio资源池化方法。

背景技术:

1、随着当前物联网、大数据和ai技术的快速发展,服务器发挥的作用越来越重要,服务器的功能也越来越强大,cpld作为服务器主板上的主要芯片,为了实现越来越强大的功能,bmc/pch/cpld的设计也越来越复杂。

2、尤其是cpld,作为复杂可编程逻辑器件,其优势在于所有的管脚都可以当作gpio使用,而不是必须定义为专用功能,因此,cpld可以跟bmc/pch/cpu/内存,以及其他众多芯片或器件相连,来实现想要的功能。

3、首先,现有的cpld的每个bank的gpio都是固定好的,不能随cpld外围电路设计进行变更,这样会对cpld的gpio利用率造成影响,其次,在目前的主板设计中,bmc/pch/cpu的管脚都有特定的功能,因此这些芯片周围的走线都基本上固定的,基于此,很大程度上,cpld管脚的随意分配与调换给layout缓解了很大的难度。

技术实现思路

1、鉴于上述现有的cpld芯片gpio资源池化方法中存在的问题,提出了本发明。

2、因此,本发明所要解决的问题在于cpld芯片的gpio利用率低和layout布局布线难。

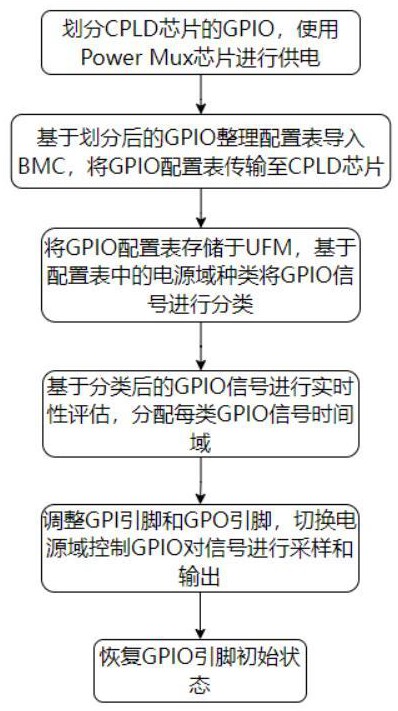

3、为解决上述技术问题,本发明提供如下技术方案:一种cpld芯片gpio资源池化方法,其包括,划分cpld芯片的gpio,使用power mux芯片进行供电;

4、基于划分后的gpio整理配置表导入bmc,将gpio配置表传输至cpld芯片;将gpio配置表存储于ufm,基于配置表中的电源域种类将gpio信号进行分类;基于分类后的gpio信号进行实时性评估,分配每类gpio信号时间域;调整gpi引脚和gpo引脚,切换电源域控制gpio对信号进行采样和输出;恢复gpio引脚初始状态。

5、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述划分cpld芯片的gpio,使用power mux芯片进行供电包括,

6、将cpld芯片上的goip划分为两个部分,第一部分为bank8,连接i2c通信管脚和power mux芯片切换管脚,使用3.3v电压供电;

7、使用power mux芯片接受不同电压的电源输入,统一输出vccio电源;

8、第二部分为bank1-7,使用统一输出后的vccio电源供电,兼容1.0v、1.1v、1.8v、2.5v和3.3v电源域。

9、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述基于划分后的gpio整理配置表导入bmc,将配置表传输至cpld芯片包括,

10、根据硬件布局图和实际连接关系,整理gpio配置表;

11、将gpio配置表转换为按照vccio分类的格式,并使用i2c接口将转换格式后的gpio配置表从bmc传输到cpld芯片;

12、cpld芯片接收gpio配置表并解析gpio配置表。

13、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述将gpio配置表存储于ufm包括,

14、在cpld芯片出厂配置过程中,bmc将gpio配置表通过i2c接口传输至cpld芯片,并存储于cpld芯片上的ufm中;

15、cpld芯片上电工作时,自动加载ufm中的gpio配置表,并基于gpio配置表进行gpio资源配置。

16、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述基于gpio配置表中的电源域种类将gpio进行分类包括,

17、bmc读取未经整理的gpio配置表,包括每个gpio的bank编号、引脚编号、引脚名称和对应的vccio电压;

18、根据不同的vccio电压将配置表数据分为“3.3v/1.0v/1.1v/1.8v/2.5v”五类,并生成新的配置表。

19、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述基于分类后的gpio信号进行实时性评估包括,

20、查阅硬件规格书和系统设计文档,获取每个gpio信号的功能描述;

21、基于每个gpio信号的功能和用途,使用优先级矩阵法,将gpio信号按实时性需求分为高实时性信号和低实时性信号;

22、所述高实时性信号指需要快速响应的信号,包括3.3v信号和2.5v信号;

23、所述低实时性信号指需要较快响应的信号,包括1.0v信号、1.1v信号和1.8v信号;

24、所述gpio信号中的3.3v、1.0v、1.1v、1.8v和2.5v信号分别是关键控制信号、cpu控制信号、内存控制信号、外围设备通信信号和数据传输信号。

25、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述分配每类gpio信号时间域包括,

26、设定总时间周期为5ms,将总时间周期划分为多个时间段;

27、根据功能分析和实时性评估结果,使用时间调度算法给不同类型信号分配时间周期,包括3.3v信号占用2ms、1.0v信号占用0.5ms、1.1v信号占用0.5ms、1.8v信号占用1ms以及2.5v信号占用1ms。

28、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述调整gpi引脚和gpo引脚包括,

29、在切换电源域vccio之前,使用cpdl芯片将不属于当前电源域vccio的gpi引脚调整为高阻态;

30、使用cpld芯片锁定不属于当前电源域vccio的gpo引脚的输出状态。

31、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述切换电源域并对gpi和gpo信号进行采样和控制包括,

32、使用分时复用技术,基于不同信号对应的时间段,在每个gpio信号的时间段开始时,cpld芯片向power mux芯片发送控制信号并切换至该gpio信号对应的vccio;

33、在当前电源域的时间段内,使用cpld芯片对当前电源域的gpi信号进行采样,读取相应引脚的电压值,并锁定当前电源域的gpo信号,设定相应引脚的电压值。

34、作为本发明所述cpld芯片gpio资源池化方法的一种优选方案,其中:所述恢复gpio引脚初始状态包括,

35、在切换到下一个电源域之前,解除当前电源域的gpi引脚高阻值设置和gpo引脚的输出锁定状态;

36、重复执行“调整gpi引脚和gpo引脚,切换电源域控制gpio对信号进行采样和输出以及恢复gpio引脚初始状态”操作。

37、本发明有益效果为:本发明提出了一种cpld芯片gpio资源池化方法,通过动态调整cpld芯片各个bank的vccio供电情况,使cpld芯片的所有gpio资源池化,可以从硬件链路上随意连接到不同电源域的芯片上,从而避免因vccio不同引起的gpio不能跨bank使用的情形,进而解决资源浪费问题以及layout时无法随意换pin的问题。

本文地址:https://www.jishuxx.com/zhuanli/20240929/311552.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。