一种17T抗辐照SRAM存储单元电路与工作方法与流程

- 国知局

- 2024-10-09 15:23:29

本发明涉及集成电路设计,具体涉及一种17t抗辐照sram存储单元电路与工作方法。

背景技术:

1、在辐射环境中,电子器件会因外部高能带电粒子(如中子、质子、α粒子或重离子)的单次作用而产生瞬时或永久性故障或性能变化。当入射粒子与半导体物质相互作用时,会引发电离效应,即从原子中释放出电子和空穴,这可能导致sram等具有存储功能的电子元件中存储数据发生翻转,这种现象也被称为单粒子翻转效应。sram作为中央处理器(cpu)与内部存储器之间的桥梁,在通信、航空航天、医疗等领域广泛应用,目前已经提出了多种具有抗辐照能力的sram设计,但这些设计在稳定性和功耗之间仍存在一些不均衡的问题。

2、随着晶体管特征尺寸的不断减小,进一步降低电源电压和节点电容,在太空等复杂辐射环境中芯片极易受到辐射影响而发生单粒子效应。目前静态随机存储器在微处理器中的面积达到了整体30%~60%,sram的稳定性以及功耗对整个芯片来说十分重要,尽管已经提出了多种抗辐照存储单元加固设计,但功耗和稳定性上面仍会存在某一方面不足。

3、申请公开号为cn114496026a的发明专利申请公开了了一种基于极性加固技术的抗辐照sram存储电路,包括八个nmos晶体管和六个pmos晶体管,pmos晶体管p3和p4交叉耦合,nmos晶体管n3、n4和pmos晶体管p1、p2作为上拉管,nmos晶体管n1、n2、n5、n6作为下拉管;两个主存储节点q与qn通过nmos晶体管n8与n7分别与第一位线bl和blb连接,两个冗余存储节点s1与s0通过pmos晶体管p6与p5分别与第一位线bl和blb连接,nmos晶体管n7、n8由第一字线wl控制,pmos晶体管p5、p6由第一字线wlb控制。对比文件所述电路能够提高sram存储单元的稳定性,并提高单元抗单粒子翻转能力;但对比文件单个节点仍存在翻转的可能,而翻转后很容易对其他节点产生影响,同时,对比文件的通用性较差,需要更改经典管尺寸来阻止部分出现错误节点的传播,功耗消耗较大。

技术实现思路

1、本发明所要解决的技术问题在于现有抗辐照sram存储电路存在功耗较大、稳定性较差的问题。

2、本发明是通过以下技术方案解决上述技术问题的:

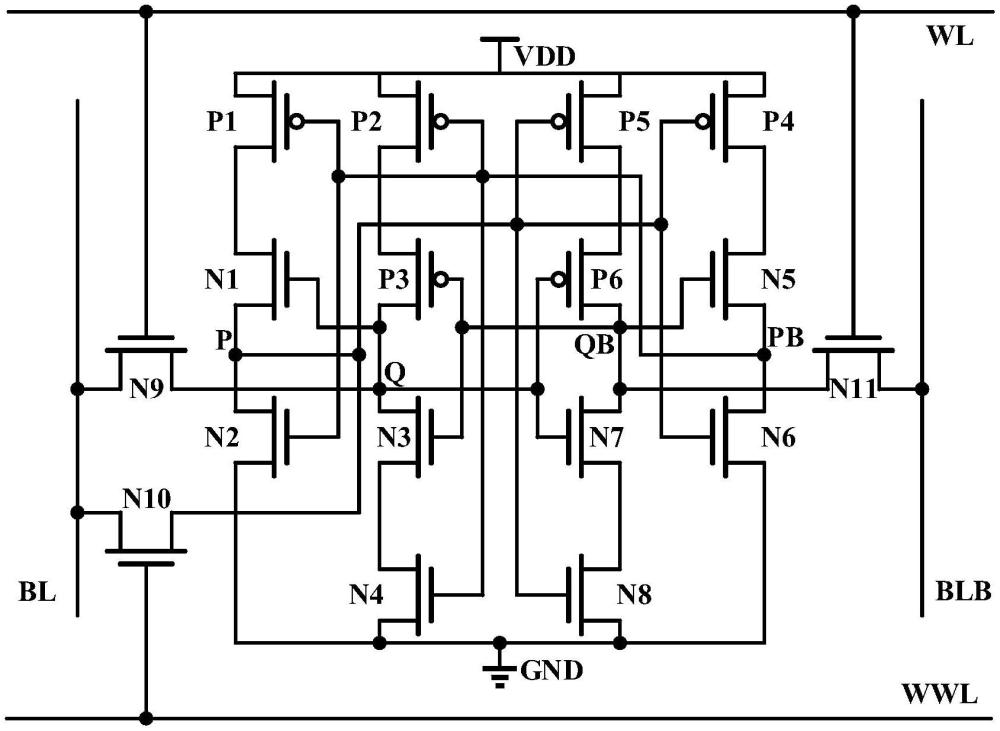

3、一种17t抗辐照sram存储单元电路,包括:6个pmos晶体管、11个nmos晶体管,所述6个pmos晶体管依次记为p1-p6,所述11个nmos晶体管依次记为n1-n11,其中:

4、nmos晶体管n1的源极与nmos晶体管的n2的漏极、nmos晶体管n10的漏极、nmos晶体管n6的栅极、nmos晶体管n8的栅极、pmos晶体管p4的栅极、pmos晶体管p5的栅极连接;nmos晶体管n1的栅极与nmos晶体管n3的漏极、nmos晶体管n9的漏极、nmos晶体管n7的栅极、pmos晶体管p3的漏极、pmos晶体管p6的栅极连接;nmos晶体管n1的漏极与pmos晶体管p1的漏极连接;nmos晶体管n2的源极与nmos晶体管n4的源极、nmos晶体管n6的源极、nmos晶体管n8的源极连接接gnd;nmos晶体管n2的栅极与nmos晶体管n4的栅极、nmos晶体管n5的源极、nmos晶体管n6的漏极、pmos晶体管p1的栅极、pmos晶体管p2的栅极连接;nmos晶体管n3的源极与nmos晶体管n4的漏极连接;nmos晶体管n3的栅极与nmos晶体管n5的栅极、nmos晶体管n7的漏极、nmos晶体管n11的漏极、pmos晶体管p3的栅极、pmos晶体管p6的漏极连接;nmos晶体管n5的漏极与pmos晶体管p4的漏极连接;nmos晶体管n7的源极与nmos晶体管n8的漏极连接;nmos晶体管n9的源极与nmos晶体管n10的源极、第一位线bl连接;nmos晶体管n9的栅极与nmos晶体管n11的栅极、第一字线wl连接;nmos晶体管n10的栅极与第二字线wwl连接;nmos晶体管n11的源极与第二位线blb连接;pmos晶体管p1的源极与pmos晶体管p2的源极、pmos晶体管p4的源极、pmos晶体管p5的源极连接接电源vdd;pmos晶体管p2的漏极与pmos晶体管p3的源极连接;;pmos晶体管p5的漏极与pmos晶体管p6的源极连接。

5、本发明所提出单元采用堆叠结构,降低了电路的泄漏电流,大幅度降低了电路功耗,存储结构采用完全对称的两个稳定结构相互锁存,增加了电路的稳定性。同时上述设计使得本发明在实现任意单节点翻转的自恢复的同时,具有较低的功耗,进一步的减少功耗。并且本发明采用极性设计的加固方式,使得单元只存在三个敏感节点,从而减少了节点的翻转概率,提高单元整体的稳定性。本发明面对任意单节点的翻转,可以有效的阻碍错误的传播,最后恢复错误节点,使得本发明具有单节点自恢复的能力。

6、优选的,在nmos晶体管n1的源极、nmos晶体管的n2的漏极、nmos晶体管n10的漏极、nmos晶体管n6的栅极、nmos晶体管n8的栅极、pmos晶体管p4的栅极、pmos晶体管p5的栅极连接所在线路上设有节点p。

7、优选的,在nmos晶体管n2的栅极、nmos晶体管n4的栅极、nmos晶体管n5的源极、nmos晶体管n6的漏极、pmos晶体管p1的栅极、pmos晶体管p2的栅极连接所在线路上设有节点pb。

8、优选的,在nmos晶体管n1的栅极、nmos晶体管n3的漏极、nmos晶体管n9的漏极、nmos晶体管n7的栅极、pmos晶体管p3的漏极、pmos晶体管p6的栅极连接所在线路上设有节点q。

9、优选的,在nmos晶体管n3的栅极、nmos晶体管n5的栅极、nmos晶体管n7的漏极、nmos晶体管n11的漏极、pmos晶体管p3的栅极、pmos晶体管p6的漏极连接所在线路上设有节点qb。

10、一种17t抗辐照sram存储单元电路工作方法,在写操作阶段:

11、当对存储单元进行写‘1’操作时,此时第一位线bl被预充到高电平‘1’,第二位线blb被放电低电平‘0’,当第一字线wl与第二字线wwl变为高电平时,写操作开始,三个传输nmos晶体管n9、nmos晶体管n10和nmos晶体管n11均导通,节点q和节点p被写入‘1’,节点qb被写入‘0’,节点pb处于不定态,此时nmos晶体管n5的栅极接低电平,pmos晶体管p4的栅极接高电平,两者均不导通,nmos晶体管n6栅极接节点p为高电平,因此该晶体管处于导通状态,节点pb被写入‘0’,此时四个节点均有相应的值,数据写入操作完成。

12、在保持阶段:

13、第一位线bl和第二位线blb会被预充到高电平,此时第一字线wl和第二字线wwl处于低电平,nmos晶体管n9、nmos晶体管n10、nmos晶体管n11不导通,节点与位线被隔开;假设此时存储的值为‘1’,即节点q和p为‘1’,节点qb和pb为‘0’,节点p通过nmos晶体管n6驱动节点pb,节点p和节点q通过pmos晶体管p5、pmos晶体管p6共同驱动节点qb,节点qb和节点pb又通过pmos晶体管p2、pmos晶体管p3共同驱动节点q,节点pb与节点q分别通过pmos晶体管p1和nmos晶体管n1驱动节点p,这样电路整体相互锁存,相互驱动,构成一条完整的反馈回路,电路所存储的值不会丢失,所有节点均处于一个稳定的状态。

14、在读取阶段:

15、假设存储的数据为‘1’,在正式进行读操作前,第一位线bl和第二位线blb会被预充至高电平,当第一字线为wl变为高电平,第二字线wwl变为低电平时,nmos晶体管n9、nmos晶体管n11导通,存储的是数据为‘1’,第一位线bl的电压不会出现变化,第二位线blb通过nmos晶体管n11与节点qb连接,此时第二位线blb被放电,使两条位线出现电压差,随着放电时间的增加,电压差不断变大,直到被灵敏放大器检测,此时电路存储数据‘1’被读出,读操作完成。

16、一种电子设备,包括存储器以及处理器,所述存储器用于存储支持处理器执行上述一种17t抗辐照sram存储单元电路工作方法的程序,所述处理器被配置为用于执行所述存储器中存储的程序。

17、一种存储介质,存储介质上存储有计算机程序,所述计算机程序被处理器运行时执行上所述一种17t抗辐照sram存储单元电路工作方法的步骤。。

18、本发明的优点在于:

19、本发明所提出单元采用堆叠结构,降低了电路的泄漏电流,大幅度降低了电路功耗,存储结构采用完全对称的两个稳定结构相互锁存,增加了电路的稳定性。同时上述设计使得本发明在实现任意单节点翻转的自恢复的同时,具有较低的功耗,进一步的减少功耗。并且本发明采用极性设计的加固方式,使得单元只存在三个敏感节点,从而减少了节点的翻转概率,提高单元整体的稳定性。本发明面对任意单节点的翻转,可以有效的阻碍错误的传播,最后恢复错误节点,使得本发明具有单节点自恢复的能力。

本文地址:https://www.jishuxx.com/zhuanli/20241009/308573.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

硬盘存储设备的制作方法

下一篇

返回列表