一种存储器及其操作方法与流程

- 国知局

- 2024-10-09 14:45:20

本申请实施例涉及半导体,特别涉及一种存储器。

背景技术:

1、为了提升存储器的良品率,存储器芯片设计中会使用冗余技术(例如行冗余技术):当在测试中发现芯片的某一根字线失效时,可将其对应的地址重定向至一个冗余的字线,从而减少因字线失效导致的良品率下降。失效的地址会通过熔丝或反熔丝等非易失性方式存储至芯片,在激活命令到来时,会将命令携带的行地址与熔丝或反熔丝中的地址进行比较,以判断该地址是否需要修复,但是这个比较的过程需要一定的时间。

技术实现思路

1、本申请实施例提供一种存储器,至少有利于改善行冗余电路的时序,提升存储器的良品率和优品率。

2、根据本申请一些实施例,本申请实施例一方面提供一种存储器,其特征在于,包括:

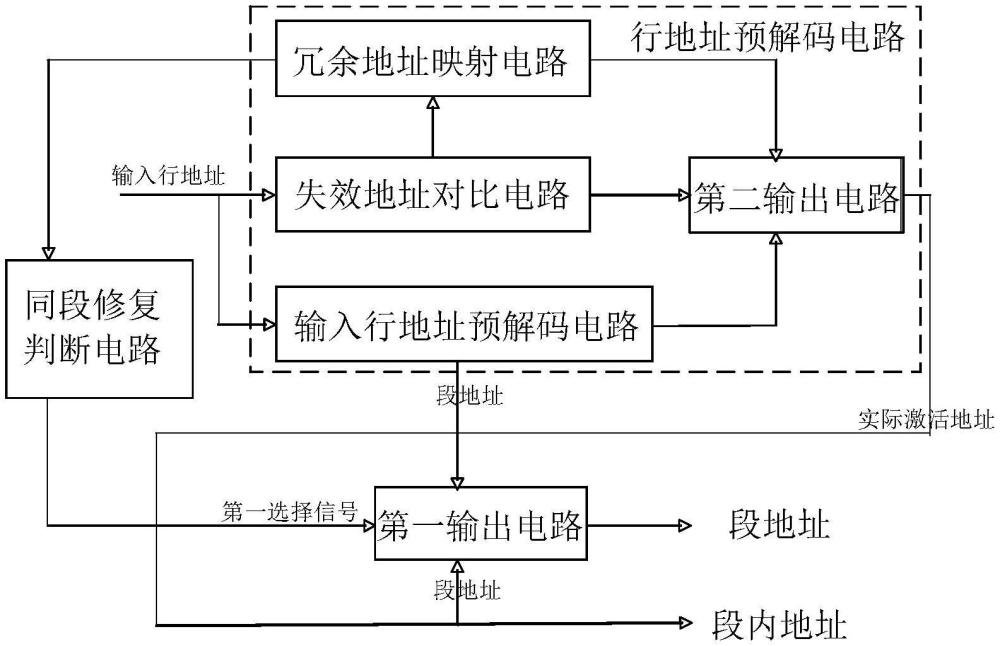

3、行地址预解码电路,被配置为接收输入行地址,并对所述输入行地址进行预解码;

4、同段修复判断电路,被配置为判断失效地址与替换该失效地址的冗余地址是否处于同一存储段;

5、第一输出电路,连接所述同段修复判断电路和所述行地址预解码电路,被配置为基于所述同段修复判断电路的判断结果,在所述失效地址及替换该失效地址的冗余地址处于同一存储段时,从所述行地址预解码电路接收对所述输入行地址预解码而得到的段地址,并输出所述段地址;

6、感测放大器,被配置为响应于所述段地址,对所述段地址指向的存储段进行阈值电压补偿操作。

7、根据本申请一些实施例,本申请实施例另一方面还提供一种存储器的操作方法,其特征在于,包括:

8、判断失效地址与替换该失效地址的冗余地址是否处于同一存储段;

9、当失效地址与替换该失效地址的冗余地址处于同一存储段时,执行以下操作:

10、接收输入行地址;

11、对输入行地址进行预解码,得到该输入行地址的段地址;

12、对所述段地址指向的存储段进行阈值电压补偿操作;

13、当失效地址与替换该失效地址的冗余地址不处于同一存储段时,执行以下操作:

14、接收输入行地址;

15、对输入行地址进行预解码,得到该输入行地址的段地址;同时,将输入行地址与失效地址进行比较,判断是否以冗余地址替换所述输入行地址;

16、根据比较结果,输出对输入行地址预解码得到的段地址或冗余地址的段地址作为实际激活地址的段地址;

17、对所述实际激活地址的段地址指向的存储段进行阈值电压补偿操作。

18、本申请实施例提供的技术方案至少具有以下优点:

19、减少字线的激活过程中冗余技术所花费的时间,有助于减小trcd(ras tocasdelay,行地址到列地址之间的延迟),trcd是激活存储器的一行与存取耦合到经激活行的存储器单元的一列中的存储器单元之间所需的最小时钟数,减小trcd可为存储器装置提供更多余量。

20、对于失效地址存在一定规律的芯片,根据冗余资源的设置与分配方式,设置条件判断电路,对于符合条件的芯片,可以减少地址比较所需要等待的时间,改善行冗余电路的时序,减小最小trcd,改善芯片时序。

技术特征:1.一种存储器,其特征在于,包括:

2.根据权利要求1所述的存储器,其特征在于,所述存储器包括存储阵列,所述存储阵列包括多个存储段和多个感测放大器阵列,所述存储段和所述感测放大器阵列沿第一方向交替排布,一个感测放大器阵列对其沿第一方向相邻的两侧的存储段进行感测放大;

3.根据权利要求1所述的存储器,其特征在于,所述存储器包括行解码器,所述行解码器包括所述行地址预解码电路;其中,所述行地址预解码电路包括输入行地址预解码电路、失效地址对比电路、冗余地址映射电路和第二输出电路;

4.根据权利要求3所述的存储器,其特征在于,所述第一输出电路连接所述同段修复判断电路、输入行地址预解码电路和第二输出电路,其中,

5.根据权利要求1所述的存储器,其特征在于,所述存储器中包括多个失效地址和多个冗余地址,所述多个失效地址和所述多个冗余地址一一对应;其中,

6.根据权利要求5所述的存储器,其特征在于,所述同段修复判断电路,包括至少一个比较电路、至少一个或逻辑电路、使能电路、初始化电路、保持电路,其中,

7.一种存储器的操作方法,其特征在于,包括:

8.根据权利要求7所述的操作方法,其特征在于,在对存储器上电时,进行所述判断失效地址与替换该失效地址的冗余地址是否处于同一存储段的操作。

9.根据权利要求7所述的操作方法,其特征在于,所述当失效地址与替换该失效地址的冗余地址处于同一存储段时,执行以下操作:接收输入行地址;对输入行地址进行预解码,得到该输入行地址的段地址;对所述段地址指向的存储段进行阈值电压补偿操作,具体为:

10.根据权利要求7所述的操作方法,其特征在于,所述存储器包括多个失效地址和多个冗余地址,所述失效地址和所述冗余地址一一对应,

技术总结本申请实施例涉及存储器领域,提供一种存储器,包括:行地址预解码电路,被配置为接收输入行地址,并对所述输入行地址进行预解码;同段修复判断电路,被配置为判断失效地址与替换该失效地址的冗余地址是否处于同一存储段;第一输出电路,连接所述同段修复判断电路和所述行地址预解码电路,被配置为基于所述同段修复判断电路的判断结果,在所述失效地址及替换该失效地址的冗余地址处于同一存储段时,从所述行地址预解码电路接收对所述输入行地址预解码而得到的段地址,并输出所述段地址;感测放大器,被配置为响应于所述段地址,对所述段地址指向的存储段进行阈值电压补偿操作。技术研发人员:陈晗受保护的技术使用者:长鑫科技集团股份有限公司技术研发日:技术公布日:2024/9/29本文地址:https://www.jishuxx.com/zhuanli/20241009/306382.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表