一种半导体器件结构及其制造方法与流程

- 国知局

- 2024-10-15 09:33:18

本发明涉及半导体集成电路工艺,尤其涉及一种半导体器件结构及其制造方法。

背景技术:

1、随着半导体超大规模集成电路的发展,现有的技术工艺已经接近物理极限。在对电子产品进一步小型化、多功能化的目的驱动下,其他新的技术、新的材料、新的科技被探索出来。三维堆叠技术就是其中之一。三维堆叠技术将硅片通过键合技术堆叠起来,实现三维层面上的金属互连结构,可以减少互连距离,提高传输速度,减小器件体积,并提供了异质结构集成的可能性。

2、现有的三维堆叠技术,其关键工艺之一为硅通孔工艺。现有的硅通孔工艺集成方案主要有3种,包括硅通孔先制作工艺,硅通孔后制作工艺,和背面硅通孔工艺。其中,硅通孔先制作工艺是在常规有源区形成时,在两个相邻的有源区之间,通过对硅衬底进行光刻、刻蚀和沉积等工艺,形成硅通孔结构。硅通孔后制作工艺是在常规后道工艺之后,从硅衬底正面对介质层及硅衬底一起进行刻蚀,形成硅通孔结构。但以上述两种工艺形成的硅通孔,最终还需要从硅衬底背面引出,该工艺通常称为硅通孔背面露出工艺。背面硅通孔工艺会将完成后道工艺的硅衬底翻面与载片进行键合及对硅衬底背面减薄,然后从硅衬底背面进行光刻、刻蚀、沉积等工艺,形成硅通孔结构。

3、目前的所有硅通孔集成方案中,都对硅通孔结构的深宽比有一定要求,但通常深宽比不超过10:1。如果要实现更高深宽比的硅通孔,比如20:1的深宽比,往往会遇到一系列的工艺问题,主要包括:在刻蚀方面,在一定的开口尺寸下,越往通孔深处刻蚀,刻蚀气体能到达通孔底部的量和速度都会变小,使得位于深处的通孔部分容易出现各种问题,如侧壁表面粗糙(长草)、尺寸发生变化等,同时,刻蚀时间也会成倍上涨;在填充方面,深宽比越高,对铜的填充要求就越高,工艺难度也越大,且很容易在通孔底部出现填充空洞等问题。

4、综合各种工艺因素,硅通孔深宽比在正常工艺下是受限的。但对于一些应用来说,10:1的硅通孔深宽比并不能有效满足需求。如果通过增大硅通孔的宽度尺寸的方式来降低工艺难度以增加深宽比,则过大的硅通孔宽度尺寸会造成器件区域的面积损失。而对于宽度尺寸较小的硅通孔,比如常见的10μm宽度尺寸的硅通孔,则衬底厚度就仅有100μm,而100μm的较薄的衬底厚度,又会对器件性能造成影响。

5、因此,如果能在满足器件性能的较厚衬底上,实现更高深宽比的硅通孔,比如10μm宽度和200μm深度的硅通孔,就可以更好满足一些对衬底厚度及器件面积损失有着较高要求的产品的应用需求。

技术实现思路

1、本发明的目的在于克服现有技术存在的上述缺陷,提供一种半导体器件结构及其制造方法。

2、为实现上述目的,本发明的技术方案如下:

3、本发明提供一种半导体器件结构,包括:

4、穿设于衬底中的导电通孔结构;

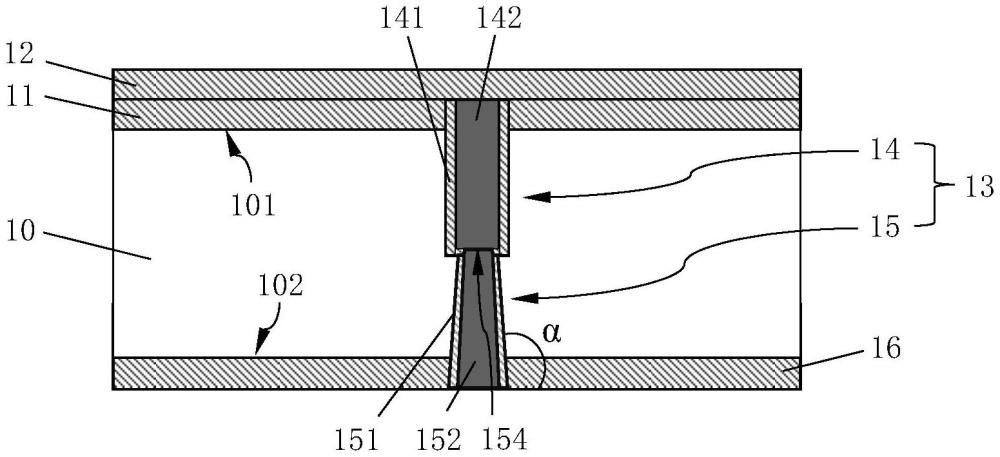

5、所述导电通孔结构包括分别自所述衬底的两个相对表面进入所述衬底中的第一导电通孔和第二导电通孔,且所述第一导电通孔的底部和所述第二导电通孔的底部在所述衬底中电性相接。

6、进一步地,所述第一导电通孔的顶部尺寸与所述第二导电通孔的顶部尺寸对应。

7、进一步地,所述第一导电通孔的顶部尺寸与底部尺寸趋于一致,所述第二导电通孔的顶部尺寸大于底部尺寸,所述第一导电通孔与所述第二导电通孔位置对应,且所述第二导电通孔的底部尺寸小于所述第一导电通孔的底部尺寸,使所述第二导电通孔的底部位于所述第一导电通孔的底部所占区域以内。

8、进一步地,所述第一导电通孔的侧壁上设有第一介质阻挡层,所述第一介质阻挡层以内填充有第一通孔金属层,所述第二导电通孔的侧壁上设有第二介质阻挡层,所述第二介质阻挡层以内填充有第二通孔金属层,位于所述第二导电通孔底部的所述第二介质阻挡层与位于所述第一导电通孔底部的所述第一介质阻挡层相接,所述第二通孔金属层依次穿过所述第二导电通孔底部的所述第二介质阻挡层和所述第一导电通孔底部的所述第一介质阻挡层进入所述第一导电通孔的底部,与所述第一通孔金属层相接;和/或,所述衬底位于所述第一导电通孔侧的第一表面上设有第一介质保护层,所述第一导电通孔的顶部位于所述第一介质保护层远离所述第一表面的一侧表面上,且所述第一导电通孔的底部穿过所述第一介质保护层进入所述衬底中,所述衬底位于所述第二导电通孔侧的第二表面上设有第二介质保护层,所述第二导电通孔的顶部位于所述第二介质保护层远离所述第二表面的一侧表面上,且所述第二导电通孔的底部穿过所述第二介质保护层进入所述衬底中,所述第一介质保护层远离所述第一表面的一侧表面上还设有第三介质保护层,所述第三介质保护层将所述第一导电通孔的顶部覆盖。

9、进一步地,所述衬底包括硅衬底,所述第一导电通孔和所述第二导电通孔包括硅通孔;和/或,所述第一导电通孔的深宽比和所述第二导电通孔的深宽比大于5:1,或,所述导电通孔结构的深宽比大于10:1。

10、本发明还提供一种半导体器件结构的制造方法,包括:

11、提供衬底;

12、在所述衬底的两个相对表面上分别形成进入所述衬底中的第一导电通孔和第二导电通孔,并使所述第一导电通孔的底部和所述第二导电通孔的底部在所述衬底中电性相接,以形成穿设于所述衬底中的导电通孔结构。

13、进一步地,形成所述导电通孔结构的方法,具体包括:

14、在所述衬底的第一表面上形成底部位于所述衬底中的第一导电通孔,并使所述第一导电通孔的顶部尺寸与底部尺寸趋于一致;

15、对所述衬底相对第一表面的第二表面进行减薄,使所述衬底被减薄至大于所述第一导电通孔深度的目标厚度;

16、在减薄后的所述衬底的第二表面上形成底部位于所述衬底中,并与所述第一导电通孔的底部电性相接的第二导电通孔,使所述第二导电通孔与所述第一导电通孔位置对应,所述第二导电通孔的顶部尺寸与所述第一导电通孔的顶部尺寸对应,所述第二导电通孔的顶部尺寸大于底部尺寸,且所述第二导电通孔的底部尺寸小于所述第一导电通孔的底部尺寸,以使所述第二导电通孔的底部位于所述第一导电通孔的底部所占区域以内,从而由相连的所述第二导电通孔和所述第一导电通孔形成导电通孔结构。

17、进一步地,形成所述第一导电通孔的方法,具体包括:

18、采用硅衬底,在所述硅衬底的第一表面上形成第一介质保护层;

19、采用光刻和刻蚀工艺,在所述第一介质保护层的表面上形成底部位于所述硅衬底中的第一通孔,并通过调节刻蚀倾角,使得所述第一通孔的顶部尺寸与底部尺寸趋于一致;

20、在所述第一通孔的内壁上形成第一介质阻挡层,以及在所述第一介质阻挡层以内的所述第一通孔中填充第一通孔金属层,从而形成硅通孔结构的第一导电通孔;

21、形成所述第二导电通孔的方法,具体包括:

22、在所述第一介质保护层的表面上形成第三介质保护层,将所述第一导电通孔的顶部覆盖;

23、将所述硅衬底翻转,对所述硅衬底的第二表面进行减薄,使所述硅衬底被减薄至所述第一导电通孔深度的两倍的目标厚度;

24、在所述硅衬底的第二表面上形成第二介质保护层;

25、采用光刻和刻蚀工艺,在所述第二介质保护层的表面上形成第二通孔,并使所述第二通孔的底部停止于所述第一导电通孔底部的所述第一介质阻挡层上,其中,通过调节刻蚀倾角,使得所述第二通孔的底部尺寸小于顶部尺寸,以使所述第二导电通孔的底部位于所述第一导电通孔的底部所占区域以内;

26、在所述第二通孔的内壁上形成第二介质阻挡层,并进行回刻,去除位于所述第二导电通孔底部的所述第二介质阻挡层和位于所述第一导电通孔底部的所述第一介质阻挡层,在所述第二通孔的底部和所述第一导电通孔的底部形成开口,露出所述第一导电通孔中的所述第一通孔金属层;

27、在所述第二介质阻挡层以内的所述第二通孔中填充第二通孔金属层,使所述第二通孔金属层通过所述开口与所述第一通孔金属层相连,从而形成与所述第一导电通孔相接的硅通孔结构的第二导电通孔。

28、进一步地,对所述硅衬底的第二表面进行减薄时,通过先采用研磨工艺,对所述第二表面进行粗磨,将所述硅衬底研磨至接近目标厚度的中间厚度,然后,采用湿法刻蚀工艺、干法刻蚀工艺和平坦化工艺的组合工艺,将所述硅衬底最终减薄至目标厚度,以降低反映在所述第二表面上的所述硅衬底的总厚度偏差;

29、执行形成所述第二通孔的光刻工艺时,通过采用红外光进行光刻对准,以将所述第二通孔相对于所述第一导电通孔的覆盖精度控制在目标精度以内,从而实现所述第二导电通孔与所述第一导电通孔的位置对准;

30、执行形成所述第二通孔的刻蚀工艺时,使对所述硅衬底材料的刻蚀速率大于对所述第一介质阻挡层材料的刻蚀速率,使形成的所述第二通孔的底部停止于所述第一导电通孔底部的所述第一介质阻挡层上,以避免使所述第一导电通孔中的所述第一通孔金属层露出;

31、以及利用形成一定厚度的所述第二介质保护层,作为进行回刻时的硬掩模层,以及位于所述硅衬底的第二表面上的顶部保护层。

32、进一步地,形成所述第一通孔时,通过调节刻蚀工艺菜单,使得所述第一通孔的深宽比大于5:1,以使得最终形成的硅通孔结构的所述导电通孔结构的深宽比大于10:1。

33、由上述技术方案可以看出,本发明通过在衬底的两个相对表面上分别形成进入衬底中的第一导电通孔和第二导电通孔,并使第一导电通孔的底部和第二导电通孔的底部在衬底中电性相接,可以在衬底中形成突破10:1深宽比的更高深宽比的导电通孔结构,以应用于硅通孔(tsv)集成结构,因此能够避免现有通过增大硅通孔的宽度尺寸方式来降低增加深宽比时的工艺难度,所带来的过大的硅通孔宽度尺寸会造成器件区域面积损失的问题,以及现有为形成宽度尺寸较小的硅通孔,而带来的衬底厚度也将相应变薄,会对器件性能造成影响的问题,使得本发明能在满足器件性能的常规厚度的衬底上,实现更高深宽比的硅通孔,从而可以更好满足一些对衬底厚度及器件面积损失有着较高要求的应用需求。

本文地址:https://www.jishuxx.com/zhuanli/20241015/314551.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表