低电阻率的基于多晶体的衬底或晶片的制作方法

- 国知局

- 2024-10-15 09:59:20

本公开涉及具有低电阻率和低翘曲度的基于碳化硅的衬底和晶片。

背景技术:

1、半导体行业一直对碳化硅(sic)表现出相当大的关注度,特别是用于制造电子器件或部件(例如,二极管、晶体管或其他相似功率应用)的碳化硅。

2、基于碳化硅的电子器件的开发和制造受到诸如形成碳化硅晶片时的电学性能和机械性能等因素的限制。制造出的许多碳化硅晶片的电阻率大于对于最终产品有益的电阻率。另一问题是源自晶片制造的翘曲量。较高的电阻率限制了电信号行进通过碳化硅晶片的能力。较高的翘曲量导致当制造终端电子器件时诸如来自抛光处理的缺陷,或者导致在处理和制造期间破裂或破碎的晶片或衬底的数量增加。

3、这些多晶sic晶片可以通过在多晶sic晶片上结合单晶晶片的方法来制造。例如,存在以下的晶片制造方法:通过直接结合,将多晶sic晶片与单晶sic晶片结合并集成在一起。在功率器件中,这些晶体缺陷、高电阻率和高翘曲度可能是有问题的,因为这些因素限制了功率器件的功能,使得功率器件的功能超出选定的公差。在这种情形下,这些器件可能被处置(例如,扔掉),由于良率降低,导致制造成本增加。

技术实现思路

1、具有低电阻率的多晶sic晶片有益于其中存在多晶sic晶片的电子器件的功能。本公开涉及提供包括具有低电阻率和低翘曲度的多晶硅碳化硅晶片或衬底的晶片的至少一个实施例。由晶片制成的电子器件或部件在使用时被进一步优化,并且几乎没有晶体缺陷。与现有的sic晶片相比,根据本公开的实施例形成的晶片具有低的或非常低的电阻率。

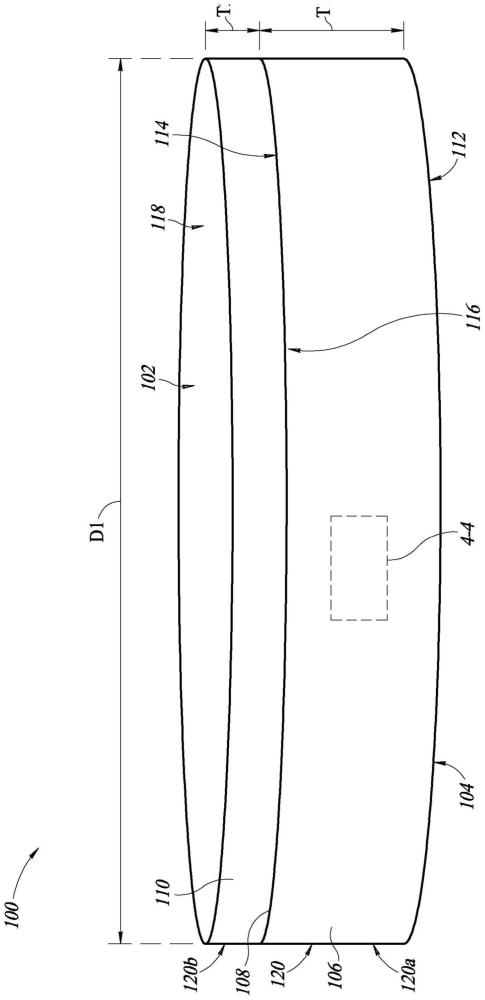

2、至少一个实施例包括一种晶片,该晶片包括电阻率小于或者等于2mohm-cm(毫欧-厘米)并且翘曲度小于或等于75μm(微米)的多晶碳化硅(sic)晶片或衬底。在一些实施例中,该晶片可以包括多晶碳化硅(sic)晶片与单晶碳化硅(sic)晶片之间的结合区域,单晶碳化硅(sic)晶片通过该结合区域耦合到多晶碳化硅(sic)晶片。多晶碳化硅(sic)晶片的低电阻率(例如,2mohm-cm)使得当电信号通过多晶sic晶片时“导通”电阻(ron)减小,从而改善了包括该晶片或该晶片的一部分的功率器件的整体信号输送功能和效率。多晶sic晶片的低翘曲度(例如,小于或等于75μm)降低了结合层内的机械缺陷或电气缺陷的可能性,或防止了该缺陷。多晶sic晶片的低翘曲度也降低了结合层、单晶碳化硅层和多晶碳化硅层之间的机械缺陷或电缺陷的可能性,或防止了该缺陷。

技术特征:1.一种器件,包括:

2.根据权利要求1所述的器件,还包括在所述多晶碳化硅(sic)晶片的第一表面上的结合层。

3.根据权利要求2所述的器件,其中,所述单晶碳化硅(sic)晶片位于所述多晶碳化硅(sic)晶片的表面上的所述结合层上,并且通过所述结合层耦合到所述多晶碳化硅(sic)晶片的第一表面。

4.根据权利要求3所述的器件,其中:

5.根据权利要求4所述的器件,其中,所述第二尺寸小于所述第一尺寸。

6.根据权利要求5所述的器件,其中:

7.根据权利要求1所述的器件,其中,所述单晶碳化硅(sic)晶片直接地物理结合到所述多晶碳化硅(sic)晶片的第一表面。

8.根据权利要求1所述的器件,其中,所述电阻率小于或等于1mohm-cm(毫欧-厘米)。

9.根据权利要求1所述的器件,其中,所述多晶碳化硅(sic)晶片的翘曲度小于75μm(微米)。

10.根据权利要求8所述的器件,其中,所述多晶碳化硅(sic)晶片的翘曲度小于45μm(微米)。

11.根据权利要求1所述的器件,其中,所述多晶碳化硅(sic)晶片具有非柱状结构。

12.根据权利要求1所述的器件,其中,所述多晶碳化硅(sic)晶片包括小于或等于1mm(毫米)的晶粒。

13.一种器件,包括:

14.根据权利要求13所述的器件,其中,所述多晶碳化硅(sic)层包括小于或等于1mm(毫米)的晶粒。

15.根据权利要求13所述的器件,其中,所述多晶碳化硅(sic)层具有非柱状结构。

16.一种器件,包括:

17.根据权利要求16所述的器件,其中,所述电阻率小于或等于1mohm-cm(毫欧-厘米)。

18.根据权利要求16所述的器件,其中,所述多晶碳化硅(sic)衬底包括小于或等于1mm(毫米)的晶粒并且具有非柱状结构。

19.根据权利要求16所述的器件,其中,所述翘曲度小于或等于75μm(微米)。

20.根据权利要求16所述的器件,其中,所述厚度是以下至少一种:150-1000μm(微米)之间、等于150μm(微米)以及等于1000μm(微米)。

21.一种方法,包括:

22.根据权利要求21所述的方法,还包括:

23.根据权利要求22所述的方法,其中,所述单晶sic衬底的所述第二部分具有在0.3-2微米(μm)范围内、等于0.3微米(μm)或等于2微米(μm)的厚度。

24.根据权利要求21所述的方法,其中,通过引入含硅气体,在化学气相沉积cvd工具的cvd腔室内的载体上形成所述多晶sic衬底。

25.根据权利要求24所述的方法,其中,通过引入碳气体和氮气,在所述cvd工具的所述cvd腔室内的所述载体上形成所述多晶sic衬底。

26.根据权利要求21所述的方法,其中,通过将掺杂粉末引入烧结工具的容器中并且用所述烧结工具烧结所述容器内的掺杂粉末来形成所述多晶sic衬底。

27.根据权利要求26所述的方法,其中,烧结所述掺杂粉末包括将所述掺杂粉末暴露于大于或等于2000摄氏度(c)的温度。

28.根据权利要求21所述的方法,其中,用升华工艺形成所述多晶sic衬底。

29.根据权利要求21所述的方法,其中,将所述单晶sic衬底结合到所述多晶sic衬底还包括将所述单晶sic衬底的第一表面直接地物理耦合到所述多晶sic衬底的第二表面。

技术总结本公开涉及低电阻率的基于多晶体的衬底或晶片。晶片的各种实施例包括多晶碳化硅(SiC)层或基体衬底。多晶碳化硅(SiC)层可以具有小于或等于2mohm‑cm(毫欧‑厘米)的电阻率,使得多晶碳化硅层是低电阻率多晶碳化硅层。多晶碳化硅层可以具有晶粒大小小于或等于1毫米(mm)的晶粒,并且可以具有非柱状结构。多晶碳化硅层可以具有小于或等于75μm(微米)的翘曲度。单晶碳化硅(SiC)层可以通过结合层耦合到多晶碳化硅(SiC)层。单晶碳化硅层可以比多晶碳化硅层薄。技术研发人员:B·马格努松林德格,C·里瓦受保护的技术使用者:意法半导体国际公司技术研发日:技术公布日:2024/10/10本文地址:https://www.jishuxx.com/zhuanli/20241015/316021.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

陶瓷体及其制造方法与流程

下一篇

返回列表