电压调节电路的制作方法

- 国知局

- 2024-10-21 14:26:20

本描述涉及一种接收输入电压并输出调节后的电压的电压调节电路,输入电压特别是dc(直流)电压供应。

背景技术:

1、近年来,gan(氮化镓)高电子迁移率晶体管技术的兴起引起了电力电子设计人员的关注。如今,目标是开发既具有能够维持高电压的功率器件又具有低压驱动器件的完全集成的功率转换器,以创建合适的驱动器。由于驱动器和功率级之间的互连较少,这可能会导致在获得更小面积、更低成本、提高可靠性和减少寄生元件的方向上进行几个改进。与通常的功率mos器件相比,这使得可以利用基于gan的技术的所有优势,例如更高的击穿电压、操作频率和更低的导通电阻。

2、例如,为了实现单片栅极驱动器,使用几个电路块以及由电压调节器提供的稳定电压偏置。

3、为了获得由电路的其它部分使用的稳定的供电电压,电压调节器应具有提供低漂移电压的电压基准发生器。

4、大多数已知体系架构都使用p-n结来获得电压基准并利用基于它的所有器件,从二极管到双极晶体管。特别地,所谓的带隙电压基准的操作原理是在电路中平衡p-n结的负温度系数(通常是双极晶体管的基极-发射极结上的电压vbe)与热电压vt的正温度系数,其中vt=kt/q。

5、在晶体管基于二维电子气(2deg)的gan技术中,这些经典的设计方法无法应用。

6、在图1中,作为这方面的示例,示意性地表示了电压调节电路10,其接收输入电压(特别是电压供应vcc)并输出调节后的电压,该调节后的电压是模拟供电电压vreg,该模拟供电电压vreg可以是正电压供应vdd,其相对于输入电压(特别是电压供应vcc)而言被稳定。如图所示,此类电压被称为接地gnd。

7、在现有技术中,大多数在无法利用p-n结的电路中提供电压基准的体系架构可以被分类为:

8、外部基准,诸如齐纳二极管:这种方法会产生几个问题,诸如由于键合线的寄生部件(电感器和电容器)或大的温度漂移而导致频率操作的限制;以及

9、内部基准:这种方法由于gan技术中可用的部件类型很少而非常具有挑战性,诸如肖特基二极管、si-cr电阻器、mim电容器和n型hem晶体管(耗尽型和增强型)。使用这些部件创建具有低温漂移和低线路灵敏度的电压基准是复杂的。

10、此外,大多数内部基准使用另一个电路块来创建可用于其它电路块作为电压偏置的调节后的电压。这意味着更高的电流消耗和更复杂的电路。

11、此外,设计此类电路块,即具有电压基准的电压调节器,也面临几个挑战,诸如:

12、补偿由于温度和过程变量引起的电压漂移;

13、环路稳定性;

14、线路灵敏度(取决于供电电压);以及

15、负载灵敏度。

技术实现思路

1、本文公开的各种实施例提供了一种具有电压基准的电压调节电路,其解决了现有技术的缺陷。

2、根据一个或多个实施例,这可以通过具有在下面的讨论中阐述的特征的电压调节电路来实现。

3、本公开描述了关于接收输入电压(特别是dc电压供应)并输出调节后的电压的电压调节电路的解决方案,

4、包括电压基准电路,被配置为供应特别是与温度变化无关的基准电压,

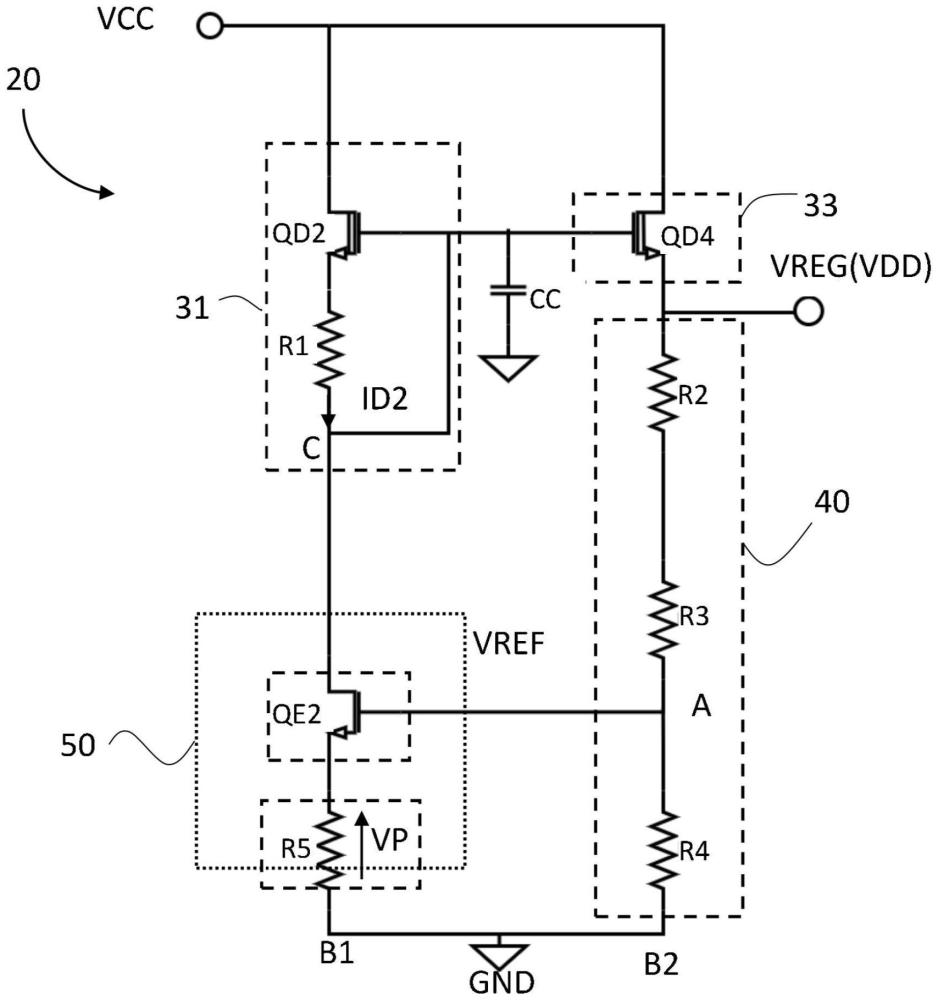

5、所述电压调节电路包括并联耦合在所述输入电压和地之间的第一电路支路和第二电路支路,

6、所述第一支路包括

7、电流发生器,包括耦合在所述输入电压和电压基准电路之间的第一耗尽型mosfet晶体管,其栅源电压为ptat(与绝对温度成比例)电压,

8、所述电压基准电路包括第一增强型mosfet晶体管,其栅源电压为ctat(与绝对温度互补)电压,其源极通过源极电阻器耦合到地,其上形成基准电压,即源极电阻器上的ptat电压降与增强型mosfet晶体管的栅源电压之和,所述第一增强型mosfet晶体管布置在所述第一支路上并且通过漏极耦合到控制节点中的所述第一耗尽型mosfet晶体管,所述控制节点耦合到所述第一耗尽型mosfet晶体管的栅极,

9、所述第一耗尽型mosfet晶体管在所述第一支路中注入ptat电流以确定所述源极电阻器上的ptat电压降,

10、所述第二支路包括耦合在待调节的电压和在其上获取调节后的电压的输出节点之间的输出级,所述输出级包括在其上获取所述输出节点的输出的第二mosfet晶体管,电阻分压器耦合到所述输出节点,从而在相应分压器输出节点上输出分压输出调节电压,该分压输出调节电压作为负反馈环路的过程变量输入,负反馈环路也耦合到所述基准电压,所述负反馈环路的输出控制所述第二mosfet晶体管的栅极。

11、在变型实施例中,在耦合在待调节的电压和其上获取所述调节后的电压的输出节点之间的所述输出级中,所述第二mosfet晶体管耦合到第一耗尽型mosfet晶体管的栅极,

12、所述负反馈环路包括所述电阻分压器的所述分压器输出节点与所述第一增强型mosfet晶体管的栅极的耦合,在所述第一增强型mosfet晶体管上形成基准电压,即源极电阻器上的ptat电压降与增强型mosfet晶体管的栅源电压之和。

13、在变型实施例中,所述增强型mos晶体管与第二增强型mosfet晶体管级联,所述第一增强型mosfet晶体管的栅极通过分压器的第一电阻器耦合到地,第二增强型mosfet晶体管的栅极通过第二电阻器耦合到所述第一电阻器并且通过第三电阻器耦合到输出节点。

14、在变型实施例中,所述第一耗尽型mosfet晶体管的栅极通过电阻器耦合到其源极,并通过所述第二增强型mosfet晶体管耦合到第一增强型mosfet晶体管的漏极。

15、在变型实施例中,所述第一耗尽型mos晶体管和第二mosfet通过相应的第三耗尽型晶体管和第四耗尽型晶体管级联,特别地所述第三耗尽型晶体管置于待调节的电压和第一耗尽型mos晶体管之间,其栅极耦合到第一耗尽型mosfet晶体管的源极,并且第四耗尽型晶体管耦合在待调节的电压和第二mosfet晶体管之间,其栅极耦合到第二mosfet晶体管的源极。

16、在变型实施例中,第一耗尽型mosfet晶体管和第二晶体管的所述栅极通过电容器接地。

17、在变型实施例中,所述负反馈环路包括差分放大器,其输入端耦合到所述分压器输出节点和所述控制节点,所述第一增强型mosfet晶体管的栅极耦合到其漏极,所述差分放大器的输出端耦合到所述第二晶体管的栅极。

18、在变型实施例中,所述耗尽型n型mosfet晶体管和增强型n型mosfet晶体管是通过氮化镓技术获得的,特别地,它们是gan高电子迁移率晶体管。

19、在实施例中,所述第二mosfet晶体管是第二耗尽型mosfet晶体管。

20、在实施例中,这里描述的解决方案还涉及接收输入电压(特别是dc电压供应)并输出调节后的电压的电压调节电路,

21、包括电压基准电路,被配置为供应特别是与温度变化无关的基准电压,

22、所述电压调节电路包括并联耦合在所述输入电压和地之间的第一电路支路和第二电路支路,包括

23、所述第一支路包括

24、电流发生器,包括耦合在所述输入电压和电压基准电路之间的第一耗尽型mosfet晶体管,其栅源电压为ptat(与绝对温度成比例)电压,

25、所述电压基准电路包括第一增强型mosfet晶体管,其栅源电压为ctat(与绝对温度互补)电压,其源极通过源极电阻器耦合到地,

26、所述第一耗尽型mosfet晶体管在所述第一支路中注入ptat电流以确定所述源极电阻器上的ptat电压降,

27、所述第二支路,包括耦合在待调节的电压和其上获取所述调节后的电压的输出节点之间的输出级,所述输出级包括耦合到第一耗尽型mosfet晶体管的栅极的第二mosfet晶体管,特别是耗尽型mosfet,

28、所述输出节点通过电阻分压器耦合到所述第一增强型mosfet晶体管的栅极,在所述第一增强型mosfet晶体管上形成基准电压,即源极电阻器上的ptat电压降与增强型mosfet晶体管的栅源电压之和。

本文地址:https://www.jishuxx.com/zhuanli/20241021/318146.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。