一种半导体结构及电子设备的制作方法

- 国知局

- 2024-10-21 14:58:06

本技术涉及半导体,尤其涉及一种半导体结构及电子设备。

背景技术:

1、随着芯片的系统集成向更高密度、更多功能、更大功率和智能化的方向发展,芯片内部高性能高功率处理区域中单位面积的发热量也不断增加。通常,将芯片内的高性能高功率处理区域称为热点区域。热点区域作为芯片内的主要热源,若热点区域的温度较高,会导致芯片总体性能较差。通过监控热点区域的热点温度,来实现对芯片的温度管理,提高芯片的性能。然而,目前收集热点区域的热点温度的结构距离热点区域的位置较远,导致监控到的热点温度具有偏差,精度较低。

技术实现思路

1、本技术实施例提供了一种半导体结构及电子设备,用以提高热点区域的热点温度的监控精度。

2、第一方面,本技术实施例提供了一种半导体结构,该半导体结构包括:至少一个芯片。所述芯片包括:衬底,所述衬底具有相对设置的第一侧和第二侧,所述衬底的第一侧设置有器件层,所述器件层具有至少一个热点区域。以及,至少一个所述芯片还包括:至少一个热敏结构、阻挡层以及温度传感器。至少一个热敏结构的至少部分内嵌于所述衬底的第二侧中,并使一个所述热点区域与至少一个所述热敏结构对应设置。阻挡层设置于所述热敏结构与所述衬底之间,且设置于通过所述热敏结构在所述衬底中形成的凹槽的内壁上。温度传感器与所述至少一个热敏结构连接。

3、本技术实施例,将热敏结构内嵌于衬底中,能够使热敏结构在垂直层面上更靠近对应的热点区域。并且,热敏结构与对应的热点区域之间的间隔材料仅为衬底材料和阻挡层材料,使得热敏结构与热点区域之间的间隔材料简单,从而使热敏结构受对应的热点区域的温度影响引起的电阻变化更准确,进而使确定出的热点温度更准确。

4、本技术实施例中,通过将热敏结构内嵌于衬底中,将热敏结构由第一布线层中移动到2d衬底区域,热点温度收集更准确,且无需占用第一布线层中的走线区域,不影响布线结构设计。

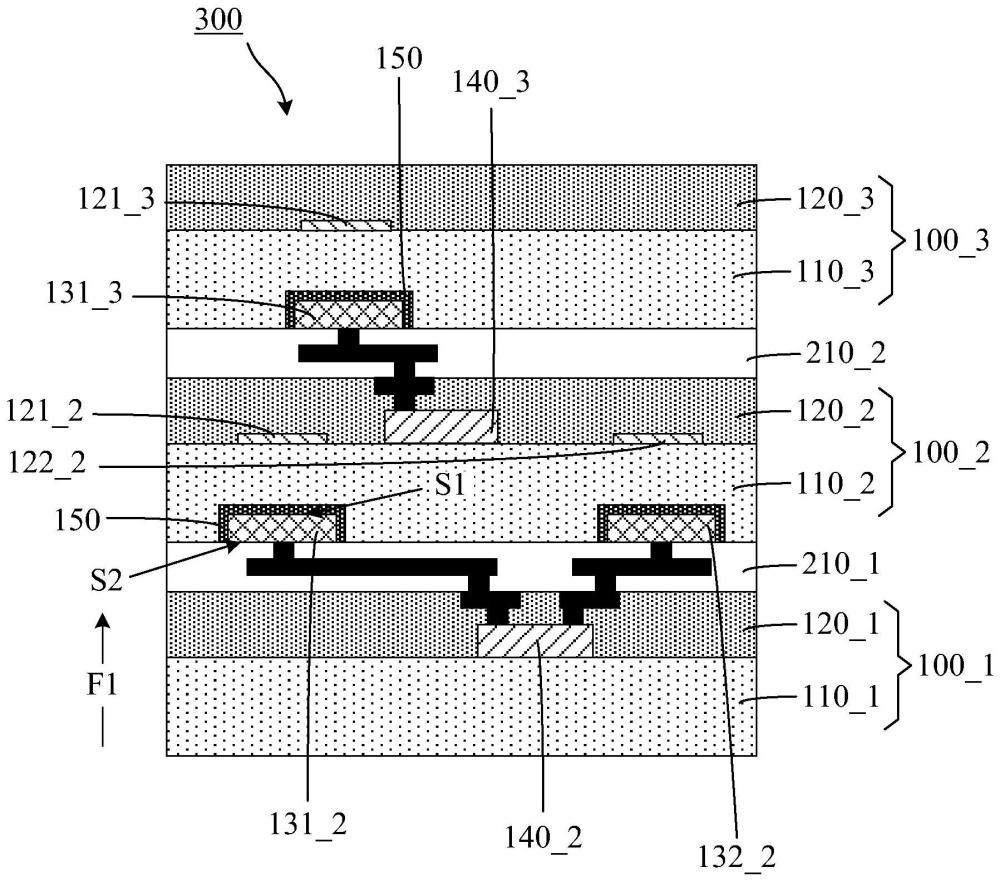

5、在一些可能的实施方式中,所述半导体结构包括多个芯片,所述多个芯片堆叠设置,每相邻设置的两个芯片之间通过第一布线层连接。这样可以使半导体结构设置为3d芯片。

6、本技术实施例中,通过将热敏结构内嵌于衬底中,不再受到3d芯片的高度限制,可以依据系统需求,选择灵敏度更好的热敏材料,或结合应力考虑,在衬底放置更大体积的热敏结构。

7、本技术实施例中,对于一个热点区域,还能根据系统设计放置多个热敏结构,这样可以读取芯片多处的温度,在进行温度管理方案设计的时候更灵活。

8、示例性地,第一布线层中可以具有重布线层(redistribution layer,rdl)。例如,第一布线层可以包括:多层介质层,以及夹在介质层之间的导电层。导电层中设置有电路布线,介质层中则会设置有介质穿孔用于连通不同层上的电路布线。在芯片的衬底中可以设置有硅通孔(through silicon via,tsv),这样可以使不同层芯片上的电路可以通过重布线层和tsv实现通信(信号传输)和电力传输。

9、示例性地,导电层的材料可以为金属材料。例如,金属材料包括但不限于al、cu、w、mn等金属,也可以是cual、sncu等金属复合材料,在此不作限定。

10、在又一些示例中,第一布线层中也可以具有介质层以及在介质层中通过tsv技术形成的tsv,并且在芯片的衬底中也可以设置有硅通孔(through silicon via,tsv),这样可以使不同层芯片上的电路可以通过介质层和衬底中的tsv实现通信(信号传输)和电力传输。

11、本技术对第一布线层中的介质层的材料不作限定。示例性地,介质层的材料包括但不限于sio2,sin,sion,不定硅等。

12、芯片与第一布线层可以采用熔融键合(fusion bonding),混合键合(hybridbonding),直接键合(direct bonding)等方式键合。

13、每一个芯片包括衬底。示例性地,衬底的材料包括但不限于si、sic、gan等材料。并且,衬底的厚度由目标产品所决定,厚度一般为几微米~几十微米。

14、本技术中的芯片可以为裸片(die),裸片是芯片未封装前的晶粒,每一个裸片就是一个具有独立功能的尚未封装的芯片,它可具有一个或多个功能电路。示例性地,裸片包括但不限于专用集成电路(application specific integrated circuit,asic)、内存裸片、存储器裸片等。当然,芯片也可以是封装后的芯片,在此不作限定。

15、在实际应用中,为了降低3d芯片的整体厚度,还可以对裸片进行减薄后进行堆叠,形成3d芯片。

16、本技术实施例中,温度传感器用于根据连接的所述热敏结构的电阻值,确定所述热点区域的热点温度。

17、在一些可能的实施方式中,在由所述衬底的第二侧指向第一侧的方向上,所述多个芯片包括第1个芯片至第n个芯片,第m个芯片包括所述热敏结构、所述阻挡层以及所述温度传感器;n为大于1的整数,2≤m≤n,m为整数;所述第m个芯片对应的温度传感器设置于第m-1个芯片的器件层中,所述第m个芯片的热敏结构通过所述第一布线层与所述温度传感器连接。本技术实施例中,可以将本层芯片对应的温度传感器设置在下一层芯片的器件层中,这样可以使温度传感器与热敏结构之间的走线较短,进一步提高确定出的热点温度的精度。

18、本技术对n的具体数值不作限定,其可以根据实际应用的需求确定。

19、在一些可能的实施方式中,第1个芯片包括所述热敏结构和所述阻挡层,所述第1个芯片的第二侧设置有第二布线层,所述第1个芯片的热敏结构通过所述第二布线层、所述第一布线层以及贯穿所述第1个芯片的衬底的硅通孔与设置于所述第1个芯片的器件层中的温度传感器连接。这样可以复用第2个芯片的温度传感器作为第1个芯片的温度传感器,可以降低温度传感器的设置数量。

20、在一些可能的实施方式中,在由所述衬底的第二侧指向第一侧的方向上,所述多个芯片包括第1个芯片至第n个芯片,第k个芯片包括所述热敏结构、所述阻挡层以及所述温度传感器;n为大于1的整数,1≤k≤n,k为整数;所述第k个芯片的温度传感器设置于所述第k个芯片的器件层中,所述第k个芯片的热敏结构通过所述第一布线层和硅通孔与所述温度传感器连接。这样可以将本层芯片对应的温度传感器设置在本层芯片的器件层中,使不同芯片之间的温度传感器相互独立。

21、在一些可能的实施方式中,1≤k≤n-1,所述第k个芯片的热敏结构依次通过所述第k个芯片与第k-1个芯片之间的第一布线层、贯穿所述第k个芯片的衬底的硅通孔以及所述第k个芯片与第k+1个芯片之间的第一布线层与所述温度传感器连接。这样即可实现温度传感器与热敏结构之间的连接。

22、在一些可能的实施方式中,所述第n个芯片的器件层上设置有第三布线层;所述第n个芯片的热敏结构依次通过所述第n个芯片与第n-1个芯片之间的第一布线层、贯穿所述第n个芯片的衬底的硅通孔以及所述第三布线层与所述温度传感器连接。这样即可实现第n个芯片的温度传感器与热敏结构之间的连接。

23、在一些可能的实施方式中,所述第1个芯片的衬底的第二侧设置有第四布线层;所述第1个芯片的热敏结构依次通过所述第四布线层、贯穿所述第1个芯片的衬底的硅通孔以及所述第1个芯片与第2个芯片之间的第一布线层与所述温度传感器连接。这样即可实现第1个芯片的温度传感器与热敏结构之间的连接。

24、在一些可能的实施方式中,也可以设置一个温度处模块,尽可能的减少温度传感器的数量。示例性地,在由所述衬底的第二侧指向第一侧的方向上,所述多个芯片包括第1个芯片至第n个芯片,第n个芯片包括所述热敏结构和所述阻挡层;n为大于1的整数,1≤n≤n,m为整数;所述温度传感器为一个,并设置于所述多个芯片中的一个芯片的器件层,以及,所述第n个芯片的热敏结构通过所述第一布线层与所述温度传感器连接。

25、在一些可能的实施方式中,本技术实施例中的半导体结构也可以设置为单层芯片。示例性地,所述半导体结构包括:一个芯片,所述温度传感器设置于所述芯片的器件层中;所述芯片的第二侧设置有第五布线层,所述芯片的器件层上设置有第六布线层,所述芯片的热敏结构依次通过所述第五布线层、贯穿所述芯片的衬底的硅通孔以及所述第六布线层与所述温度传感器连接。

26、在一些可能的实施方式中,所述热敏结构在所述衬底的正投影与对应的所述热点区域在所述衬底的正投影具有交叠区域。这样可以进一步使热敏结构在垂直层面上靠近对应的热点区域,使热敏结构与对应的热点区域之间的距离大致为衬底的厚度减去热敏结构的厚度,从而使热敏结构受对应的热点区域的温度影响引起的电阻变化更准确,进而使确定出的热点温度更准确。

27、在一些示例中,也可以使热敏结构在衬底的正投影的位于对应的热点区域在衬底的正投影内。

28、在又一些示例中,也可以使热敏结构在衬底的正投影的最外围围成的区域覆盖对应的热点区域在衬底的正投影。

29、在一些可能的实施方式中,所述衬底的第二侧设置有凹槽,所述阻挡层覆盖于所述凹槽的侧壁和底部,覆盖有所述阻挡层的凹槽中填充有热敏材料,所述热敏结构由所述热敏材料形成;即所述热敏结构与所述凹槽一一对应并填充于覆盖有所述阻挡层的凹槽中;所述热敏结构具有相对设置的第一表面和第二表面,所述热敏结构的第一表面面向所述凹槽的底部,所述热敏结构的第二表面与对应的所述凹槽的开口部对齐。

30、本技术中,可以在裸片完成减薄后,通过刻蚀工艺在衬底的第二侧蚀刻出凹槽,再通过沉积工艺在凹槽中填充入热敏材料,形成热敏结构。之后,再进行3d芯片的堆叠制备工作。这样使得凹槽在衬底上的正投影的形状即可以作为热敏结构在衬底上的正投影的形状。本技术对凹槽在衬底上的正投影的形状不作限定。示例性地,凹槽在衬底的正投影的形状包括但不限于为:矩形、圆形、椭圆形、蛇形,环形,螺旋形、网络形中的至少一种。

31、本技术实施例对形成热敏结构的热敏材料不作限定。在一些可能的实施方式中,热敏结构的材料包括但不限于cu、al、w、纳米银、金刚石中的至少一种。

32、本技术实施例对形成阻挡层的材料不作限定。在一些可能的实施方式中,阻挡层的材料包括但不限于钛、钽、氮化钛、氮化钽中的至少一种。

33、第二方面,本技术实施例还提供了一种电子设备,该电子设备可以包括:电路板和半导体结构,并且该半导体结构与电路板连接。其中,该半导体结构可以为如第一方面或第一方面的各种实施方式的半导体结构。由于上述半导体结构的性能较好,因而,包括上述半导体结构的电子设备的性能也较好。以及,该电子设备解决问题的原理与前述半导体结构相似,因此该电子设备的实施可以参照前述半导体结构的实施,重复之处不再赘述。

34、在一些可能的实施方式中,电子设备可以包括各种终端设备以及电子器件。例如,终端设备包括但不限于智能手机、智能电视、智能电视机顶盒、智能手表、个人电脑(personal computer,pc)、可穿戴设备、智能宽带等设备。例如,电子器件包括但不限于无线网络、固定网络、服务器等电信设备以及芯片模组、存储器等器件,此处不进行一一列举。

本文地址:https://www.jishuxx.com/zhuanli/20241021/319983.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表