一种显示装置源极驱动电路及其电平衡方法与流程

- 国知局

- 2024-10-21 15:12:54

本发明属于图像处理控制,尤其涉及一种显示装置源极驱动电路的电平衡方法及其源极驱动电路。

背景技术:

1、目前oled显示领域(消费品手机、穿戴)十分关注功耗的问题,除了面板内部要尽量减小电流或电压外,驱动芯片的一些功能也被要求,比如eq(equalizer,电平衡)电路功能。

2、现在市面上在面板中常用的显示单元驱动电路如图1所示,以7t1c像素补偿电路为例,采用降低pvdd和pvee以及s1、s2、emit及vdata的电压,或者提升oled的发光效率(即用很小的电流就能产生很大亮度)来实现节省功耗。但当面板tft因为工艺的考量,输入面板内部的vgho、vglo、clock(其中,vgho为面板tft的开启电压,vglo为面板tft的关断电压,三者配合可以产生s1、s2、emit)无法降低时,这部分功耗就无法单纯从电压调整来实现降低功耗。目前多数驱动芯片都采取中间电压准位来减小goa这部分由于电平翻转充放电峰值电流造成的功耗损失。

3、vgho和vglo的关系,如图2所示,正常情况下是虚线,当开启了eq功能后,波形就变成实线。假设电压从vglo到vgho产生的电流为i0,按照正常情况,那么这部分功耗损失为p0=i0*(vgho-vgio),对于ic(驱动芯片)内部,vgho及vglo由avdd经过电荷泵再经过ldo(线性稳压器)产生,所以对于ic内部这部分功耗损失就落在了avdd或vci上。当采用了eq功能后,实际上峰值电流可以认为没有发生变化,但将其平均分成了两段,最终的功耗损失为p1=1/2i0*(vgho-veq)+1/2i0*(veq-vglo)。

4、以图3为例,左侧为正常情况时的功耗示意图,当i0=2ma,vgho=8v,vglo=-7v,那么p0=30mw,若avdd=7v的话,那么avdd的功耗pavdd=14mw;右侧为以gnd端进行eq功能时的功耗示意图,由于一部分电荷宣泄到了gnd上而不计入功耗,因此p1=1/2i0*(vgho-veq)+1/2i0*(veq-vglo)=15mw,avdd的功耗pavdd=7*1=7mw。由此可见eq功能的使用可以降低面板及ic内部功耗。

5、如果利用此逻辑,将设计理念应用在源极驱动电路中,如图4所示,对功耗的降低也有贡献,在运算放大器输出当前行数据对应的源极电压至显示单元驱动电路时,利用开关,来启动eq功能,电平衡开关的一端接入源极电压输出端,另一端接参考电位端(例如vci电压端)。通常情况下,面板内部的源极电压范围为0~7v,eq功能一般不会以0v的gnd端为参考电位端,所以通常情况下会选择vci,但vci也是主板产生的,因此也会产生一部分功耗损失。

6、并且,目前显示面板由于需要不同的刷新率而采用了不同的架构,从而具有不同的刷新率,如具有60hz、90hz的显示面板采用sdl架构,以及,具有120hz的显示面板采用ddl架构,由于显示面板架构不同,导致现有技术中具备eq功能的源极驱动电路不能同时适配低刷新率和高刷新率的面板,如何在加入eq功能进一步减少因接入vci端产生的功耗损失的同时适配不同刷新率的显示面板,是一个亟待解决的问题。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种显示装置源极驱动电路及其电平衡方法,通过对dataline自身的寄生电容充放电的控制,从而达到节省功耗的效果,并且适用于sdl架构和ddl架构的显示装置。

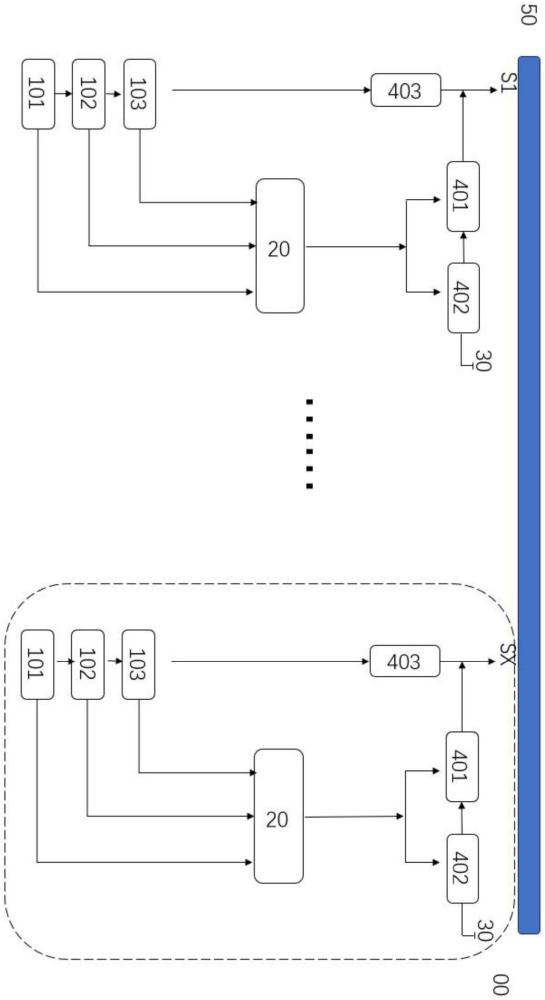

2、一方面,本发明提供一种显示装置源极驱动电路,包括第一锁存器、第二锁存器、第三锁存器、比较模块、eq开关、电源开关、op开关、电源模块;

3、所述第一锁存器、所述第二锁存器和所述第三锁存器分别与所述比较模块的一端连接;所述第一锁存器、所述第二锁存器和所述第三锁存器依次连接;所述第三锁存器与所述op开关的一端连接;

4、所述比较模块的另一端与eq开关的一端连接;

5、所述eq开关一端与op开关的一端连接,所述eq开关的另一端与所述电源开关连接,所述电源开关与所述电源模块连接,所述op开关的另一端与所述第三锁存器连接;

6、所述第三锁存器模块,用于存储第一行数据;所述第二锁存器模块,用于存储第二行数据;所述第一锁存器模块,用于存储第三行数据;其中,所述第一行数据为当前行数据,所述第二行数据为当前行数据的下一行数据,所述第三行数据为第二行数据的下一行数据;

7、所述比较模块,用于所述第三行数据和所述第二行数据的比较,或,所述第三行数据和所述第一行数据的比较,并判断比较结果是否满足预设条件,并根据判断结果控制所述eq开关、所述电源开关和所述op开关的导通和关断,从而适配sdl架构的显示面板和ddl架构的显示面板;

8、所述op开关用于控制第三锁存器的数据与显示面板之间推送的通断。

9、进一步的,所述预设条件为:所述第三行数据中最高两位构成的数值到所述第二行数中最高两位构成的数值的变化为由11变化为00,或,由00变化为11。

10、进一步的,所述预设条件为:所述第三行数据中最高两位构成的数值到所述第一行数的最高两位构成的数值变化为由00变化为11,或,由11变化为00。

11、进一步的,所述预设条件为:所述第三行数据和所述第二行数据均为8bit数据,所述第三行数据中最高两位构成的数值为所述第三行数据中第7bit和第6bit构成的数值,所述第二行数中最高两位构成的数值为所述第二行数据中第7bit和第6bit构成的数值。

12、进一步的,所述预设条件为:所述第三行数据和所述第一行数据均为8bit数据,所述第三行数据中最高两位构成的数值为所述第三行数据中第7bit和第6bit构成的数值,所述第一行数中最高两位构成的数值为所述第一行数据中第7bit和第6bit构成的数值。

13、另一方面,本发明还提供一种采用上述驱动电路的电平衡方法,包括以下步骤:

14、s0:根据所述显示装置的架构,选择不同的电平衡步骤:当显示装置为sdl架构时,跳至步骤s1;当显示装置为ddl架构时,跳至步骤s2;

15、s1:当显示架构为sdl架构时:

16、s11:将第一行数据、第二行数据和第三行数据分别存储于所述第三锁存器、所述第二锁存器中和所述第一锁存器中;

17、s12:利用所述比较模块对所述第三行数据和所述第二行数据进行比较,当比较结果满足所述预设条件时,跳至步骤s13;反之,则跳至步骤s14;

18、s13:导通所述eq开关,并随后关断所述op开关;所述电源开关始终处于关闭状态;

19、s14:所述eq开关导通并维持一段时间后,关断所述eq开关,并随后导通所述op开关,所述第三锁存器中的数据由所述op开关推送至所述显示面板进行显示;

20、s2:当显示架构为ddl架构时:

21、s21:将第一行数据、第二行数据和第三行数据分别存储于所述第三锁存器、所述第二锁存器中和所述第一锁存器中;

22、s22:利用所述比较模块对所述第三行数据和所述第一行数据进行比较;当比较结果满足所述预设条件时,则跳至步骤s23;反之,则跳至步骤s24;

23、s23:导通所述eq开关,并随后关断所述op开关,且在所述eq开关导通以及所述op开关关断期间,所述电源开关导通并维持;

24、s24:所述eq开关导通并维持一段时间后,关断所述eq开关,并在所述eq开关关断前,关断所述电源开关,并在所述eq开关关断后,所述op开关导通,在所述op开关导通期间,所述第三锁存器中的数据由所述op开关推送至所述显示面板进行显示。

25、进一步的,所述预设条件为:所述第三行数据中最高两位构成的数值到所述第二行数中最高两位构成的数值的变化为由11变化为00,或,由00变化为11。

26、进一步的,所述预设条件为:所述第三行数据中最高两位构成的数值到所述第一行数的最高两位构成的数值的变化为由00变化为11,或,由11变化为00。

27、进一步的,所述预设条件为:所述第三行数据和所述第二行数据均为8bit数据,所述第三行数据中最高两位构成的数值为所述第三行数据中第7bit和第6bit构成的数值,所述第二行数中最高两位构成的数值为所述第二行数据中第7bit和第6bit构成的数值。

28、进一步的,所述预设条件为:所述第三行数据和所述第一行数据均为8bit数据,所述第三行数据中最高两位构成的数值为所述第三行数据中第7bit和第6bit构成的数值,所述第一行数中最高两位构成的数值为所述第一行数据中第7bit和第6bit构成的数值。

29、与现有技术相比,本发明具有以下优势:

30、(1)本发明通过增加了一级锁存器和电源开关,从而使得原本仅适用于sdl架构的源极驱动电路不仅适配sdl架构,还适配ddl架构。

31、(2)本发明通过dataline的寄生电容实现了eq功能,从而降低了整体功耗。

本文地址:https://www.jishuxx.com/zhuanli/20241021/320885.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种数字媒体展示装置

下一篇

返回列表