提升传输结束数据包回报准确性的方法、芯片的兼容性测试方法、显示驱动芯片与流程

- 国知局

- 2024-11-06 14:59:38

本发明涉及芯片测试,尤其涉及一种提升传输结束数据包回报准确性的方法、芯片的兼容性测试方法、显示驱动芯片。

背景技术:

1、移动产业处理器接口(mobile industry processor interface,mipi)是由mipi联盟发起的为移动应用处理器制定的开放标准和规范。mipi联盟下dsi(mipi dsi,mobileindustry processor interface display serial interface,mipi联盟显示串行接口,简称为dsi)所定义的数据包有两种:短数据包和长数据包。其中,短数据包(short packet)主要用于传输命令以及读写寄存器地址信息;长数据包(long packet)主要用用于传输大量图像数据或部分控制命令。

2、如图1所示,示意了dsi的两类数据包结构,其中短数据包和长数据包所包含的各个序列包含义如下:

3、lps:低功耗模式,排在短数据包和长数据包的首位和末尾。

4、sot:传输起始信号,紧邻lps之后。

5、data id:数据标识符。

6、word count(wc):计数字段。

7、ecc:纠错码;纠错码可以设置在图1的短数据包中的data 1与eot之间;纠错码也可以设置在图1的长数据包中的word count与data 0之间。

8、data:命令或者数据,表示命令时包括图1的短数据包中的data 0和data 1,表示数据时包括图1的长数据包中的data 0、data 1、...、data wc-2和data wc-1。

9、check sum:校验和,配合纠错码ecc进行检验纠错;check sum例如设置在图1的长数据包的包尾(packet footer(pf))部分,图1中的check sum占据16比特位宽。

10、eot:传输结束信号,设置在位于数据包末尾的lps之前且相邻;在长数据包中,包头、有效数据内容和包尾依次设置在sot和eot之间;在短数据包中,只有包头设置在sot和eot之间。总的来说,lps、sot和eot分别表示传输数据时的不同电路时序状态,各个数据包之间由eot-lps-sot序列包隔开。

11、dsi发送端用于基于dsi协议使用输出的图像数据驱动显示模组,能够显示在显示屏上。dsi具备低功率模式(lp,lower power)和高速模式(hs,high speed)该两种工作模式,实现mipi接口协议层中的数据和命令的传输。dsi的初始状态均是lp模式下的中止传输状态,大批量的数据传输一般是在hs模式中进行。dsi进入或退出hs模式的控制方式都一样,退出hs模式后可回到lp模式的中止传输状态。dsi在hs模式下的数据传输采用数据包格式,分为长数据包和短数据包。dsi发送数据的时候,将数据按照信息类型及内容进行打包,以完成纠错码(ecc码)的生成和循环冗余校验码 (crc码)的添加。

12、如图2所示,接受到传输mipi时钟信号clk后,根据mipi差动信号dp/dn,会依序sot-> virtual channel id -> data type -> ecc single/muti-bit -> word count ->checksum -> eot开始判读数据包,其中,eot数据包是最后一笔数据bit的反向8bit。

13、dsi是面向字节的协议,现有芯片匹配mipi传输的封包的包头和包尾分别设置有开始传输(sot)标志和结束传输(eot)标志,所有未损坏的高速(hs)传输都包含整数个字节,如果在eot序列包期间,外设phy(物理层)检测到最后一个字节与字节边界不匹配,则应标记eot同步错误。如果需要一个确认响应,外围设备应发送一个确认和错误报告包。外设应在向主机处理器返回数据包的错误报告字节中设置eot同步错误位。

14、然而,封包内的各数据包都比较容易受esd静电、emi电磁干扰等影响,导致数据包损坏甚至丢失,例如eot作为封包传输的最后一个数据包,当数据包受影响(例如受esd静电、emi电磁干扰等)导致该eot数据包丢掉,mipi传输协议无法判断下一个接来的数据包是否为最后一个,这个时候会以为eot数据包还没有到来,从而导致结束传输(eot)标志乱举,例如,现有技术中,常设置eot标志为低电平指示eot得到了正常传送,高电平指示eot未得到正常传送。当封包进入高速传输状态后,现有技术中通常设置eot一直标志为低电平,即eot得到了正常传送;接下来在逐个完成各数据包的传输过程中,理想状态下,eot标志应当在对应eot数据传输结束的位置获得一个准确的eot是否正常传送的信号以确定eot标志是指示eot正常传送(低电平)还是指示eot未正常传送(高电平);然而,如果此时eot数据包若丢失或损坏,eot标志要么不会获得该指示,要么会获得一个错误的指示。特别是在eot数据包丢失的情况下,现有技术的这种设置会导致eot标志仍然指示eot正常传送,并最终在该封包的低速传输状态回报eot正常传送,这样的回报显然是错误的,这也导致芯片兼容性验证(cts,compatibility test suite)准确率极低,严重影响兼容性验证准确性。为了应对该情况,现有的兼容性验证测试方法也有将数据包内的每一数据包内容都进行更换,然后验证结束传输(eot)标志是否会举起以一一验证是否存在eot同步错误的问题。然而该方法效率极低。

技术实现思路

1、基于上述描述的问题,本发明提出提升传输结束数据包回报准确性的方法、芯片的兼容性测试方法、显示驱动芯片,所述方法对于任意封包,在进入高速传输时,先默认传输结束数据包未正常传送并设置指示传输结束数据包的标志信号维持指示传输结束数据包未正常发送,此后只有收到了正确的传输结束数据包才撤掉传输结束数据包未正常发送的指示,并在该封包传输进入低速传输后输出标志信号以指示传输结束数据包正常发送。从而可以避免标志信号乱举,提升传输结束数据包回报的准确性,使得芯片cts验证的准确性得到保证。

2、第一方面,本发明提供一种提升传输结束数据包回报准确性的方法,其特征在于,在任意封包进入高速传输时,先默认传输结束数据包未正常传送,并设置指示传输结束数据包的标志信号维持指示传输结束数据包未正常发送,此后只有收到了正确的传输结束数据包才撤掉传输结束数据包未正常发送的指示,并在该封包的低速传输状态输出所述标志信号以指示传输结束数据包正常发送。

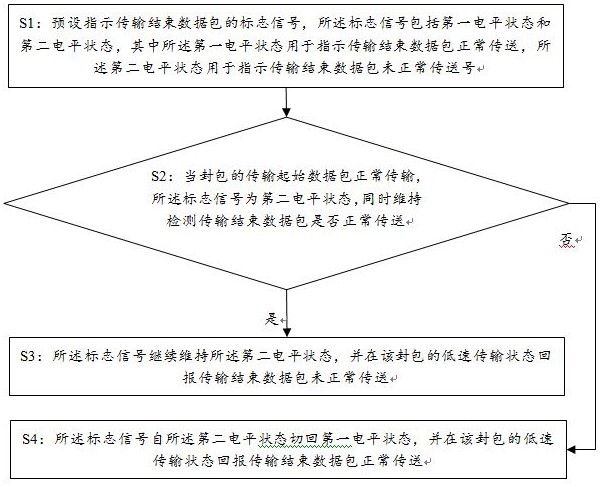

3、优选的,所述方法包括步骤:

4、步骤s1:预设指示传输结束数据包的标志信号,所述标志信号包括第一电平状态和第二电平状态,其中所述第一电平状态用于指示传输结束数据包正常传送,所述第二电平状态用于指示传输结束数据包未正常传送;

5、步骤s2:当封包的传输起始数据包正常传输,所述标志信号为第二电平状态,同时维持检测传输结束数据包是否正常传送,若未检测到传输结束数据包正常传送,则进入步骤s3,若检测到传输结束数据包正常传送,则进入步骤s4;

6、步骤s3:所述标志信号继续维持所述第二电平状态,并在该封包的低速传输状态回报传输结束数据包未正常传送;

7、步骤s4:所述标志信号自所述第二电平状态切回第一电平状态,并在该封包的低速传输状态回报传输结束数据包正常传送。

8、优选的,维持检测传输结束数据包是否正常传送还包括传输结束数据包误判规避标准是否发生的检测,当所述传输结束数据包误判规避标准发生,则直接进入所述步骤s3。

9、优选的,所述传输结束数据包误判规避标准包括封包内的数据包丢失或损坏。

10、优选的,所述封包包括短封包或长封包。

11、优选的,所述封包包括单一封包或多封包。

12、第二方面,提供一种芯片的兼容性测试方法,在对芯片进行兼容性验证时,根据前述任一所述的提升传输结束数据包回报准确性的方法以进行传输结束数据包是否正常传送的回报。

13、第三方面,提供一种显示驱动芯片,所述显示驱动芯片支持mipi封包传输,并且将前述任一所述的提升传输结束数据包回报准确性的方法应用于所述显示驱动芯片的兼容性验证进行传输结束数据包是否正常传送的回报。

14、与现有技术相比本发明技术方案具有以下有益效果:在进入高速传输时,先默认传输结束数据包未正常传送并设置指示传输结束数据包的标志信号维持指示传输结束数据包未正常发送,此后只有收到了正确的传输结束数据包才撤掉传输结束数据包未正常发送的指示,并在该封包传输进入低速传输后输出标志信号以指示传输结束数据包正常发送。从而可以避免标志信号乱举,提升传输结束数据包回报的准确性,使得芯片cts验证的准确性得到保证。

本文地址:https://www.jishuxx.com/zhuanli/20241106/324809.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表