BMS高压侧与低压侧的隔离通信电路结构及控制方法与流程

- 国知局

- 2024-11-18 18:23:27

本技术涉及隔离通信电路,具体地涉及一种bms高压侧与低压侧的隔离通信电路结构及控制方法。

背景技术:

1、bms(battery management system蓄电池管理系统)通信电路是一种较为常见的电路结构,在传统的bms通信电路中,高低压之间通信方式单一,通信电路结构复杂,高低压之间通信无隔离功能,同时高低压之间通信方式兼容性差。

技术实现思路

1、为克服上述缺点,本技术的目的在于:提供一种bms高压侧与低压侧的隔离通信电路结构及控制方法,解决上述技术问题。

2、为了达到以上目的,本技术采用如下技术方案:

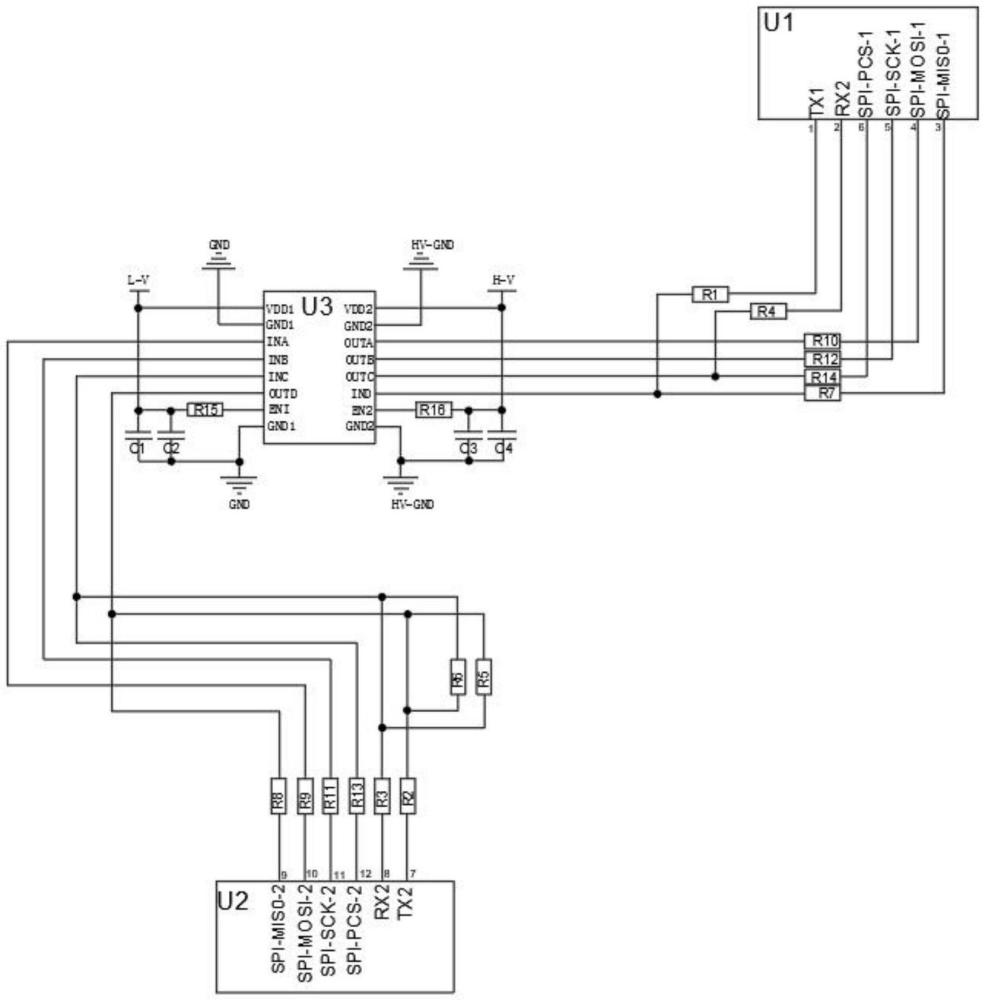

3、第一方面,本技术提供一种bms高压侧与低压侧的隔离通信电路结构,包括:

4、第一芯片,所述第一芯片包括第一信号输送模块一和第二信号输送模块一,

5、第二芯片,所述第二芯片包括第一信号输送模块二和第二信号输送模块二,

6、第三芯片,所述第三芯片包括隔离信号输送模块,

7、电阻模块,所述电阻模块包括电阻模块一、电阻模块二、电阻模块三以及电阻模块四;

8、所述第一信号输送模块一与所述隔离信号输送模块电性连接,所述隔离信号输送模块与所述第一信号输送模块二电性连接,同时,所述电阻模块一设置在所述第一信号输送模块一与所述隔离信号输送模块连接的电路上,所述电阻模块二设置在所述隔离信号输送模块与所述第一信号输送模块二连接的电路上;

9、所述第二信号输送模块一与所述隔离信号输送模块电性连接,所述隔离信号输送模块与所述第二信号输送模块二电性连接,同时,所述电阻模块三设置在所述第二信号输送模块一与所述隔离信号输送模块连接的电路上,所述电阻模块四设置在所述隔离信号输送模块与所述第二信号输送模块二连接的电路上。

10、进一步地,

11、所述第一芯片还包括时钟信号模块一和片选信号模块一,

12、所述第二芯片还包括时钟信号模块二和片选信号模块二,

13、所述电阻模块还包括电阻模块五和电阻模块六、电阻模块七以及电阻模块八;

14、所述时钟信号模块一与所述隔离信号输送模块电性连接,所述信号输送模块与所述时钟信号模块二电性连接,所述片选信号模块一与所述隔离信号输送模块电性连接,所述隔离信号输送模块与所述片选信号模块二电性连接,同时,所述电阻模块五设置在所述时钟信号模块一与所述隔离信号输送模块连接的电路上,所述电阻模块六设置在所述信号输送模块与所述时钟信号模块二连接的电路上,所述电阻模块七设置在所述片选信号模块一与所述隔离信号输送模块连接的电路上,所述电阻模块八设置在所述隔离信号输送模块与所述片选信号模块二连接的电路上。

15、进一步地,

16、所述第一芯片中:

17、所述第一信号输送模块一包括引脚一和引脚二,所述第二信号输送模块一包括引脚三和引脚四,所述时钟信号模块一包括引脚五,所述片选信号模块一包括引脚六;

18、所述第二芯片中:

19、所述第一信号输送模块二包括引脚七和引脚八,所述第二信号输送模块二包括引脚九和引脚十,所述时钟信号模块二包括引脚十一,所述片选信号模块一包括引脚十二;

20、所述第三芯片中:

21、所述隔离信号输送模块包括输入引脚一、输入引脚二、输入引脚三、输入引脚四、输出引脚一、输出引脚二、输出引脚三、输出引脚四。

22、进一步地,

23、所述第一信号包括can通讯信号和uart通讯信号,其中:

24、根据所述can通讯信号的传输方向,所述引脚一与所述输入引脚四电性连接,所述输出引脚四与所述引脚七电性连接,所述引脚八与所述输入引脚三电性连接,所述输出引脚三与所述引脚二电性连接;

25、根据所述uart通讯信号的传输方向,所述引脚一与所述输入引脚四电性连接,所述输出引脚四与所述引脚八电性连接,所述引脚七与所述输入引脚三电性连接,所述输出引脚三与所述引脚二电性连接。

26、进一步地,

27、所述电阻模块一包括电阻一和电阻四,电阻模块二包括电阻二、电阻三、电阻五以及电阻六,其中:

28、所述电阻一设置在所述引脚一与所述输入引脚四连接的电路上,所述电阻二设置在所述输出引脚四与所述引脚七连接的电路上,所述电阻三设置在所述引脚八与所述输入引脚三连接的电路上,所述电阻四设置在所述输出引脚三与所述引脚二连接的电路上,所述电阻五设置在所述输出引脚四与所述引脚八连接的电路上,所述电阻六设置在所述引脚七与所述输入引脚三连接的电路上。

29、进一步地,

30、所述第二信号包括spi通讯信号,

31、根据spi通讯信号的传输方向,所述引脚三与所述输入引脚四电性连接,所述输出引脚四与所述引脚九电性连接,所述引脚十与所述输入引脚一电性连接,所述输出引脚一与所述引脚四电性连接;

32、根据时钟信号的传输方向,所述引脚十一与所述输入引脚二电性连接,所述输出引脚二与所述引脚五电性连接;

33、根据片选信号的传输方向,所述引脚十二与所述输入引脚三电性连接,所述输出引脚三与所述引脚六电性连接。

34、进一步地,

35、所述电阻模块三包括电阻七和电阻十,所述电阻模块四包括电阻八和电阻九,所述电阻模块五包括电阻十一,所述电阻模块六包括电阻十二,所述电阻模块七包括电阻十三,所述所述电阻模块八包括电阻十四,其中:

36、所述电阻七设置在所述引脚三与所述输入引脚四连接的电路上,所述电阻八设置在所述输出引脚四与所述引脚九连接的电路上,所述电阻九设置在所述引脚十与所述输入引脚一连接的电路上,所述电阻十设置在所述输出引脚一与所述引脚四连接的电路上;

37、进一步地,

38、所述电阻十一设置在所述引脚十一与所述输入引脚二连接的电路上,所述电阻十二设置在所述输出引脚二与所述引脚五连接的电路上;

39、所述电阻十三设置在所述引脚十二与所述输入引脚三连接的电路上,所述电阻十四设置在所述输出引脚三与所述引脚六连接的电路上。

40、进一步地,

41、所述第三芯片还包括供电引脚一、供电引脚二,接地引脚一、接地引脚二、使能引脚一以及使能引脚二,其中,

42、所述供电引脚一电性连接低压侧电源,所述供电引脚二电性连接高压侧电源,

43、所述使能引脚一电性连接电容一和电容二,且在所述使能引脚一与所述电容一、所述电容二连接的电路中设置有电阻十五;

44、所述使能引脚一电性连接电容三和电容四,且在所述使能引脚二与所述电容三、所述电容四连接的电路中设置有电阻十六。

45、第二方面,本技术还提供一种bms高压侧与低压侧的隔离通信电路控制方法,其包括:

46、当电路进行can通讯时,选贴电阻一、电阻二、电阻三以及电阻四,第一芯片中的引脚一将信号输送至第三芯片的输入引脚四,通过第三芯片进行信号隔离,再通过第三芯片的输出引脚四将信号输送至第二芯片的引脚七,通过第二芯片的引脚八将信号输送至第三芯片的输入引脚三,最后通过第三芯片的输出引脚三将信号输送至第一芯片的引脚二;

47、当电路进行uart通讯时,选贴电阻一、电阻二、电阻三、电阻四,电阻五和电阻六,第一芯片中的引脚一将信号输送至第三芯片的输入引脚四,通过第三芯片进行信号隔离,再通过第三芯片的输出引脚四将信号输送至第二芯片的引脚八,通过第二芯片的引脚七将信号输送至第三芯片的输入引脚三,最后通过第三芯片的输出引脚三将信号输送至第一芯片的引脚二;

48、当电流进行spi通讯时,第一芯片为从芯片,第二芯片为主芯片,选贴电阻七、电阻八、电阻九、电阻十、电阻十一、电阻十二、电阻十三以及电阻十四,第一芯片中的引脚三将信号输送至第三芯片的输入引脚四,通过第三芯片进行信号隔离,再通过第三芯片的输出引脚四将信号输送至第二芯片的引脚九,

49、通过第二芯片的引脚十将信号输送至第三芯片的输入引脚一,最后通过第三芯片的输出引脚一将信号输送至第一芯片的引脚四,同时第二芯片的引脚十一将时钟信号输送至第三芯片的输入引脚二,再通过第三芯片的输出引脚二将时钟信号输送至第一芯片的引脚五,第二芯片的引脚十二将片选信号输送至第三芯片的输入引脚三,再通过第三芯片的输出引脚三将片选信号输送至第一芯片的引脚六。

50、有益效果

51、本技术公开的一种bms高压侧与低压侧的隔离通信电路结构,通过选贴电阻,可以适配高压侧从芯片的采样数据通过多种通讯方式回传到低压侧的主芯片,适用can通信、spi通信、uart通信等通信方式,可有效地增加bms高低压之间通信方式,简化bms高低压之间通信电路,增加bms高低压之间通信隔离,增加bms高低压之间通信的兼容性。

本文地址:https://www.jishuxx.com/zhuanli/20241118/328582.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表