集成PN结和肖特基结的平面栅MOSFET及制备方法与流程

- 国知局

- 2024-11-21 12:03:30

本发明涉半导体,尤其涉及集成pn结和肖特基结的平面栅mosfet及制备方法。

背景技术:

1、在电力电子器件技术领域,mosfet作为一种常用的功率半导体,已经代替三极管成为功率半导体领域最常用的开关器件之一。

2、mosfet在几十年的迭代过程中,已经成为目前主流的功率半导体器件之一,在某些应用场合,mosfet的体二极管发挥重要的续流作用,目前常规的mosfet主要采用pn结体二极管进行续流,pn结体二极管存在开启电压大,通流能力弱的缺点,因此如何改善mosfet体二极管的性能一直是目前研究的热点。

3、在mosfet中集成肖特基二极管是一种改善mosfet体二极管的性能的方案,目前已经有多个专利研究了该技术,一般都有其局限性,例如:

4、2024年06月25日公告的一篇“集成sbd的平面mosfet及其工艺方法”,公开号为cn118248553a;该专利利用肖特基二极管代替pn结体二极管,但肖特基二极管完全代替pn结体二极管,降低了体二极管正向浪涌能力,且制备过程需要从外延片表面对p-well整体进行n型离子注入,n型离子注入穿通整个p-well区,容易产生横向扩散导致元胞尺寸难以缩小。

5、2024年01月02日公告的一篇“一种源极沟槽集成sbd的sic平面mos及制备方法”,公开号为cn117334747a,该专利将源极沟槽穿通体区并延伸至耐压区,利用mosfet体区下方的电流扩展层与沟槽内肖特基接触金属形成sbd,并为了减小集成的sbd的反向漏电,在肖特基接触金属下方制备p+屏蔽层,但是在耐压区制备p+屏蔽层也减弱了集成的sbd的正向通流能力和mosfet正向通流能力。

6、因此,在mosfet中集成肖特基二极管,改善器件性能的同时增强mosfet体二极管续流能力成为本行业亟需解决的技术难题。

技术实现思路

1、本发明针对增强mosfet体二极管续流能力的研发方向,发明了一种集成pn结和肖特基结的平面栅mosfet及其制备方法。

2、本发明的技术方案是:

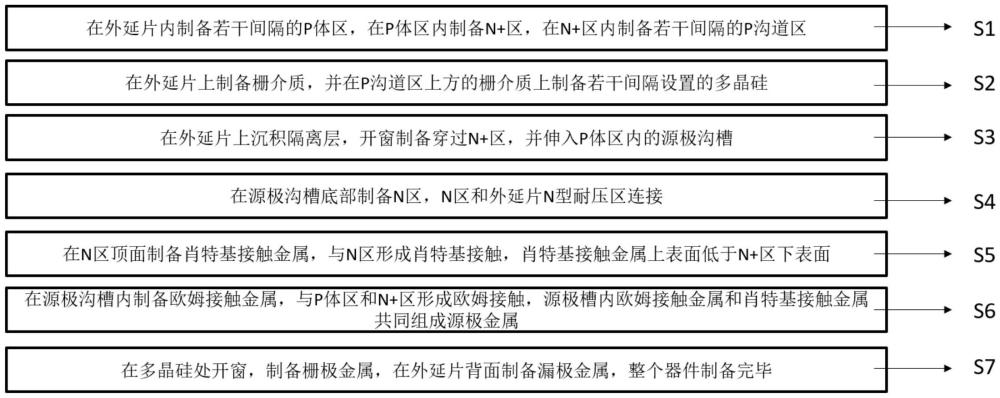

3、集成pn结和肖特基结的平面栅mosfet制备方法,包括以下步骤:

4、步骤s100,在外延片内制备若干间隔的p体区,在p体区内制备n+区,在n+区内制备若干间隔的p沟道区;

5、步骤s200,在外延片上制备栅介质,并在p沟道区上方的栅介质上制备若干间隔设置的多晶硅;

6、步骤s300,在外延片上沉积隔离层,开窗制备穿过n+区,并伸入p体区内的源极沟槽;

7、步骤s400,在源极沟槽底部制备n区,n区和外延片n型耐压区连接;

8、步骤s500,在n区顶面制备肖特基接触金属,与n区形成肖特基接触,肖特基接触金属上表面低于n+区下表面;

9、步骤s600,在源极沟槽内制备欧姆接触金属,与p体区和n+区形成欧姆接触,源极槽内欧姆接触金属和肖特基接触金属共同组成源极金属;

10、步骤s700,在多晶硅处开窗,制备栅极金属,在外延片背面制备漏极金属,整个器件制备完毕。

11、具体的,步骤s100包括:

12、步骤s110,利用光刻工艺,使用掩模将p体区外部区域保护,通过扩散工艺或者离子注入工艺,形成若干间隔的p体区;

13、步骤s120,利用光刻工艺,使用掩模将n+区外部区域保护,通过扩散工艺或者离子注入工艺,形成n+区;

14、步骤s130,利用光刻工艺,使用掩模将p沟道区外部区域保护,通过扩散工艺或者离子注入工艺,形成若干间隔的p沟道区。

15、具体的,步骤s200包括:

16、步骤s210,使用热氧技术在外延片上制备栅介质;

17、步骤s220,通过光刻工艺,使用掩模将p沟道区外部区域保护,通过化学气相沉积,在p沟道区上方的栅介质上制备多晶硅。

18、具体的,步骤s300包括:

19、步骤s310,利用化学气相沉积制备隔离层,通过光刻工艺,使用掩模将源极沟槽外部区域保护,采用刻蚀工艺制备源极沟槽,源极沟槽底部延伸至p体区,沟槽两侧面位于n+区内部。

20、具体的,步骤s400包括:

21、步骤s410,利用光刻工艺,使用掩模将源极沟槽外部区域保护,通过扩散工艺或者离子注入工艺,在源极沟槽底部制备n区,n区和外延片n型耐压区连接。

22、具体的,步骤s500包括:

23、步骤s510,利用光刻工艺,使用掩模将源极沟槽外部区域保护,使用剥离工艺或者刻蚀工艺,在源极沟槽底部制备肖特基接触金属,与n区形成肖特基接触,肖特基接触金属上表面低于n+区下表面。

24、具体的,步骤s600包括:

25、步骤s610,利用光刻工艺,使用掩模将源极沟槽外部区域保护,使用剥离工艺或者刻蚀工艺,在源极沟槽内制备欧姆接触金属,与p体区、n+区形成欧姆接触,源极槽内欧姆接触金属和肖特基接触金属共同组成源极金属。

26、具体的,步骤s700包括:

27、步骤s710,利用光刻工艺,使用掩模将多晶硅开窗处外部区域保护,利用刻蚀工艺,在多晶硅处开窗,随后使用剥离工艺或者刻蚀工艺制备栅极金属,使用减薄工艺和背金工艺在外延片背面制备漏极金属,整个器件制备完毕。

28、集成pn结和肖特基结的平面栅mosfet,包括自下而上依次设置的漏极金属、外延片、多晶硅和隔离层;

29、所述外延片顶部设有:

30、p体区,设有若干并相互间隔;

31、n+区,设有若干并相互间隔,分别从所述外延片的顶面向下;

32、p沟道区,设有若干,分别从所述n+区顶面端部向下延伸至n+区底面;

33、栅介质,设置在所述外延片的顶面;

34、所述多晶硅设有若干并相互间隔,分别位于所述栅介质的顶面;

35、所述隔离层位于多晶硅顶面和相邻多晶硅之间的栅介质上;

36、n区,设置在所述p体区内,底面与n型耐压区连接;

37、肖特基接触金属,沿所述n区的顶面向上延伸,与所述n区形成肖特基接触,其顶面低于所述p体区的顶面;

38、欧姆接触金属,沿所述肖特基接触金属的顶面向上延伸,其顶面与所述隔离层上表面齐平;

39、栅极金属,从所述隔离层的顶面向下延伸至多晶硅内部,和所述多晶硅形成良好的欧姆接触。

40、具体的,所述外延片包括自下而上的n+衬底层和n型耐压区。

41、本发明有益效果:

42、本发明通过制备源极沟槽,并在源极沟槽底部制备肖特基接触,形成了集成肖特基二极管和pn结二极管的结构,利用肖特基二极管的低开启电压和高电流特性,达到减小体二极管续流损耗的目的,利用pn结二极管增强体二极管正向浪涌能力。同时本发明肖特基二极管的n区,两侧是mosfet的p体区,形成超结结构,进而减小集成的肖特基二极管的反向漏电,不需要特殊的额外工艺步骤来降低集成的肖特基二极管的反向漏电,外延层结构和常规mosfet结构一致,不影响集成的sbd的正向通流能力和mosfet正向通流能力,和已有的对比文件相比,本发明制备的增强体二极管续流能力的平面栅mosfet及其制备方法,具备更优异的性能优势和工艺优势。

本文地址:https://www.jishuxx.com/zhuanli/20241120/334062.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。