一种用于音频主动降噪功能的复合ADC电路的制作方法

- 国知局

- 2024-06-21 10:38:31

本技术涉及集成电路,尤其是涉及一种用于音频主动降噪功能的复合adc电路。

背景技术:

1、随着移动互联网的发展,尤其是手机和便携式入耳耳机的普及,耳机的降噪功能成为新的产品亮点,耳机降噪主要分为被动降噪和主动降噪两种。其中,主动降噪是通过一个麦克风主动采集环境噪声,快速处理后,反相送给耳机播放出来,这样子耳机播放一个和环境噪声反相的声波信号,两者在人耳膜上的效果抵消了,就可以实现主动降噪。而实际上,因为耳机/人耳结构限制,从麦克风采集到环境噪声到播放出反相信号的整个主动降噪处理时间必须足够小,不然环境噪声已经传递到耳膜了,而主动降噪输出追不上环境噪声在空气和耳道中的传播,就没有主动降噪效果。一般的耳机考虑其物理结构,从麦克风采集的位置到实际耳机播放输出的位置,空间距离就1-2cm,声音在空气中传播340m/s,所以时间就是29us-58us,即整个主动降噪处理时间必须要小于这个范围才能起到降噪效果。

2、现有的应用于音频主动降噪功能的sigma-delta调制器的采样率是8k-48khz,其单纯采样一个点就是需要20us-125us,并且sigma-delta调制器结构是利用多次采样的时间累积结果作为一个采样点输出,所以其数字滤波器的实际延时会更大,一般过采样率取128,adc时钟在6.144mhz(48k*128)的调制器,声音经过数字滤波后延时接近100us,无法满足主动降噪处理时间的要求。

3、针对上述中的相关技术,发明人发现现有的sigma-delta调制器存在有时延性能、信噪比要求和功耗难以同时满足的问题。

技术实现思路

1、为了在改善时延性能的同时减少对芯片信噪比的影响,以及降低功耗,本技术提供了一种用于音频主动降噪功能的复合adc电路。

2、第一方面,本技术提供一种用于音频主动降噪功能的复合adc电路。

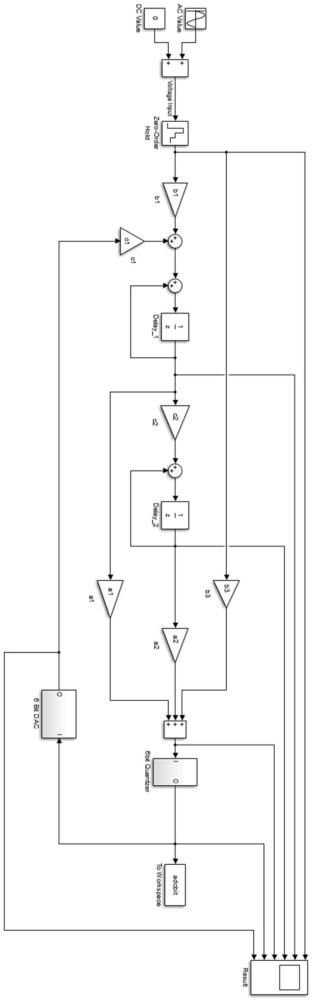

3、本技术是通过以下技术方案得以实现的:

4、一种用于音频主动降噪功能的复合adc电路,包括,

5、采样模块,用于获取采样信号并转化为模拟信号输出;

6、滤波模块,电性连接于所述采样模块的输出端,用于基于sigma-delta调制器架构对所述模拟信号执行至少2阶的噪声整形,得到滤波信号;

7、量化模块,电性连接于所述滤波模块的输出端,用于异步采样所述滤波信号,输出至少4bit量化信号。

8、本技术在一较佳示例中可以进一步配置为:所述滤波模块对所述模拟信号进行2-4阶噪声整形。

9、本技术在一较佳示例中可以进一步配置为:所述滤波模块采用ciff/cifb/crff/crfb调制器中的任一种。

10、本技术在一较佳示例中可以进一步配置为:所述量化模块输出4-8bit量化信号。

11、本技术在一较佳示例中可以进一步配置为:所述滤波模块包括0阶保持器、第一积分器、第二积分器、第一加法器、第二加法器和第一延时模块;

12、所述0阶保持器的输入端接入采样电压,所述0阶保持器的输出端连接所述第一积分器的输入端,所述第一积分器的输出端连接所述第一加法器的一输入端,所述采样模块的输出端连接所述第二积分器的输入端,所述第二积分器的输出端连接所述第一加法器的另一输入端,所述第一加法器的输出端连接所述第二加法器的一输入端,所述第二加法器的输出端连接所述第一延时模块的输入端,所述第一延时模块的输出端连接所述第二加法器的另一输入端。

13、本技术在一较佳示例中可以进一步配置为:所述滤波模块还包括第三积分器、第三加法器和第二延时模块;

14、所述第一延时模块的输出端还与所述第三积分器的输入端连接,所述第三积分器的输出端与所述第三加法器的一输入端连接,所述第三加法器的输出端连接所述第二延时模块的输入端,所述第二延时模块的输出端连接所述第三加法器的另一输入端。

15、本技术在一较佳示例中可以进一步配置为:所述滤波模块还包括第四积分器、第五积分器、第六积分器和第四加法器,所述第二延时模块经所述第四加法器连接所述量化模块的输入端;

16、所述第二延时模块的输出端与所述第四积分器的输入端连接,所述第四积分器的输出端与所述第四加法器的一输入端连接;

17、所述第一延时模块的输出端与所述第五积分器的输入端连接,所述第五积分器的输出端与所述第四加法器的另一输入端连接;

18、所述0阶保持器的输出端与所述第六积分器的输入端连接,所述第六积分器的输出端与所述第四加法器的又一输入端连接。

19、本技术在一较佳示例中可以进一步配置为:所述量化模块为adc量化器。

20、本技术在一较佳示例中可以进一步配置为:所述adc量化器包括异步sar逻辑的比较器,所述第二延时模块的输出端连接所述比较器的输入端。

21、本技术在一较佳示例中可以进一步配置为:所述采样模块包括电容阵列式dac量化器。

22、本技术在一较佳示例中可以进一步配置为:所述电容阵列由相同数值大小的电容并联形成。

23、本技术在一较佳示例中可以进一步配置为:还包括,

24、工作空间模块,电性连接于所述量化模块,用于存储所述量化信号。

25、第二方面,本技术提供一种复合adc电路的音频主动降噪方法。

26、本技术是通过以下技术方案得以实现的:

27、一种复合adc电路的音频主动降噪方法,包括以下步骤,

28、触发dac量化器获取采样信号,并转化为模拟信号输出;

29、基于sigma-delta调制器架构对所述模拟信号执行至少2阶的噪声整形,得到滤波信号;

30、采用adc量化器异步采样所述滤波信号,输出至少4bit量化信号。

31、本技术在一较佳示例中可以进一步配置为:所述adc量化器异步采样所述滤波信号的步骤包括,

32、启动外部时钟;

33、比较器响应于所述外部时钟执行一次采样转化,以及

34、所述比较器每次比较完成时产生时钟,推动多bit的电荷充放电/比较。

35、本技术在一较佳示例中可以进一步配置为:所述dac量化器获取采样信号,并转化为模拟信号输出的步骤包括,

36、基于电容阵列电荷充放电方式,结合输入数字码的总数量,确定目标电容;

37、响应于所述外部时钟,所述目标电容依次参与电荷转换积分,完成电容电压转换,输出模拟信号。

38、本技术在一较佳示例中可以进一步配置为:令所述目标电容参与电荷转换积分的步骤前,还包括,

39、引入一比所述外部时钟更高频率的第二时钟;

40、在所述第二时钟翻转时,响应于所述外部时钟,所述目标电容依次参与电荷转换积分,其中,各目标电容的单位电容总数不变。

41、本技术在一较佳示例中可以进一步配置为:所述噪声整形的阶数与所述adc量化器的bit数值满足以下关系式,

42、snrmax=10*lg[1.5*(2l+1)/(pi2l)*osr(2l+1)*2(n-1)]

43、式中,snrmax为目标信噪比上限,l为噪声整形的阶数,osr为adc量化器的过采样率,n为adc量化器的bit数值,pi为常数。

44、第三方面,本技术提供一种集成电路。

45、本技术是通过以下技术方案得以实现的:

46、一种集成电路,包括上述任意一项所述的用于音频主动降噪功能的复合adc电路。

47、第四方面,本技术提供一种音频处理芯片。

48、本技术是通过以下技术方案得以实现的:

49、一种音频处理芯片,包括集成电路,所述集成电路包括上述任意一项所述的用于音频主动降噪功能的复合adc电路。

50、第五方面,本技术提供一种便携式入耳耳机。

51、本技术是通过以下技术方案得以实现的:

52、一种便携式入耳耳机,包括麦克风和扬声器,所述麦克风和所述扬声器之间电性连接有上述任意一项所述的用于音频主动降噪功能的复合adc电路。

53、综上所述,与现有技术相比,本技术提供的技术方案带来的有益效果至少包括:

54、基于sigma-delta调制器架构实现至少2阶的频谱搬移或者噪声整形,使得过采样率可以只配置32或者16,同时量化部分采用异步采样结构直接输出至少4bit量化信号,实现采样率高且功耗较低的目的,以在电路整体信噪比不降低的前提下,使得数字滤波器的延时大大减小,满足主动降噪的处理时间要求,能够适用于主动降噪音频adc的低延时、高精度和低功耗的要求。

本文地址:https://www.jishuxx.com/zhuanli/20240618/20877.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。