栅极驱动电路、显示面板及其驱动方法与流程

- 国知局

- 2024-06-21 13:42:38

本发明涉及显示,具体涉及栅极驱动电路、显示面板及其驱动方法。

背景技术:

1、oled显示技术具备高对比、快速响应、低功耗等优势。为了进一步降低功耗,采用ltps+igzo结合而实现的ltpo显示技术可以实现低帧频显示,通过减少静态画面的反复刷新来降低驱动功耗。但现有的oled显示器在更新画面时,仍然需要在一帧内对全部像素电压进行初始化和写入。而在某些特殊画面下(如常亮显示画面、静态画面或较少更新的画面等),整屏绝大部分像素电压不需要更新,即可以通过低漏电的ltpo tft维持在原有的显示亮度,对这些像素的反复刷写造成了数据线功耗的浪费。局部刷新栅极驱动(gate driveron array,goa)电路,可以实现屏幕局部画面的更新,而其余画面则不需要多次充放电,从而进一步降低oled显示的功耗,或通过显示画面局部更新实现穿戴、mobile、nb等oled产品的超低功耗。

2、然而,相关技术中局部刷新的goa电路中,多行goa单元共用同一选通信号ms(即大小相等),当选通信号ms输出高电平信号时,多行goa单元的输出信号存在差异,造成显示面板亮度不均匀、出现横纹现象。

技术实现思路

1、为了解决上述问题,发明人通过研发找到了问题的成因,并形成了解决方案。

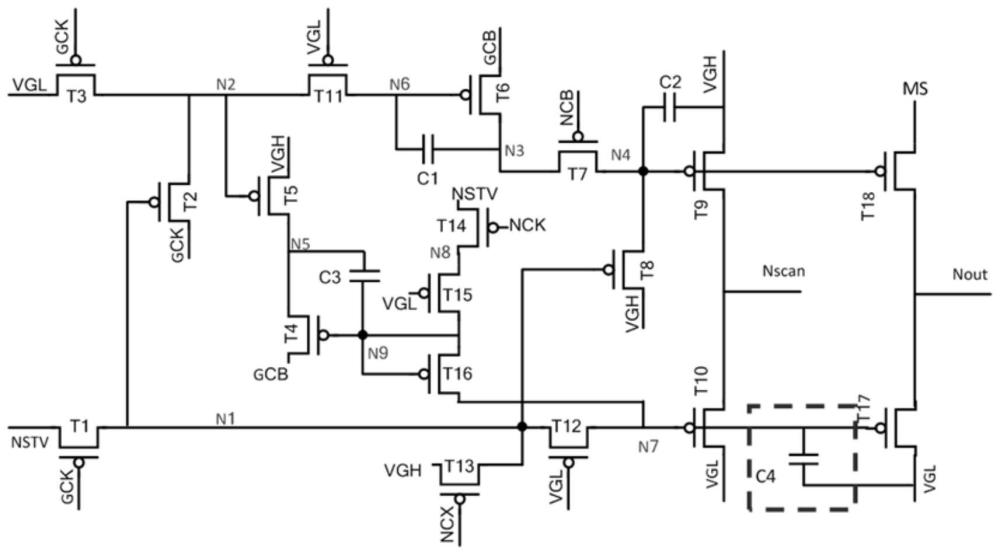

2、第一方面,本发明提供一种栅极驱动电路,该栅极驱动电路包括多行栅极驱动单元,

3、其中,每行栅极驱动单元包括移位寄存器和与其连接的选通电路,

4、所述多行栅极驱动单元的移位寄存器级联,以使得前一级的移位寄存器输出的扫描信号传输至后一级移位寄存器;

5、每个选通电路被配置为,接收选通信号并且当所述扫描信号为第一电平信号以及所述选通信号为第二电平信号时,通过各自的输出端输出有效电平信号,当所述扫描信号为第三电平信号或者所述选通信号为第四电平信号时,通过各自的输出端输出非有效电平信号,

6、并且其中,所述多行栅极驱动单元被划分为至少1组,同组中每个选通电路被配置为在所输出的有效电平信号与非有效电平信号转换时所形成的下降沿趋于一致。

7、进一步地,上述所述的栅极驱动电路中,所述选通电路包括第一输出子电路和第二输出子电路;

8、所述第一输出子电路的控制端与所述移位寄存器电连接;

9、所述第一输出子电路的输入端与选通信号端电连接,用于接收所述选通信号;

10、所述第一输出子电路的输出端与所述第二输出子电路的输出端电连接;

11、所述第二输出子电路的控制端与所述移位寄存器电连接;

12、所述第二输出子电路的输入端与电源端电连接;其中,所述电源端用于输入所述第三电平信号;

13、同组中的所述第二输出子电路被配置为使得所述输出端在所输出的有效电平信号与非有效电平信号转换时所形成的下降沿趋于一致。

14、进一步地,上述所述的栅极驱动电路中,所述第二输出子电路包括控制晶体管;

15、所述控制晶体管的栅极作为所述第二输出子电路的控制端;

16、所述控制晶体管的第一极作为第二输出子电路的输入端;

17、所述控制晶体管的第二极作为所述第二输出子电路的输出端;

18、其中,同组中的所述控制晶体管的沟道宽长比被配置为使得所述输出端在所输出的有效电平信号与非有效电平信号转换时所形成的下降沿趋于一致。

19、进一步地,上述所述的栅极驱动电路中,同组中的控制晶体管的沟道宽长比被配置为:

20、前一级移位寄存器的控制晶体管的沟道宽长比小于后一级移位寄存器的控制晶体管的沟道宽长比。进一步地,上述所述的栅极驱动电路中,同组中的控制晶体管的沟道宽长比被配置为:

21、同组中的控制晶体管的沟道长度不变时,前一级移位寄存器的控制晶体管的沟道宽度小于后一级移位寄存器的控制晶体管的沟道宽度;或者,

22、同组中的控制晶体管的沟道宽度不变时,前一级移位寄存器的控制晶体管的沟道长度大于后一级移位寄存器的控制晶体管的沟道长度;或者,

23、前一级移位寄存器的控制晶体管的沟道宽度小于后一级移位寄存器的控制晶体管的沟道宽度,前一级移位寄存器的控制晶体管的沟道长度大于后一级移位寄存器的控制晶体管的沟道长度。

24、进一步地,上述所述的栅极驱动电路中,同组中的控制晶体管被划分为至少2个子组;

25、其中,每个子组中的控制晶体管的沟道宽长比相同;前一级子组的控制晶体管的沟道宽长比小于后一级子组的控制晶体管的沟道宽长比。

26、进一步地,上述所述的栅极驱动电路中,同组中的控制晶体管的沟道宽长比被配置为:

27、同组中的控制晶体管的沟道长度不变时,前一级子组的控制晶体管的沟道宽度小于后一级子组的控制晶体管的沟道宽度;或者,

28、同组中的控制晶体管的沟道宽度不变时,前一级子组的控制晶体管的沟道长度大于后一级子组的控制晶体管的沟道长度;或者,

29、前一级子组的控制晶体管的沟道宽度小于后一级子组的控制晶体管的沟道宽度,前一级子组的控制晶体管的沟道长度大于后一级子组的控制晶体管的沟道长度。

30、进一步地,上述所述的栅极驱动电路中,所述第二输出子电路包括控制晶体管和补偿电容;

31、所述控制晶体管的栅极作为所述第二输出子电路的控制端;

32、所述控制晶体管的第一极作为第二输出子电路的输入端;

33、所述控制晶体管的第二极作为所述第二输出子电路的输出端;

34、所述补偿电容的第一端与所述控制晶体管的栅极电连接;

35、所述补偿电容的第二端与所述控制晶体管的第一极电连接,和/或,所述补偿电容的第三端与所述控制晶体管的第二极电连接;

36、同组中的补偿电容被配置为使得所述输出端在所输出的有效电平信号与非有效电平信号转换时所形成的下降沿趋于一致。

37、进一步地,上述所述的栅极驱动电路中,同组中的控制晶体管的沟道宽长比还被配置为使得所述输出端在所输出的有效电平信号与非有效电平信号转换时所形成的下降沿趋于一致。

38、进一步地,上述所述的栅极驱动电路中,所述补偿电容包括第一电容和/或第二电容;

39、所述第一电容的第一端与所述控制晶体管的栅极电连接;所述第一电容的第二端与所述电源端电连接;

40、所述第二电容的第一端与所述控制晶体管的栅极电连接;所述第二电容的第二端与所述控制晶体管的输出端电连接;

41、同组中的第一电容被配置为在前行的第一电容的容值大于在后行的第一电容的容值;

42、同组中的第二电容被配置为在前行的第二电容的容值小于在后行的第二电容的容值。

43、第二方面,本发明提供一种显示面板,该显示面板包括:

44、多个像素电路;

45、多条栅线,与所述多个像素电路电连接;

46、如上任一项所述的栅极驱动电路,

47、其中,所述栅极驱动电路中多行栅极驱动单元的每行选通电路与对应的栅线电连接,向对应的栅线提供有效电平信号或非有效电平信号。

48、第三方面,本发明提供一种如上所述的显示面板的驱动方法,述方法包括:

49、确定待刷新的一个或多个像素行;

50、当前为待刷新像素行对应的扫描时段时,控制待刷新像素行对应的移位寄存器输出第一电平信号的扫描信号,以及,控制所述选通电路输入第二电平信号的选通信号,使得待刷新像素行对应的选通电路向对应的栅线输出有效电平信号,以对所述待刷新像素行进行刷新;

51、当前为非刷新像素行对应的扫描时段时,控制非刷新像素行对应的移位寄存器输出第三电平信号的扫描信号,使得非刷新像素对应的选通电路向对应的栅线输出非有效电平信号,从而不对所述非刷新像素行进行刷新。

52、本发明上述一个或多个技术方案,至少具有如下一种或多种有益效果:

53、在实施本发明的技术方案时,通过将goa电路的用于局部刷新的选通电路进行差异化设置,以便同组中每个选通电路在有效电平信号与非有效电平信号之间相互转换时,使各自的输出端nout的输出信号所形成的下降沿趋于一致。这样,在多行goa单元接收同一选通信号ms的情况下,可以将其中每行goa单元的输出能力趋于一致,从而使得面板的亮度比较均匀、避免出现横纹现象,以及,避免在不同组goa单元的分界处产生亮暗分界线。

本文地址:https://www.jishuxx.com/zhuanli/20240618/34093.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表