半导体用支承玻璃基板及使用其的层叠基板的制作方法

- 国知局

- 2024-06-20 13:12:31

本发明涉及半导体用支承玻璃基板及使用其的层叠基板,具体而言,涉及在半导体封装体的制造工序中用于支承半导体基板的半导体用支承玻璃基板及使用其的层叠基板。

背景技术:

1、对于便携电话、笔记本电脑、pda(personal data assistance)等便携型电子设备,要求小型化及轻量化。与此相伴随,这些电子设备中使用的半导体芯片的安装空间也受到严格限制,半导体芯片的高密度安装成为课题。因此,近年来,通过三维安装技术、即将半导体芯片彼此层叠、对各半导体芯片间进行布线连接,来谋求半导体封装体的高密度安装。

技术实现思路

1、发明要解决的课题

2、随着三维安装技术的进步,对半导体基板以数十nm水平的精度实施图案化,即使在仅发生数十nm的尺寸变化的情况下,也成为成品率降低的原因。为了抑制半导体基板的尺寸变化,使用用于支承半导体基板的支承玻璃基板是有效的,使用平坦的支承玻璃基板特别有效。

3、但是,若使用平坦的支承玻璃基板,则在半导体封装体的制造工序中容易产生由静电带来的问题。即,在半导体封装体的制造工序中,支承玻璃基板与平台反复接触剥离。若反复该接触剥离,则支承玻璃基板内的带电量增加而使引入绝缘破坏的可能性变高。另外,在支承玻璃基板与平台的热膨胀系数差大的情况下,在热工艺中因支承玻璃基板与平台的摩擦而使支承玻璃基板带电,从而还存在引起绝缘破坏的风险。若使支承玻璃基板绝缘破坏,则污染半导体基板而成为成本高的原因。

4、本发明是鉴于上述情况而完成的发明,其技术课题在于通过发明出在半导体封装体的制造工序中难以绝缘破坏的支承玻璃基板而有助于半导体封装体的高密度安装。

5、用于解决课题的手段

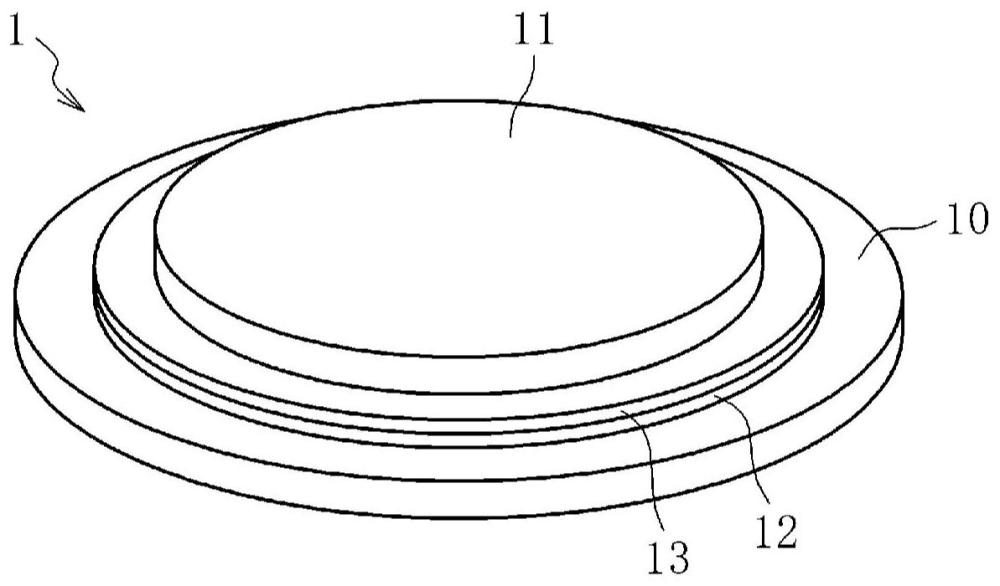

6、本发明人等反复进行了各种实验,结果发现可以通过在玻璃基板的表面形成特定的粗糙面化区域来解决上述的技术课题,从而提出本发明。即,本发明的半导体用支承玻璃基板,其特征在于,具有成为层叠半导体基板的一侧的第一表面和与第一表面相反侧的表面即第二表面,并在第一表面及第二表面中的至少一面上具有表面粗糙度ra为0.3nm以上且表面粗糙度rmax为100nm以下的粗糙面化区域。在此,“表面粗糙度ra”和“表面粗糙度rmax”是使用扫描型探针显微镜(例如bruker公司制dimension icon)在5μm见方的面积进行测定得到的值。例如在玻璃基板的第二表面的整面形成粗糙面化区域的情况下,对玻璃基板的面内中央部和周边部(距离玻璃基板的端面约50mm内侧的部分)的9个位置在5μm见方的面积分别测定表面粗糙度ra和rmax时的平均值。

7、本发明的半导体用支承玻璃基板在至少一个表面具有表面粗糙度ra为0.3nm以上的粗糙面化区域。由此,使支承玻璃基板与平台的接触面积变小,并且可以降低支承玻璃基板内的带电量。另一方面,若粗糙面化区域的表面粗糙度rmax过大,则在支承玻璃基板产生微裂纹,使支承玻璃基板的强度容易降低。为此,本发明的半导体用支承玻璃基板将粗糙面化区域的表面粗糙度rmax限制为100nm以下。

8、第二,本发明的半导体用支承玻璃基板优选使粗糙面化区域形成于第二表面。

9、第三,本发明的半导体用支承玻璃基板优选使粗糙面化区域形成于以面积比计为第二表面的5%以上。

10、第四,本发明的半导体用支承玻璃基板优选使粗糙面化区域形成于第一表面和第二表面这两个面。这样一来,不仅在使支承玻璃基板与平台接触时,而且在剥离半导体基板时也可以降低支承玻璃基板内的带电量。

11、第五,本发明的半导体用支承玻璃基板优选在粗糙面化区域内存在圆弧状的研磨痕。这样一来,不仅支承玻璃基板内的带电量降低,而且支承玻璃基板的整体板厚偏差也容易降低。

12、第六,本发明的半导体用支承玻璃基板优选使整体板厚偏差为3.0μm以下。这样一来,容易提高加工处理的精度。尤其可以提高布线精度,因此能够进行高密度的布线。另外,使支承玻璃基板的强度提高,并且支承玻璃基板及层叠基板不易破损。进而,可以增加支承玻璃基板的再利用次数。在此,“整体板厚偏差”为支承玻璃基板整体的最大板厚与最小板厚之差,例如可以利用神钢(kobelco)科研公司制的bow/warp测定装置sbw-331ml/d进行测定。

13、第七,本发明的半导体用支承玻璃基板优选使板厚不足2.0mm且翘曲量为60μm以下。在此,“翘曲量”是指支承玻璃基板整体的最高位点与最小二乘焦点面之间的最大距离的绝对值和最低位点与最小二乘焦点面的绝对值的总和,例如可以利用神钢(kobelco)科研公司制的bow/warp测定装置sbw-331ml/d进行测定。

14、第八,本发明的层叠基板优选为至少具备半导体基板和用于支承半导体基板的半导体用支承玻璃基板的层叠基板、且半导体用支承玻璃基板为上述的半导体用支承玻璃基板。

15、第九,本发明的层叠基板优选使半导体用支承玻璃基板在20~260℃时的平均热膨胀系数为50×10-7/℃以上、且半导体基板至少具备被密封材密封的半导体芯片。在此,“在20~260℃时的平均热膨胀系数”可以利用热膨胀仪进行测定。

16、作为新的wlp,提出了fan-out型的wlp。fan-out型的wlp能够使引脚数增加,并且通过保护半导体芯片的端部,从而可以防止半导体芯片的缺口等。fan-out型的wlp中,将多个半导体芯片用树脂密封材料进行密封而形成加工基板后,具有在加工基板的一个表面进行布线的工序、形成焊料凸块的工序等。这些工序由于伴随有约200℃~300℃的热处理,因此有密封材料变形而使半导体基板发生尺寸变化之担忧。若半导体基板发生尺寸变化,则难以对半导体基板的一个表面进行高密度布线,另外,也难以准确地形成焊料凸块。

17、如上所述,为了抑制半导体基板的尺寸变化,使用支承玻璃基板是有效的,但即使在使用支承玻璃基板的情况下,有时在半导体基板内半导体芯片的比例多且密封材的比例少时也会发生半导体基板的翘曲变形。为此,若如上述那样地规定支承玻璃基板的平均热膨胀系数,则即使在半导体基板内半导体芯片的比例多且密封材的比例少的情况下,也可以抑制半导体基板的翘曲变形。

18、第十,本发明的层叠基板优选使半导体用支承玻璃基板为无碱玻璃且半导体基板具备硅晶片。在此,“无碱玻璃”是指玻璃组成中的碱成分(li2o、k2o、na2o)的含量为0.5质量%以下的玻璃。

技术特征:1.一种半导体用支承玻璃基板,其特征在于,具有成为层叠半导体基板的一侧的第一表面和与第一表面相反侧的表面即第二表面,

2.根据权利要求1所述的半导体用支承玻璃基板,其特征在于,粗糙面化区域形成于第二表面。

3.根据权利要求2所述的半导体用支承玻璃基板,其特征在于,粗糙面化区域形成于以面积比计为第二表面的5%以上。

4.根据权利要求1或2所述的半导体用支承玻璃基板,其特征在于,粗糙面化区域形成于第一表面和第二表面这两个面。

5.根据权利要求1或2所述的半导体用支承玻璃基板,其特征在于,在粗糙面化区域内存在圆弧状的研磨痕。

6.根据权利要求1或2所述的半导体用支承玻璃基板,其特征在于,整体板厚偏差为3.0μm以下。

7.根据权利要求1或2所述的半导体用支承玻璃基板,其特征在于,板厚不足2.0mm且翘曲量为60μm以下。

8.一种层叠基板,其特征在于,是至少具备半导体基板和用于支承半导体基板的半导体用支承玻璃基板的层叠基板,半导体用支承玻璃基板为权利要求1~7中任一项所述的半导体用支承玻璃基板。

9.根据权利要求8所述的层叠基板,其特征在于,半导体用支承玻璃基板在20℃~260℃时的平均热膨胀系数为50×10-7/℃以上,且半导体基板至少具备被密封材密封而成的半导体芯片。

10.根据权利要求8所述的层叠基板,其特征在于,半导体用支承玻璃基板为无碱玻璃,且半导体基板具有硅晶片。

技术总结本发明涉及半导体用支承玻璃基板及使用其的层叠基板,其技术课题在于通过发明出在半导体封装体的制造工序中难以绝缘破坏的支承玻璃基板而有助于半导体封装体的高密度安装。本发明的半导体用支承玻璃基板,其特征在于,具有成为层叠半导体基板的一侧的第一表面和与第一表面相反侧的表面即第二表面,并在第一表面及第二表面中的至少一面上具有表面粗糙度Ra为0.3nm以上且表面粗糙度Rmax为100nm以下的粗糙面化区域。技术研发人员:柳濑智基受保护的技术使用者:日本电气硝子株式会社技术研发日:技术公布日:2024/6/5本文地址:https://www.jishuxx.com/zhuanli/20240619/7853.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表