基于声子辅助的量子比特三维集成装置

- 国知局

- 2024-07-27 12:42:20

1.本发明涉及半导体领域,尤其涉及基于声子辅助的量子比特集成阵列装置。背景技术:2.近年来量子信息科技的发展十分迅速,在各个国家大力发展的尖端科技领域中具有重要的战略地位。谷歌、ibm、微软等公司十分看重量子计算的商业价值,在量子计算领域投入了大量的资金和科研资源,取得的成果进展相继发表在nature、science等顶级学术刊物。2019年martinis团队在nature发表论文宣告人类首次实现了“量子霸权”,引起了不小的轰动。martinis团队开发的“sycamore”处理器处理传统计算机需要10000年才能算出结果的问题仅需要20秒。“sycamore”处理器的问世在量子计算领域中具有里程碑意义,它让人们看到了量子计算惊人的发展潜力,引起了一波量子计算的研究热潮。目前已经出现了超导量子计算、半导体量子计算、离子阱量子计算、拓扑量子计算等各种各样具有特色的量子计算系统。我们用一维纳米线(管)中的量子点作为量子比特构造一种可扩展的三维量子计算阵列装置。通过量子点与声子的相互作用、声子与声子的相互作用来实现多个量子点的耦合。技术实现要素:3.本发明提供一种基于声子辅助的量子比特三维集成装置,其目的在于通过微纳加工工艺制作三维电极结构,并利用多根碳纳米管在电极阵列上形成可扩展的量子比特阵列。碳纳米管通过电压调节形成量子点结构可构建量子比特,同时碳纳米管振动时形成的机械模式可作为声子腔提供并传递声子,借助量子点与声子间相互作用、声子与声子间相互作用实现量子比特的二维可扩展集成。本装置整体尺寸小,结构简单,与现有微电子工艺兼容,有望实现半导体量子计算芯片的大规模集成。4.为实现上述发明目的,本发明技术方案如下:5.一种基于声子辅助的量子比特三维集成装置,包括基片、基片上形成的量子点系统、辅助声子腔系统和三维电极系统;所述量子点系统和辅助声子腔系统由一维纳米线管结构通过电极系统调控形成;6.所述量子点系统:用于形成量子比特,7.所述辅助声子腔系统:位于两个量子点系统之间,用于借助声子-声子相互作用实现不同量子点之间的间接耦合;8.所述三维电极系统:包括内电极、绝缘层、点阵电极、连接电极;9.所述内电极:生长在基片上方,包括内源极、内栅极,内电极用于连接外部电压源、微波源及测控设备,为点阵电极供电;内栅极位于两个相邻的内源极之间的中点;10.所述绝缘层:位于内电极和基片之上;11.所述点阵电极:位于绝缘层之上,包括外源极611和外栅极612,外源极用于搭载量子点和声子腔,外源极和外栅极用于测量及调控量子点和声子腔;外源极在x和y方向上形成矩形阵列,沿x和y方向相邻的外源极611之间设有一个外栅极612;在绝缘层的平面上,外源极611和外栅极612从左至右交替排列的方向为x方向,y方向与x方向垂直;12.所述连接电极:用于连接内源极和外源极,并连接内栅极和外栅极;13.所述一维纳米线管结构:搭在或生长在点阵电极的外源极上方,在x和y方向上形成二维阵列;所述一维纳米线管结构的机械振动成的声子和量子点系统实现耦合,多个纳米线管构建成的二维阵列用于实现量子比特的集成化;14.所述量子比特三维集成装置通过电极调控由多个一维纳米线管构成的二维量子比特网状阵列中的量子点,多个量子点系统通过辅助声子腔系统、借助量子点与声子的相互作用、声子与声子的相互作用,实现间接耦合。15.作为优选方式,一维纳米线管结构为碳纳米管或硅纳米线。16.作为优选方式,辅助声子腔系统与量子点系统均由一维纳米线管结构形成。17.作为优选方式,所述三维电极系统共包括16个外源极、24个外栅极、40个连接电极、16个内源极、24个内栅极,16个外源极以4*4的结构组成阵列装置的基础框架,即4个横排和4个纵列,24个外栅极则分布在沿x和y方向相邻的外源极之间。18.作为优选方式,一维纳米线管结构通过电压的调控形成量子点。19.作为优选方式,量子点和声子腔作为一个整体搭在外源极上,一共有8根碳纳米管来形成二维量子比特网状阵列,其中4根碳纳米管横向搭在4横排的外源极上,剩余的4根碳纳米管纵向搭在4纵列的外源极上。20.作为优选方式,绝缘层由二氧化硅构成。用于防止电极之间出现漏电串扰的情况,起到保护作用,同时用于支撑连接电极。21.作为优选方式,内源极和内栅极宽度为1微米,两个相邻的内源极的间距为2微米,内源极和内栅极的镀膜厚度均为25纳米,由20纳米厚的金和5纳米厚的钛构成;镀膜速度为真空度为10-7mbar。22.本发明的工作过程和工作原理为:利用电子-声子相互作用、声子-声子相互作用,以声子腔为媒介在阵列装置上实现大规模的量子比特耦合。一维纳米线管形成的量子点与机械振动形成的声子模式耦合,相邻振子的声子模式通过声子腔与已经和量子点耦合的声子模式进行耦合。阵列上的量子点以相同的方式与声子腔耦合。23.本发明的有益效果为:碳纳米管具有尺寸小、质量轻、品质因子高等优点,所以选择碳纳米管作为阵列装置的主体。装置整体尺寸为微米量级,外部结构简单,有望在量子芯片上实现一定规模的集成。制作工艺为传统的半导体微纳加工工艺,易于大规模制作。附图说明24.图1为本发明装置的整体结构示意图。25.图2为本发明装置的俯视示意图。26.图3为本发明装置的主视剖面示意图。27.图4为本发明内电极的结构示意图。填充部分为内源极,未填充部分为内栅极。28.1为基片,2为绝缘层,3为量子点系统,4为辅助声子腔系统,5为一维纳米线管,6为三维电极系统,61为点阵电极,611为外源极,612为外栅极,62为内电极,621为内源极,622为内栅极,63为连接电极。具体实施方式29.下面结合附图和具体实施例进一步说明本发明的技术方案。30.一种基于声子辅助的量子比特三维集成装置,包括基片、基片上形成的量子点系统、辅助声子腔系统和三维电极系统;所述量子点系统和辅助声子腔系统由一维纳米线管结构通过电极系统调控形成;31.所述量子点系统:用于形成量子比特,32.所述辅助声子腔系统:位于两个量子点系统之间,用于借助声子-声子相互作用实现不同量子点之间的间接耦合;33.所述三维电极系统:包括内电极、绝缘层、点阵电极、连接电极;34.所述内电极:生长在基片上方,包括内源极、内栅极,内电极用于连接外部电压源、微波源及测控设备,为点阵电极供电;内栅极位于两个相邻的内源极之间的中点;35.所述绝缘层:位于内电极和基片之上;36.所述点阵电极:位于绝缘层之上,包括外源极611和外栅极612,外源极用于搭载量子点和声子腔,外源极和外栅极用于测量及调控量子点和声子腔;外源极在x和y方向上形成矩形阵列,沿x和y方向相邻的外源极611之间设有一个外栅极612;在绝缘层的平面上,外源极611和外栅极612从左至右交替排列的方向为x方向,y方向与x方向垂直;37.所述连接电极:用于连接内源极和外源极,并连接内栅极和外栅极;38.所述一维纳米线管结构:搭在或生长在点阵电极的外源极上方,在x和y方向上形成二维阵列;所述一维纳米线管结构的机械振动成的声子和量子点系统实现耦合,多个纳米线管构建成的二维阵列用于实现量子比特的集成化;39.所述量子比特三维集成装置通过电极调控由多个一维纳米线管构成的二维量子比特网状阵列中的量子点,多个量子点系统通过辅助声子腔系统、借助量子点与声子的相互作用、声子与声子的相互作用,实现间接耦合。40.一维纳米线管结构为碳纳米管或硅纳米线。41.辅助声子腔系统与量子点系统均由一维纳米线管结构形成。42.本实施例中,所述三维电极系统共包括16个外源极、24个外栅极、40个连接电极、16个内源极、24个内栅极,16个外源极以4*4的结构组成阵列装置的基础框架,即4个横排和4个纵列,24个外栅极则分布在沿x和y方向相邻的外源极之间。43.一维纳米线管结构通过电压的调控形成量子点。44.量子点和声子腔作为一个整体搭在外源极上,一共有8根碳纳米管来形成二维量子比特网状阵列,其中4根碳纳米管横向搭在4横排的外源极上,剩余的4根碳纳米管纵向搭在4纵列的外源极上。45.绝缘层由二氧化硅构成。用于防止电极之间出现漏电串扰的情况,起到保护作用,同时用于支撑连接电极。46.基片由本征硅和两微米的氧化硅构成。本实施例在1cm*1cm的底片基础之上来制作装置。47.清洗基片,用丙酮和去离子水分别清洗基片各1分钟,并且用超声仪震荡。48.基片洗好后用电子束曝光的方式制作内源极和内栅极,在电极附近套刻标记后依次进行匀电子束胶、烤胶、电子束曝光、显影、电子束镀膜和金属剥离。内源极和内栅极的结构如图4所示。49.内源极和内栅极宽度为1微米,两个相邻的内源极的间距为2微米,内栅极居中位于两个相邻的内源极之间。内源极和内栅极的镀膜厚度均为25纳米,由20纳米厚的金和5纳米厚的钛构成。镀膜速度为真空度为10-7mbar。50.内源极和内栅极制作完成后,将带有套刻标记100纳米厚的二氧化硅覆盖在基片上。用氢氟酸在标记的位置刻蚀出直径为50纳米的圆形沟道用于制作连接电极、外源极和外栅极。51.沟道的位置即为点阵电极(外源极和外栅极)的位置,刻蚀完成后依次进行匀电子束胶、烤胶、电子束曝光、显影、电子束镀膜和金属剥离来制作连接电极、外源极和外栅极。一部分金属镀膜在沟道内形成的金属柱为连接电极,位于二氧化硅层外表面的电极即为点阵电极。连接电极和点阵电极均由金来制作。52.点阵电极的长和宽均为1微米。其中外源极的镀膜厚度为200纳米,外栅极的镀膜厚度为50纳米。两个相邻外源极的间距为2微米,外栅极居中位于两个相邻外源极之间,与基片上内源极和内栅极分布位置一致。镀膜速度为真空度为10-7mbar。53.实际应用中集成装置可以根据芯片的使用需求扩展到更高的维度。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123102.html

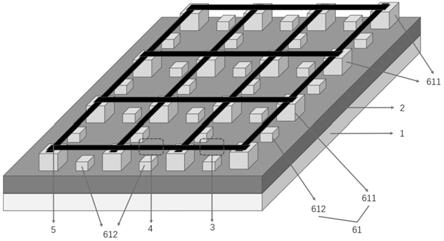

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。