一种参考电压浮动的控制电路的制作方法

- 国知局

- 2024-07-31 23:34:59

本发明涉及集成电路领域,特别是双电源供电的集成电路领域,特别是双电源供电的功率放大器领域。

背景技术:

1、集成电路产品内部常常需要使能、过流保护、过温保护。使能是利用外部端口进行控制,在使能情况下允许各模块正常工作,在关断情况下禁止部分模块工作以节省电流,其中对节省电流最为有效的是关断输出器件。过流保护是用于将输出器件的输出电流限制在一定值以内。如果输出电流达到过流保护阈值,则防止输出电流进一步增大。根据不同的需要,过流保护阈值有时需要在外部进行调整。过温保护是使在正常温度情况下允许各模块正常工作,在温度过高的情况下禁止部分模块工作,特别是禁止输出器件工作,以防止芯片温度进一步升高。

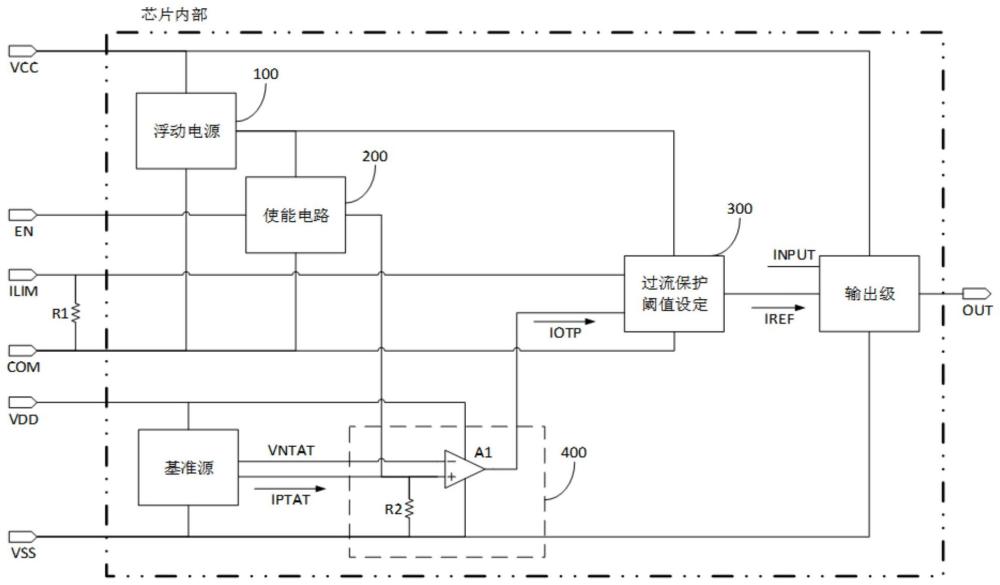

2、如图1所示现有技术中典型的使能、过流保护、过温保护的功能框图。图中vcc为高压正电源,vss为负电源,vdd为低压电源;vdd可以由芯片内部产生,也可以由外部提供;en为使能端口,ilim为过流保护阈值设定端口,out为输出端口;使能电路受外部en引脚电压控制,输出控制电压信号ctrl,经由控制电路输出关断电压信号sd以关断输出级;过流保护阈值设定电路经由外部电阻r1进行过流保护阈值调整,输出电流信号iref以控制输出级的过流保护阈值,a1为迟滞比较器,a1、r2构成过温保护电路;基准源输出负温度系数电压vntat至a1的一个输入端,并且输出正温度系数电流iptat。正温度系数电流iptat流经r2生成正温度系数电压,该电压连接至a1的另一个输入端。在温度未超过过温保护阈值时,vntat小于vr1,此时a1输出为0;当温度超过过温保护阈值时,vntat大于vr1,此时a1输出过温保护电压信号otp,经由控制电路输出关断电压信号sd以关断输出级。

3、现有技术中使能电路、过流保护阈值设定电路、过温保护电路相互独立;使能关断、过温保护功能需要经由额外的控制电路对输出级进行控制;使能电路、过流保护阈值设定电路、过温保护电路以及控制电路必须接负电源vss,不能满足使能和过流保护阈值参照某浮动端口进行设置的应用。

技术实现思路

1、针对现有技术中存在的不足,本发明提供一种参考电压浮动的控制电路,并通过采用输出电流控制技术简化电路结构,该结构适用于cmos、bicmos、bcd等工艺。

2、本发明技术方案为:一种参考电压浮动的控制电路,该电路包括:过温保护电路、过流保护阈值设定电路、输出级;过温保护电路输出端连接过流保护阈值设定电路,以此控制过流保护阈值设定电路输出的阈值设定的值,过流保护阈值设定电路的输出端连接输出级,以此来控制输出级的通断;

3、当芯片正常工作时,过温保护电路输出电流信号iotp为0,过流保护阈值设定电路正常工作;

4、当芯片温度达到过温保护阈值,过温保护电路输出电流信号iotp不为0,过流保护阈值设定电路输出过流保护阈值为0,以此来关断输出级。

5、进一步的,该电路还包括电阻r1,当过温保护电路输出电流信号iotp为0时,过流保护阈值设定电路经由外部电阻r1两端的电压进行过流保护阈值调整,输出电流信号iref以控制输出级的过流保护阈值。

6、进一步的,该电路还包括:浮动电源、使能电路、基准源、高压正电源vcc、使能端口en、过流保护阈值设定端口ilim、设置使能和过流保护阈值的参考电压端口com、低压电源vdd、负电源vss;com电压不能低于vss电压;

7、浮动电源和输出级都连接vcc,浮动电源、使能电路、过流保护阈值设定电路均连接com;浮动电源提供一个相对于com的低压电源,以保证使能电路、过流保护阈值设定电路的正常工作;

8、使能电路连接en,使能电路输出电流受en和com的电压控制;若en输入使能信号,则使能电路200输出电流为0,若使能端口en输入关断信号,则使能电路200输出电流不为0;

9、ilim连接过流保护阈值设定电路,并且在ilim和com之间设置电阻r1;

10、所述过温保护电路包括:电阻r2和迟滞比较器a1;基准源输入端分别连接vdd和vss,vntat输出端连接a1的负极,iptat输出端连接a1的正极,a1的正极并连接r2的一端,r2的另一端连接vss,a1的输入电压端连接vdd,a1的输出电压端连接vss;使能电路的输出端连接a1的正极;a1的输出端连接过流保护阈值设定电路;过流保护阈值设定电路的输出端连接输出级,输出级的接地端连接vss;

11、当芯片温度达到过温保护阈值,或en输入关断信号时,过温保护电路输出电流信号iotp至过流保护阈值设定电路,将过流保护阈值设定为0,以此来关断输出级。

12、进一步的,所述浮动电源包括:电流源i1、nmos型晶体管n0、n12、n13,pmos型晶体管p0,电容c1;所述com连接n0的源极和c1的一端,n0的栅极和漏极共接后连接p0的栅极和漏极,p0的源极连接n12的源极,n12的栅极和漏极共接后连接i1的输出端和n13的栅极,c1的另一端连接n13的源极,n13的漏极和i1的输入端都连接vcc;c1与n13的源极的共节点为浮动电源的输出端。

13、进一步的,使能电路包括:pmos型晶体管p1、p2、p3、p4、p5、p11,nmos型晶体管n1、n2、n3、n4、n5、n8;所述p1的源极、p2的源极、p3的源极、p4的源极、p5的源极连接浮动电源的输出端;p1栅极和漏极、p2的栅极、p3的栅极、p4的栅极、p5的栅极、n8的漏极共接;n8的源极连接vss,n8的栅极连接过温保护电路;n1的源极、n2的源极、n3的源极、n4的源极连接com;n1的栅极和漏极、n2的栅极、p2的漏极共接;n2的漏极、p3的漏极、n5的源极和栅极、p11的栅极共接;n3的漏极接en;n3的栅极、n4的栅极和漏极、p4的漏极共接;p11的源极接p5的漏极;p11的漏极连接过温保护电路中a1的正极。

14、进一步的,所述过温保护电路包括:电流源i2,nmos型晶体管n9、n10、n11,迟滞比较器a1,电阻r2;所述i2的输入端连接vdd;n11的源极、n10的源极连接vss;n9的栅极、n10的栅极和漏极、i2的输出端与n8的栅极共接;n9的漏极连接过流保护阈值设定电路。

15、进一步的,所述过流保护阈值设定电路包括:pmos型晶体管p6、p7、p8、p9、p10,nmos型晶体管n6、n7,电阻r3、r4;p6的栅极与使能电路中p5的栅极连接,所述p6的源极、p7的源极、p8的源极、p9的源极、p10的源极共接后连接浮动电源的输出端;p6的漏极、n6的栅极和漏极共接、n7的栅极;n6的源极连接r3的一端,r3的另一端、n6的衬底极、n7的衬底极连接com;n7的源极连接r4的一端,r4的另一端连接ilim;n7的漏极、p8的漏极、p9的漏极和栅极、p10的栅极共接;p7的栅极和漏极、p8的栅极共接后连接过温保护电路;p10的漏极为输出端。

16、进一步的,所述输出级包括:nmos型晶体管n14、n15、n16、n17、n18、n19、n20、n21、n22、n23、n24,pmos型晶体管p12、p13、p14、p15、p16、p17、p18、p19、p20、p21、p22,电阻r5、r6、r7、r8、电流源i3、比较器a2、a3;所述n14的源极、n15的源极、n16的源极、n17的源极、n18的源极、n19的衬底极、n20的衬底极、n23的源极、n24的源极、r7的一端、r8的一端连接vss;n14的漏极和栅极、n15的栅极、n16的栅极共接后连接过流保护阈值设定电路;n15的漏极、p14的漏极和栅极、p15的栅极共接;p14的源极、i3的输入端、p15的源极、p17的源极、p18的衬底极、p19的衬底极、p21的源极、p22的源极、r5的一端、r6的一端连接vcc;p12的源极、p13的源极、i3的输出端共接,p12的栅极连接负输入in-,p13的栅极连接正输入in+;p12的漏极、n17的漏极、n19源极共接;p13的漏极、n20的源极、n18的漏极共接;n17的栅极、n18的栅极共接,n19的栅极、n20的栅极共接;n19的漏极、n21的源极共接,n21的栅极、n22的栅极共接,p18的栅极、p19的栅极共接;n21的漏极、p18的漏极、p16的栅极、p17的栅极共接;p18的源极与p16的漏极连接,p17的漏极与p19的源极连接;p19的漏极、n22的漏极、p20的源极、a2的输出端、p21的栅极、p22的栅极共接;n20的漏极、n22的源极、p20的漏极、a3的输出端、n23栅极、n24的栅极共接;p21的漏极与n23的漏极共接后作为输出级的输出out;r5的另一端、a3的正输入端、n23的漏极共接,r6的另一端、a3的负输入端、n24的漏极共接;p22的漏极、a2的正输入端、r7的另一端共接,p15的漏极、a2的负输入端、r8的另一端共接。

17、进一步的,所述输出级包括:nmos型晶体管n14、n15、n16、n17、n18、n19、n20、n21、n22、n23、n24,pmos型晶体管p12、p13、p14、p15、p16、p17,电阻r5、r6、r7、r8,电流源i3,电流源a2、a3;所述n14、n15、n16、n17、n18、n23、n24的漏极接地,n14的栅极和漏极、n15栅极、n16栅极共接后连接过流保护阈值设定电路;n17、n18的栅极共接;n23、n24的栅极共接;p12的漏极、n19源极、n17漏极共接,p13的漏极、n20的源极、n18的漏极共接,p12的栅极连接正输入信号in+,p13的栅极连接负输入信号in-;i3的一端、p16的源极、p17的源极、r5的一端、r6的一端、r7的一端、r8的一端连接vcc;i3的另一端、p12的源极、p13的源极共接;p16、p17的栅极共接,p14、p15的栅极共接,p14的源极、p16的漏极共接,p15的源极、p17的漏极共接;p14的漏极、a2的输出端、n21的栅极、n19的漏极共接;p15的漏极、a3的输出端、n22的栅极、n20的漏极共接;r5的另一端、a2的负输入端、n21的漏极共接,r6的另一端、a3的负输入端、n22的漏极共接,n21的源极与n23的漏极后作为输出级的正输出out+;n22的源极与n24的漏极后作为输出级的负输出out-;r7的另一端、a2的正输入端、n15的漏极共接,r8的另一端、a3的正输入端、n16的漏极共接。

18、本发明所述的参考电压浮动的控制电路,实现了参考浮动电压com进行使能控制和过流保护阈值设定,并通过使能电路和过温保护电路控制过流保护置0的方式实现了电路的简化。

本文地址:https://www.jishuxx.com/zhuanli/20240730/197909.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表