一种应用于CAN收发器的驱动电路的制作方法

- 国知局

- 2024-07-31 23:49:37

本发明涉及模拟电路设计,具体地,涉及一种应用于can收发器的驱动电路。

背景技术:

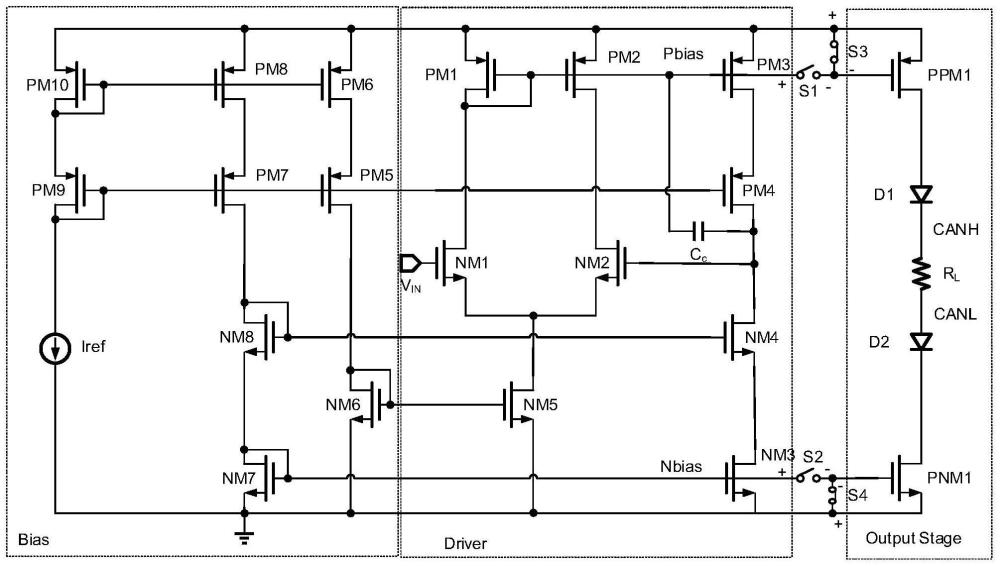

1、如图1所示是传统can收发器的驱动电路图,由基准电流源电路产生基准电流iref,利用nm1、nm2的nmos电流镜将基准电流复制到pm1上,用于产生输出级pmos pm2的驱动电压,输出级nmos nm3的驱动电压由nm1产生,当开关s1、s2闭合,s3、s4断开时,此时处于显性状态,nm1和pm1产生的偏置电压会使得输出级pmos pm2和输出级nmos nm3产生电流,电流在输出负载电阻上形成电压差canh和canl输出到总线上;当开关s1、s2断开,s3、s4闭合时,此时处于隐性状态,nm1和pm1的源极分别连接到gnd和vcc上;在稳定的显性情况下,当nm1、nm2的nmos电流镜的精度足够高时,canh和canl仍然可以保持较好的对称性,但是在从隐性向显性跳变的过程中,由于输出级pmos pm2和输出级nmos nm3的尺寸通常远大于产生偏置电压的nm1和pm1的尺寸,这就会导致在开关s1、s2闭合时,如图2中的(a),vnbias和vpbias的电压会发生的变化,由于在vnbias和vpbias处引入了较大的电容,导致vnbias的电压下降,vpbias的电压上升,此时对vnias节点的充电电流仍然是iref,但是对vpbias处的充电电流会小于iref,这导致在隐性向显性跳变的过程中,输出级pmos pm2的导通阻抗会大于输出级nmos nm3的导通阻抗,从而使得canh和canl的波形产生不对称,如图2中的(b)所示,会使得can收发器对外部其他电子元件造成较大的电磁干扰。

技术实现思路

1、针对现有技术中存在的问题,本发明提供了一种应用于can收发器的驱动电路,改善了can收发器的canh输出端、canl输出端的共模电平的稳定性,降低了在显隐跳变的过程中共模电平的变化,改善了can收发器的电磁干扰(electromagnetic interferences,emi)和电磁发射(electromagnetic emissions,eme)特性。

2、为实现上述技术目的,本发明采用如下技术方案:一种应用于can收发器的驱动电路,包括:偏置电路、负反馈驱动环路和输出级模块,所述偏置电路为负反馈驱动环路提供偏置电流,所述负反馈驱动环路通过环路控制产生使输出级模块输出电流接近输出驱动电压的偏置电压,所述输出级模块用于产生流向can收发器的电流,提高can收发器共模电压的稳定性。

3、进一步地,所述偏置电路包括:基准电流源iref、第五pmos管pm5、第六pmos管pm6、第七pmos管pm7、第八mos管pm8、第九pmos管pm9、第十pmos管pm10、第六nmos管nm6、第七nmos管nm7和第八nmos管nm8,所述第六pmos管pm6的源极、第八pmos管pm8的源极、第十pmos管pm10的源极均与电源vcc连接,所述第六pmos管pm6的栅极分别与第八pmos管pm8的栅极、第十pmos管pm10的栅极、第十pmos管pm10的漏极、第九pmos管pm9的源极连接,所述第六pmos管pm6的漏极与第五pmos管pm5的源极连接,所述第八pmos管pm8的漏极与第七pmos管pm7的源极连接,所述第九pmos管pm9的栅极、第九pmos管pm9的漏极、基准电流源iref的输入端、第七pmos管pm7的栅极、第五pmos管pm5的栅极均与负反馈驱动环路连接,所述第五pmos管pm5的漏极分别与第六nmos管nm6的漏极、第六nmos管nm6的栅极、负反馈驱动环路连接,所述第七pmos管pm7的漏极分别与第八nmos管nm8的漏极、第八nmos管nm8的栅极、负反馈驱动环路连接,所述第八nmos管nm8的源极分别与第七nmos管nm7的漏极、第七nmos管nm7的栅极、负反馈驱动环路连接,所述第七nmos管nm7的源极、第六nmos管nm6的源极、基准电流源iref的输出端均接地。

4、进一步地,所述负反馈驱动环路包括:第一级负反馈驱动环路、第二级负反馈驱动环路和电容cc,所述第一级负反馈驱动环路用于调整第一级负反馈驱动环路的输入端与第二级负反馈驱动环路的输出端之间电压的压差,所述第二级负反馈驱动环路用于提升负反馈驱动环路的增益,提高负反馈驱动环路的钳位能力,所述电容cc位于第一级负反馈驱动环路、第二级负反馈驱动环路和电容cc之间,进行米勒补偿。

5、进一步地,所述第一级负反馈驱动环路包括:由第一nmos管nm1和第二nmos管nm2组成的输入级差分管对、向输入级差分管对提供偏置电流的第五nmos管nm5、由第一pmos管pm1和第二pmos管pm2组成的输入级差分管对负载,所述第五nmos管nm5的栅极与第六nmos管nm6的栅极连接,所述第五nmos管nm5的源极接地,所述第五nmos管nm5的漏极分别与第一nmos管nm1的源极、第二nmos管nm2的源极连接,所述第一nmos管nm1的栅极与维持驱动电路工作的输入电平vin连接,所述第一nmos管nm1的漏极分别与第一pmos管pm1的漏极、第一pmos管pm1的栅极、第二pmos管pm2的栅极、电容cc的一端、第二级负反馈驱动环路的输入端、输出级模块连接,所述第一pmos管pm1的源极、第二pmos管pm2的源极均与电源vcc连接,所述第二pmos管pm2的漏极与第二nmos管nm2的漏极连接,所述第二nmos管nm2的栅极分别与电容cc的另一端、第二级负反馈驱动环路连接。

6、进一步地,所述第二级负反馈驱动环路包括:第三pmos管pm3、第一cascode管pm4、通过第八nmos管nm8提供偏置电压的第二cascode管nm4、通过第七nmos管提供偏置电压的第三nmos管nm3,所述第三pmos管pm3作为第二级负反馈驱动环路的输入级,所述第三pmos管pm3的源极与电源vcc连接,所述第三pmos管pm3的栅极分别与第二pmos管pm2的栅极、输出级模块连接,所述第三pmos管pm3的漏极与第一cascode管pm4的源极连接,所述第一cascode管pm4的栅极与第五pmos管pm5的栅极连接,所述第一cascode管pm4的漏极分别与电容cc的另一端、第二nmos管nm2的栅极、第二cascode管nm4的漏极连接,所述第二cascode管nm4的栅极与第八nmos管nm8的栅极连接,所述第二cascode管nm4的源极与第三nmos管nm3的漏极连接,所述第三nmos管nm3的栅极分别与第七nmos管nm7的栅极、输出级模块连接,所述第三nmos管nm3的源极接地。

7、进一步地,所述偏置电路包括:基准电流源iref、第六nmos管nm6、第七nmos管nm7、第八nmos管nm8、第九nmos管nm9、第十nmos管nm10、第十三nmos管nm13、第六pmos管pm6、第七pmos管pm7、第八pmos管pm8和基准电流源iref,所述基准电流源iref的输入端、第八pmos管pm8的源极、第六pmos管pm6的源极均与电源vcc连接,所述第六pmos管pm6的栅极分别与第六pmos管pm6的漏极、第十三nmos管nm13的漏极、负反馈驱动环路连接,所述第八pmos管pm8的栅极分别与第八pmos管pm8的漏极、第七pmos管pm7的源极、负反馈驱动环路连接,所述第七pmos管pm7的栅极分别与第七pmos管pm7的漏极、第八nmos管nm8的漏极、负反馈驱动环路连接,所述第八nmos管nm8的栅极分别与第九nmos管nm9的栅极、第九nmos管nm9的漏极、基准电流源iref的输出端、第十三nmos管nm13的栅极、负反馈驱动环路连接,所述第八nmos管nm8的源极与第七nmos管nm7的漏极连接,所述第九nmos管nm9的源极分别与第十nmos管nm10的漏极、第十nmos管nm10的栅极、第七nmos管nm7的栅极、第六nmos管nm6的栅极连接,所述第十三nmos管nm13的源极与第六nmos管nm6的漏极连接,所述第六nmos管nm6的源极、第七nmos管nm7的源极、第十nmos管nm10的源极均接地。

8、进一步地,所述负反馈驱动环路由第一级负反馈驱动环路、第二级负反馈驱动环路和电容cc,所述第一级负反馈驱动环路组成,所述第一级负反馈驱动环路用于调整第一级负反馈驱动环路的输入端与第二级负反馈驱动环路的输出端之间电压的压差,所述第二级负反馈驱动环路用于提升负反馈驱动环路的增益,提高负反馈驱动环路的钳位能力,所述电容cc位于第一级负反馈驱动环路、第二级负反馈驱动环路和电容cc之间,进行米勒补偿。

9、进一步地,所述第一级负反馈驱动环路包括:由第十一pmos管pm11和第十二pmos管pm12组成的输入级差分管对、向输入级差分管对提供偏置电流的第十三pmos管pm13、由第十一nmos管nm11和第十二nmos管nm12组成的输入级差分管对负载,所述第十三pmos管pm13的源极与电源vcc连接,所述第十三pmos管pm13的栅极与第六pmos管pm6的栅极连接,所述第十三pmos管pm13的漏极分别与第十一pmos管pm11的源极、第十二pmos管pm12的源极连接,所述第十一pmos管pm11的栅极与维持驱动电路工作的输入电平vin连接,所述第十一pmos管pm11的漏极分别与第十一nmos管nm11的漏极、第十一nmos管nm11的栅极、第十二nmos管nm12的栅极、电容cc的一端、第二级负反馈驱动环路的输入端连接,所述第十二pmos管pm12的栅极分别与电容cc的另一端、第二级负反馈驱动环路连接,所述第十二pmos管pm12的漏极与第十二nmos管nm12的漏极连接,所述第十一nmos管nm11的源极、第十二nmos管nm12的源极均接地。

10、进一步地,所述第二级负反馈驱动环路包括:第三nmos管nm3、第二cascode管nm4、通过第七pmos管pm7提供偏置电压的第一cascode管pm4、通过第八pmos管pm8提供偏置电压的第三pmos管pm3,所述第三nmos管nm3作为第二级负反馈驱动环路的输入级,所述第三nmos管nm3的栅极分别与第十二nmos管nm12的栅极、输出级模块连接,所述第三nmos管nm3的源极接地,所述第三nmos管nm3的漏极与第二cascode管nm4的源极连接,所述第二cascode管nm4的栅极与第十三nmos管nm13的栅极连接,所述第二cascode管nm4的漏极分别与第一cascode管pm4的漏极、电容cc的一端、第十二pmos管pm12的栅极连接,所述第一cascode管pm4的栅极与第七pmos管pm7的栅极连接,所述第一cascode管pm4的源极与第三pmos管pm3的漏极连接,所述第三pmos管pm3的栅极分别与第八pmos管pm8的栅极、输出级模块连接,所述第三pmos管pm3的源极与电源vcc连接。

11、进一步地,所述输出级模块包括:第一开关s1、第二开关s2、第三开关s3、第四开关s4、输出级pmos管ppm1、输出级nmos管pnm1、第一二极管d1、第二二极管d2和外部负载rl,所述第三开关s3的一端、输出级pmos管ppm1的源极均与电源vcc连接,所述第三开关s3的另一端分别与第一开关s1的一端、输出级pmos管ppm1的栅极连接,所述第一开关s1的另一端与第三pmos管pm3的栅极连接,所述输出级pmos管ppm1的漏极与第一二极管d1的阳极连接,所述第一二极管d1的阴极与外部负载rl的一端连接,所述外部负载rl的另一端与第二二极管d2的阳极连接,所述第二二极管d2的阴极与输出级nmos管pnm1的漏极连接,所述输出级nmos管pnm1的栅极分别与第二开关s2的一端、第四开关s4的一端连接,所述第二开关s2的另一端与第三nmos管nm3的栅极连接,所述第四开关s4的另一端、输出级nmos管pnm1的源极均接地;所述外部负载rl与第一二极管d1连接一侧作为can收发器的canh输出端,所述外部负载rl与第二二极管d2连接一侧作为can收发器的canl输出端,所述canh输出端与canl输出端输出共模电平。

12、与现有技术相比,本发明具有如下有益效果:本发明应用于can收发器的驱动电路中负反馈驱动环路的第一级负反馈驱动环路用于调整第一级负反馈驱动环路的输入端与第二级负反馈驱动环路的输出端之间电压的压差,第二级负反馈驱动环路采用cascode结构,用于提升负反馈驱动环路的增益,提高负反馈驱动环路的钳位能力,电容cc位于第一级负反馈驱动环路、第二级负反馈驱动环路和电容cc之间,进行频率补偿,使负反馈驱动环路产生输出级模块偏置电压的偏置电流一致来保证输出级pmos管ppm1和输出级nmos管pnm1的导通阻抗尽可能一致,改善了can收发器的canh输出端、canl输出端的共模电平的稳定性,降低了在显隐跳变的过程中共模电平的变化,从而减小can收发器对外部电子设备的干扰。

本文地址:https://www.jishuxx.com/zhuanli/20240730/198703.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表