半导体器件及其制作方法与流程

- 国知局

- 2024-07-31 18:07:15

本申请涉及显示,具体涉及一种半导体器件及其制作方法。

背景技术:

1、相关技术中,半导体器件在设置垂直沟道时,由于设备套刻精度限制,其源极和漏极往往存在较大的重叠面积,导致沟道位置的电容较大,造成驱动时存在feed-through电压较大的问题,进而最终影响半导体器件所应用的显示设备的画面显示。

技术实现思路

1、本申请实施例提供一种半导体器件及其制作方法,用以解决相关技术中半导体器件的沟道位置电容较大的问题。

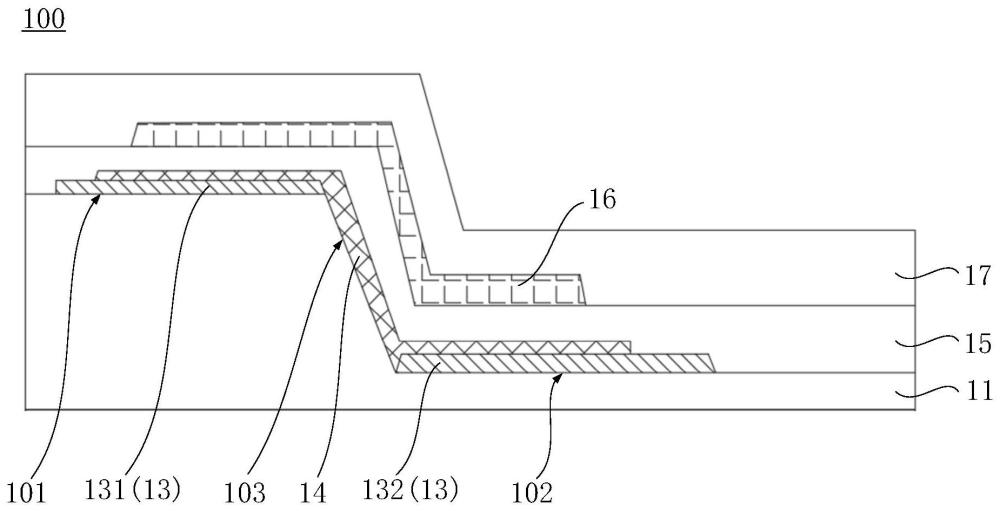

2、一方面,本申请实施例提供一种半导体器件,包括:衬底、源极、漏极、半导体层以及位于所述半导体层上且依次层叠的栅绝缘层和栅极。所述衬底包括位于同侧的第一表面和第二表面,所述第一表面与所述第二表面之间具有形成段差的过渡面;所述源极和所述漏极分别位于所述第一表面和所述第二表面且在所述过渡面断开设置;所述半导体层连续覆盖所述源极和所述漏极。

3、在一些实施例中,所述半导体器件还包括:设置在所述栅极上的层间绝缘层、以及位于所述层间绝缘层上的源极电极和漏极电极,所述层间绝缘层和所述栅绝缘层共同开设有第一过孔和第二过孔,所述源极电极通过所述第一过孔与所述源极电连接,所述漏极电极通过所述第二过孔与所述漏极电连接。

4、在一些实施例中,所述衬底包括层叠设置的基板以及层间介质层,所述第一表面和所述第二表面位于所述层间介质层上。

5、在一些实施例中,所述半导体器件还包括遮光电极,所述半导体层包括位于所述源极和所述漏极之间的沟道,所述遮光电极位于所述基板和所述层间介质层之间且覆盖所述沟道。

6、在一些实施例中,所述半导体器件还包括底栅电极,所述底栅电极与所述栅极同层设置,所述栅绝缘层和所述层间介质层共同开设有第三过孔,所述底栅电极通过所述第三过孔和所述遮光电极电连接。

7、在一些实施例中,所述半导体器件还包括源极电极和转接电极,所述源极电极与所述源极电连接,所述转接电极与所述漏极和所述遮光电极电连接。

8、在一些实施例中,所述源极电极和所述转接电极同层设置。

9、在一些实施例中,所述栅绝缘层开设有第四过孔和第五过孔,所述源极电极通过所述第四过孔与所述源极电连接,所述转接电极通过所述第五过孔与所述漏极电连接;所述栅绝缘层和所述层间介质层共同开设有第六过孔,所述转接电极通过所述第六过孔与所述遮光电极电连接。

10、在一些实施例中,所述半导体器件还包括设置于所述栅极上的层间绝缘层,所述栅绝缘层和所述层间绝缘层共同开设有第七过孔和第八过孔,所述源极电极通过所述第七过孔与所述源极电连接,所述转接电极通过所述第八过孔与所述漏极电连接;所述层间绝缘层、所述栅绝缘层以及所述层间介质层共同开设有第九过孔,所述转接电极通过所述第九过孔与所述遮光电极电连接。

11、在一些实施例中,所述半导体器件还包括:设置在所述栅极上的层间绝缘层、以及设置在所述层间绝缘层上的源极电极、漏极电极、顶栅电极和底栅电极,所述源极电极与所述源极电连接,所述漏极电极与所述漏极电连接,所述顶栅电极与所述栅极电连接,所述底栅电极与所述遮光电极电连接。

12、另一方面,本申请实施例还提供一种半导体器件的制作方法,该制作方法包括:提供衬底,将所述衬底形成第一表面、第二表面以及位于所述第一表面和所述第二表面之间且具有段差的过渡面;在所述衬底上设置源漏电极层,对所述源漏电极层图案化处理,形成位于所述第一表面的源极和位于所述第二表面的漏极,所述源极和所述漏极在所述过渡面断开;在所述源极和所述漏极上设置半导体初始层,对所述半导体初始层图案化处理,形成连续覆盖所述源极和所述漏极的半导体层;在所述半导体层上设置栅绝缘层;以及在所述栅绝缘层上设置栅极金属层,对所述栅极金属层图案化处理,形成栅极。

13、在一些实施例中,所述在所述衬底上设置所述源漏电极层,对所述源漏电极层图案化处理,形成位于所述第一表面的源极和位于所述第二表面的漏极,所述源极和所述漏极在所述过渡面断开,包括:在所述衬底上设置源漏电极层;在所述源漏电极层上设置变质层,所述变质层具有变质部和非变质部,所述变质部覆盖所述第一表面和所述第二表面,所述非变质部覆盖所述第一表面和所述第二表面之间的间隙,所述变质部的刻蚀速率小于所述非变质部的刻蚀速率;刻蚀所述变质层和所述源漏电极层,形成源极、漏极以及覆盖所述源极和所述漏极的剩余变质部;以及去除剩余变质部。

14、在一些实施例中,所述在所述源漏电极层上设置变质层,包括:在所述源漏电极层设置变质材料层;以及对所述变质材料层变质处理,形成所述变质层。

15、在一些实施例中,所述变质层和所述变质材料层为不同材料转化;或者,所述变质层和所述变质材料层为不同材料组分变化;或者,所述变质层和所述变质材料层为相同材料的不同相态转化。

16、在一些实施例中,所述变质材料层的材料为金属,且所述变质层包括金属氧化物。

17、在一些实施例中,所述变质材料层的材料为非晶金属材料,且所述变质层包括结晶金属材料,其中,所述金属材料包括金属氧化物、金属单质以及合金中的一者。

18、对于本申请实施例提供的半导体器件,由于第一表面和第二表面位于不同高度,也即二者之间具有段差,这样使得衬底一侧形成台阶状结构。将半导体层设置在该台阶状结构之上,从而形成垂直沟道,这样一方面可以提升半导体器件的开态的电流,从而利于满足充电率需求;另一方面可以减小半导体器件的尺寸,从而有利于提高对应该半导体器件的像素的光线穿透率,并且有利于实现半导体器件所应用的显示面板实现窄边框。此外,由于源极和漏极不产生交叠,这样可以避免沟道位置存在电容的问题,进而避免该半导体器件所应用的显示面板在驱动时受到feed-through电压影响而出现显示效果不佳的问题。

技术特征:1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,还包括:设置在所述栅极上的层间绝缘层、以及位于所述层间绝缘层上的源极电极和漏极电极,所述层间绝缘层和所述栅绝缘层共同开设有第一过孔和第二过孔,所述源极电极通过所述第一过孔与所述源极电连接,所述漏极电极通过所述第二过孔与所述漏极电连接。

3.根据权利要求1所述的半导体器件,其特征在于,所述衬底包括层叠设置的基板以及层间介质层,所述第一表面和所述第二表面位于所述层间介质层上。

4.根据权利要求3所述的半导体器件,其特征在于,还包括遮光电极,所述半导体层包括位于所述源极和所述漏极之间的沟道,所述遮光电极位于所述基板和所述层间介质层之间且覆盖所述沟道。

5.根据权利要求4所述的半导体器件,其特征在于,还包括底栅电极,所述底栅电极与所述栅极同层设置,所述栅绝缘层和所述层间介质层共同开设有第三过孔,所述底栅电极通过所述第三过孔和所述遮光电极电连接。

6.根据权利要求4所述的半导体器件,其特征在于,还包括源极电极和转接电极,所述源极电极与所述源极电连接,所述转接电极与所述漏极和所述遮光电极电连接。

7.根据权利要求6所述的半导体器件,其特征在于,所述源极电极和所述转接电极同层设置。

8.根据权利要求7所述的半导体器件,其特征在于,所述栅绝缘层开设有第四过孔和第五过孔,所述源极电极通过所述第四过孔与所述源极电连接,所述转接电极通过所述第五过孔与所述漏极电连接;所述栅绝缘层和所述层间介质层共同开设有第六过孔,所述转接电极通过所述第六过孔与所述遮光电极电连接;或者,

9.根据权利要求4所述的半导体器件,其特征在于,还包括:设置在所述栅极上的层间绝缘层、以及设置在所述层间绝缘层上的源极电极、漏极电极、顶栅电极和底栅电极,所述源极电极与所述源极电连接,所述漏极电极与所述漏极电连接,所述顶栅电极与所述栅极电连接,所述底栅电极与所述遮光电极电连接。

10.一种半导体器件的制作方法,其特征在于,包括:

11.根据权利要求10所述的半导体器件的制作方法,其特征在于,所述在所述衬底上设置所述源漏电极层,对所述源漏电极层图案化处理,形成位于所述第一表面的源极和位于所述第二表面的漏极,所述源极和所述漏极在所述过渡面断开,包括:

12.根据权利要求11所述的半导体器件的制作方法,其特征在于,所述在所述源漏电极层上设置变质层,包括:

13.根据权利要求12所述的半导体器件的制作方法,其特征在于,所述变质层和所述变质材料层为不同材料转化;或者,

14.根据权利要求13所述的半导体器件的制作方法,其特征在于,所述变质材料层的材料为金属,且所述变质层包括金属氧化物;或者,

技术总结本申请实施例提供一种半导体器件及其制作方法,涉及显示技术领域,其目的是解决相关技术中半导体器件的半导体层位置电容较大的问题。该半导体器件包括:衬底、源极、漏极、半导体层以及位于所述半导体层上且依次层叠的栅绝缘层和栅极。所述衬底包括位于同侧的第一表面和第二表面,所述第一表面与所述第二表面之间具有形成段差的过渡面;所述源极和所述漏极分别位于所述第一表面和所述第二表面且在所述过渡面断开设置;所述半导体层连续覆盖所述源极和所述漏极。技术研发人员:刘念受保护的技术使用者:深圳市华星光电半导体显示技术有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/177950.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表