碳化硅MOSFET功率器件及其制备方法与流程

- 国知局

- 2024-07-31 18:19:10

本发明涉及功率器件及其制法,具体为碳化硅mosfet功率器件及其制备方法。

背景技术:

1、电力电子系统的发展对半导体器件性能提出了更高的要求,特别是在高温、高频、抗辐照、高压等方面。作为第三代半导体材料的代表,sic具有较大的禁带宽度、较高的电子饱和漂移速度、较强的抗辐照能力、更高的击穿电场和热导率,使其在电力电子设备、宇航系统、高铁牵引设备、军事电子通讯系统等领域有着广泛的应用前景。

2、相比平面栅型sic mosfet器件,沟槽型sic mosfet器件通过在沟槽侧壁形成沟道,既提高了沟道迁移率,又消除了jfet效应,显著减小了器件导通电阻,同时缩小了元胞尺寸,增大了功率密度。

3、但沟槽型sic mosfet器件的栅氧化层质量一直是限制商业化生产的关键因素。sic材料的各个晶面具备不同的氧化速率,这一特点使得沟槽侧壁的栅氧化层厚度是沟槽底部栅氧化层厚度的3~4倍,关断状态下,曲率效应使得沟槽底角处较薄的栅氧化层承受了较高的电场强度,造成破坏性失效。

4、目前可以商业化生产的sic mosfet器件的栅介质材料均为sio2,解决栅介质承受电场过高的方法之一是加厚栅介质,以提高sio2层的抗击穿能力。目前已有的加厚栅介质层的方法包括通过重剂量离子注入将栅介质区域的sic打成非晶态,利用非晶态sic氧化速率更高的特点形成加厚的栅介质,以及在沟槽底部淀积多晶硅,通过热氧化工艺形成加厚的栅介质层。但是,前者会破坏栅介质附近sic外延层的晶体结构,损害器件的电学性能;后者因为难以控制多晶硅的氧化速率,从而无法准确控制栅介质厚度。

技术实现思路

1、发明目的:为了克服现有技术中存在的不足,本发明的目的是提供一种抗击穿能力显著提升、减小失效风险的碳化硅mosfet功率器件,本发明的另一目的是提供一种简单方便、能够高性能批量化生产的碳化硅mosfet功率器件的制备方法。

2、技术方案:本发明所述的一种碳化硅mosfet功率器件,包括漏极电极,漏极电极的表面依次设置衬底、外延层、阱区、源区;外延层、阱区、源区上设置栅沟槽,栅沟槽包括第一沟槽和第二沟槽,第一沟槽的直径大于第二沟槽的直径,栅沟槽内设置同轴的介质层和栅极电极;介质层包括设在第一沟槽内的第一介质层、设在第二沟槽内的第二介质层,第一介质层的厚度大于第二介质层的厚度;栅极电极、介质层、源区的表面设置隔离介质层,源区的表面还设置源极电极。

3、进一步地,第一沟槽的直径大于第二沟槽的直径0.1 ~0.5µm,这一设计可以利用sic材料各个晶面具备不同氧化速率这一特点,在沟槽底角处形成了加厚的第一介质层。第一沟槽的深宽比≤2:1,侧壁角度≥80度。第二沟槽的深宽比≥1.5:1,侧壁角度≥80度。

4、进一步地,相邻第一沟槽之间的距离不小于1µm。第一沟槽的宽度为0.7 ~2µm,深度为0.2~1.0µm;第二沟槽的宽度为0.5 ~1.8µm,深度为0.5~2.0µm。

5、进一步地,介质层还包括第三介质层,第三介质层设置栅沟槽底部中央,厚度为40~150nm。介质层由二氧化硅材料制成。

6、进一步地,衬底由3c-sic、4h-sic、6h-sic或15r-sic材料制成,衬底的厚度为10 ~1000µm,掺杂浓度1e18cm-3~5e19cm-3,掺杂元素为n、p等元素。

7、进一步地,外延层由是3c-sic、4h-sic、6h-sic或15r-sic材料制成,外延层的厚度为8 ~200µm,掺杂浓度1e14cm-3~1e16cm-3。

8、进一步地,衬底、外延层、阱区、源区均为n型或p型。

9、进一步地,阱区深度为0.5 ~1.0µm,阱区的掺杂分布可以是均匀分布或非均匀分布,平均掺杂浓度为5e16cm-3~5e17cm-3。

10、进一步地,隔离介质层由氮化硅材料制成,厚度为0.5~10µm,以形成源极窗口。通过此源极窗口蒸发金属,金属选用ti/al合金,再于300℃~1100℃下退火,以形成源极欧姆接触。在衬底底层形成漏极欧姆接触,在源极欧姆接触表面形成源极电极,在漏极欧姆接触层表面形成漏极电极。

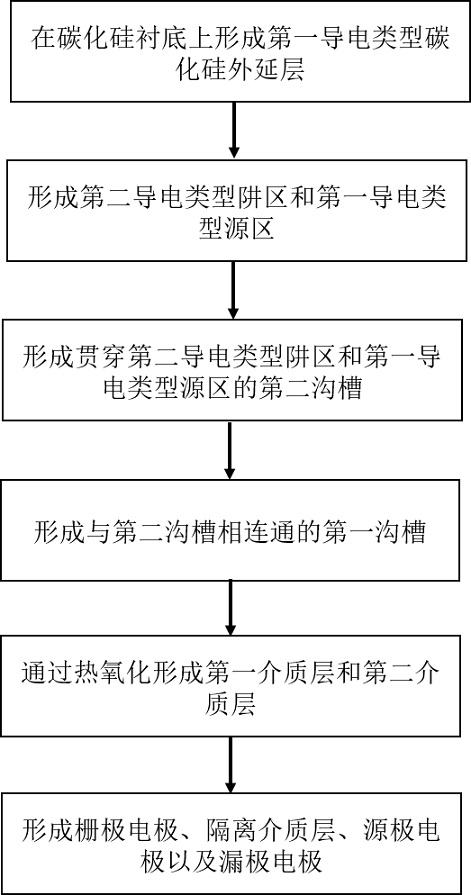

11、本发明所述的一种用于碳化硅mosfet功率器件的制备方法,包括以下步骤:

12、步骤一,在衬底上依次生长外延层、阱区、源区;

13、步骤二,对外延层进行电感耦合等离子体刻蚀,去除部分外延层,形成贯穿阱区、源区的凹槽;

14、步骤三,对凹槽的底部进行各向同性刻蚀, 1400℃~1800℃高温退火钝化,形成栅沟槽;

15、步骤四,在栅沟槽的两个底角处形成第一介质层,在栅沟槽的侧壁处形成第二介质层,900℃~1300℃高温退火;

16、步骤五,在介质层内形成栅极电极,在栅极电极、源区表面形成隔离介质层、源极电极,衬底上形成漏极电极。

17、为了进一步提升栅介质层的抗击穿能力,步骤四替换为:在栅沟槽的底部中央形成替代层,在栅沟槽的两个底角处形成第一介质层,在栅沟槽的侧壁处形成第二介质层,900℃~1300℃高温退火,替代层热氧化形成第三介质层。

18、进一步地,步骤一中,阱区、源区采用离子注入法形成,具体步骤包括:在外延层表面制备图形化掩膜层,随后注入第一导电类型或第二导电类型杂质,去除掩膜后于1400℃~2200℃温度下退火2min~30min。

19、进一步地,步骤三中,高温退火钝化所用气体为sih4、h2、ar中的一种或多种。

20、进一步地,步骤四中,高温退火的气体是no、n2o、h2、nh3中的一种或多种。

21、进一步地,步骤五中,栅极电极为多晶硅、非晶硅或无定型硅,掺杂杂质为al、n、p或b。形成栅极电极的方法是原子层沉积、化学气相沉积、等离子增强化学气相沉积或溅射。

22、工作原理:关断状态下,加厚的第一介质层的抗击穿能力得到了极大加强,避免了栅介质提前击穿、使得器件击穿电压达不到预期的风险,有效提升了器件可靠性。

23、有益效果:本发明和现有技术相比,具有如下显著性特点:

24、1、不破坏sic外延层的晶体结构,显著提高了器件的电学性能,能够准确控制栅介质厚度;

25、2、通过相连通的第一沟槽、第二沟槽组成栅沟槽,通过热氧化形成栅沟槽底角处的第一介质层与第二沟槽侧壁处的第二介质层,利用sic材料各个晶面具备不同氧化速率这一特点,在沟槽底角处形成了加厚的第一介质层,显著提升了底角介质层的抗击穿能力,极大程度地减小了器件失效风险;

26、3、制备方法与现有sic槽栅型mosfet功率器件制造工艺兼容,仅仅增加了一步各向同性刻蚀工艺,相比已有的改进结构,明显降低了工艺复杂性,可用于实现高性能的槽栅型碳化硅mosfet器件批量生产。

技术特征:1.一种碳化硅mosfet功率器件,其特征在于:包括漏极电极(1),所述漏极电极(1)的表面依次设置衬底(2)、外延层(3)、阱区(6)、源区(7);所述外延层(3)、阱区(6)、源区(7)上设置栅沟槽(4),所述栅沟槽(4)包括第一沟槽(401)、第二沟槽(402),所述第一沟槽(401)的直径大于第二沟槽(402)的直径,所述栅沟槽(4)内设置同轴的介质层(5)和栅极电极(8);所述介质层(5)包括设在第一沟槽(401)内的第一介质层(501)、设在第二沟槽(402)内的第二介质层(502),所述第一介质层(501)的厚度大于第二介质层(502)的厚度;所述栅极电极(8)、介质层(5)、源区(7)的表面设置隔离介质层(10),所述源区(7)的表面还设置源极电极(9)。

2. 根据权利要求1所述的一种碳化硅mosfet功率器件,其特征在于:所述第一沟槽(401)的直径大于第二沟槽(402)的直径0.1 ~0.5µm。

3.根据权利要求2所述的一种碳化硅mosfet功率器件,其特征在于:所述第一沟槽(401)的深宽比≤2:1,侧壁角度≥80度。

4.根据权利要求2所述的一种碳化硅mosfet功率器件,其特征在于:所述第二沟槽(402)的深宽比≥1.5:1,侧壁角度≥80度。

5.根据权利要求1所述的一种碳化硅mosfet功率器件,其特征在于:所述介质层(5)还包括第三介质层(503),所述第三介质层(503)设置栅沟槽(4)底部中央,厚度为40~150nm。

6.根据权利要求1所述的一种碳化硅mosfet功率器件,其特征在于:所述介质层(5)由二氧化硅材料制成。

7. 根据权利要求1所述的一种碳化硅mosfet功率器件,其特征在于:所述衬底(2)由3c-sic、4h-sic、6h-sic或15r-sic材料制成,所述衬底(2)的厚度为10 ~1000µm,掺杂浓度1e18cm-3~5e19cm-3。

8. 根据权利要求1所述的一种碳化硅mosfet功率器件,其特征在于:所述外延层(3)由是3c-sic、4h-sic、6h-sic或15r-sic材料制成,所述外延层(3)的厚度为8 ~200µm,掺杂浓度1e14cm-3~1e16cm-3。

9.一种用于权利要求1或5所述的碳化硅mosfet功率器件的制备方法,其特征在于,包括以下步骤:

10.根据权利要求9所述的碳化硅mosfet功率器件的制备方法,其特征在于:所述步骤四替换为:在栅沟槽(4)的底部中央形成替代层(11),在栅沟槽(4)的两个底角处形成第一介质层(501),在栅沟槽(4)的侧壁处形成第二介质层(502),900℃~1300℃高温退火,替代层(11)热氧化形成第三介质层(503)。

技术总结本发明公开了一种碳化硅MOSFET功率器件及其制备方法,碳化硅MOSFET功率器件包括漏极电极,漏极电极的表面依次设置衬底、外延层阱区、源区;外延层、阱区、源区上设置栅沟槽,栅沟槽包括第一沟槽和第二沟槽,栅沟槽内设置同轴的介质层和栅极电极;介质层包括第一介质层、第二介质层,第一介质层的厚度大于第二介质层的厚度;栅极电极、介质层、源区的表面设置隔离介质层,第一导电类型源区的表面还设置源极电极。本发明不破坏SiC外延层的晶体结构,显著提高器件的电学性能,能够准确控制栅介质厚度;利用SiC材料各个晶面氧化速率不同,在沟槽底角处形成加厚的第一介质层,显著提升抗击穿能力,极大减小了失效风险。技术研发人员:王德平,张跃,赵永强,赵慧超,张腾,杨勇受保护的技术使用者:中国电子科技集团公司第五十五研究所技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178750.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表