半导体器件及其制造方法与流程

- 国知局

- 2024-07-31 18:25:36

本发明涉及半导体,特别涉及一种半导体器件及其制造方法。

背景技术:

1、在半导体器件的制造过程中,半导体器件一般要经历很多使用等离子的工艺,如等离子蚀刻或活性离子蚀刻(rie)、薄膜沉积、灰化、和/或其他包括等离子的工艺。例如,可通过在覆盖导电层(blanket conductive layer)中蚀刻图案(如,线路)形成互连。用于进行这些工艺的能量可导致包括互连线路和栅电极的集成电路层变得带电。参图2所示,图2为保护二极管示意图,其中,10-晶圆衬底;20-天线;30-栅极氧化层;40-栅极结构,这些导电线路可作为天线,由于导电线路可被连接到器件的栅极,天线20收集的电荷传输到栅极结构40,产生的电荷可导致对器件的栅极电介质(如,栅极氧化层30)的损害,即会产生等离子体工艺致损伤(pid)。

2、等离子体工艺致损伤(pid)是晶体管可靠性风险评估的项目之一,对晶体管制造的良率和产品寿命有重要影响。特别是对含先进的阱、深沟槽等引入隔离面积的半导体器件尤为重要。在半导体制造时,新产品导入时会对数据进行天线设计规则检查,天线比(ar)通常指金属面积与mos栅氧化层面积比值。即,ar=(s_met)/(s_mos+c1·s_diff),其中,s_met为焊盘的面积;s_mos为nmos栅氧化层的面积与pmos栅氧化层的面积之和;c1为有效系数,为一常数;s_diff为扩散区的面积,即二极管的面积。天线设计规则为天线比规定了最大许可值。通常每层与多晶硅相连的金属、每个接触孔都具有ar值,其中mos栅氧面积是nmos和pmos栅氧面积总和,并不区分晶体管类型。图1为二极管的面积与ar值的函数关系,从图1可以看出,在实际设计中,部分区域的ar会超出上限,此时需要加入保护区,通常为扩散区。

3、为了解决上述的技术问题,在图2中的半导体器件加入二极管作为保护区,并且二极管的一端与栅极结构40连接,另一端与衬底10连接,由于衬底10接地,当进行等离子体加工时,电荷可通过二极管流入到衬底10中,从而减低等离子的损害。但是,对于扩散区的类型和位置分布并无明确规定,且pid对不同类型的mos影响不同,特别是反相器中,具有非对称性,无法保证具体器件无pid风险。

4、需要说明的是,公开于该发明背景技术部分的信息仅仅旨在加深对本发明一般背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制造方法,以解决在满足天线设计规则的条件下,对于扩散区的类型和位置分布并无明确规定,因此无法保证具体器件无pid风险的问题。

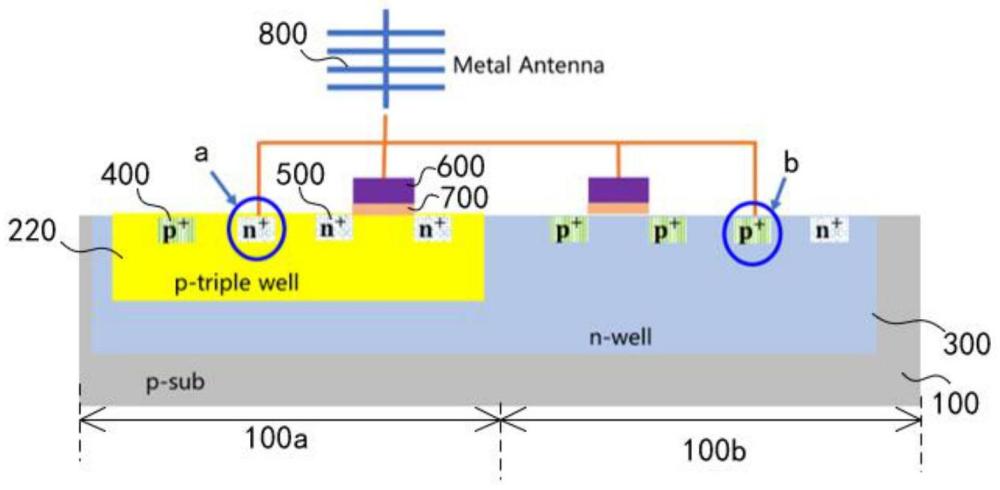

2、为解决上述技术问题,本发明提供一种半导体器件,包括:

3、p型衬底,接地,所述p型衬底形成有待保护器件,以及形成于所述p型衬底的p阱和n阱,所述待保护器件包括形成于所述p阱和/或n阱的栅氧化层,所述栅氧化层的表面形成有栅极,所述栅极的两侧具有漏极和源极;

4、保护区,形成于具有p阱和n阱的p型衬底上,所述保护区连接至所述栅极,且所述待保护器件和保护区位于相同阱内。

5、优选地,所述保护区为二极管。

6、优选地,所述待保护器件包括第一器件和第二器件,所述第一器件和所述第二器件的至少一个栅极连接到所述保护区。

7、优选地,所述第一器件为nmos器件,所述第二器件为pmos器件,所述nmos器件和pmos器件的栅极与所述保护区连接。

8、优选地,所述nmos器件还包括形成于p阱内的一个高浓度p型掺杂区和多个高浓度n型掺杂区,所述高浓度n型掺杂区的表面形成有栅氧化层,所述栅极一侧的高浓度n型掺杂区形成漏极,所述栅极另一侧的高浓度n型掺杂区形成源极;

9、所述pmos器件包括形成于n阱内的多个高浓度p型掺杂区和一个高浓度n型掺杂区,所述高浓度p型掺杂区的表面形成有栅氧化层,所述栅极一侧的高浓度p型掺杂区形成漏极,所述栅极另一侧的高浓度p型掺杂区形成源极。

10、优选地,所述nmos器件的保护区形成于所述nmos器件的高浓度n型掺杂区,所述pmos器件的保护区形成于所述pmos器件的高浓度p型掺杂区。

11、优选地,所述待保护器件的p阱包括第一p阱和第二p阱,所述第二p阱形成于所述n阱内;

12、所述第一p阱具有一个高浓度p型掺杂区和多个高浓度n型掺杂区,所述高浓度n型掺杂区的表面形成有栅氧化层,所述栅极一侧的高浓度n型掺杂区为源极,所述栅极另一侧的高浓度n型掺杂区为漏极;

13、所述n阱和第二p阱分别具有一个高浓度p型掺杂区和一个高浓度n型掺杂区。

14、基于相同的发明思想,本发明还提供了一种半导体器件制造方法,包括:

15、提供一p型衬底,所述p型衬底形成有待保护器件,以及形成于所述p型衬底的p阱和n阱,所述待保护器件包括形成于所述p阱和/或n阱的栅氧化层,所述栅氧化层的表面形成有栅极,所述栅极的两侧具有漏极和源极;

16、在具有p阱和n阱的p型衬底上制作保护区,所述保护区连接至所述栅极,且所述待保护器件和保护区位于相同阱内。

17、优选地,所述保护区为二极管。

18、优选地,所述待保护器件包括nmos器件和pmos器件,所述nmos器件和pmos器件分别与所述二极管位于相同阱内。

19、与现有技术相比,本发明的半导体器件具有如下优点:

20、本发明通过设置p型衬底,接地,所述p型衬底形成有待保护器件,以及形成于所述p型衬底的p阱和n阱,所述待保护器件包括形成于所述p阱和/或n阱的栅氧化层,所述栅氧化层的表面形成有栅极,所述栅极的两侧具有漏极和源极;保护区,形成于具有p阱和n阱的p型衬底上,所述保护区连接至所述栅极,且所述待保护器件和保护区位于相同阱内。由此,本发明提供的半导体器件,由于将把保护区与栅极设置在相同阱内,从而能够确定最佳保护区的位置。不仅能够满足天线设计规则的条件,在保证全局pid可靠性的前提下,降低了芯片的面积。避免对半导体器件的性能造成影响。

21、本发明提供的半导体器件制造方法与本发明提供的半导体器件属于同一发明构思,因此,本发明提供的半导体器件制造方法至少具有本发明提供的半导体器件的所有优点,能够满足天线设计规则的条件,保证全局pid可靠性,同时,也降低了芯片的面积。避免对半导体器件的性能造成影响。

技术特征:1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述保护区为二极管。

3.根据权利要求1所述的半导体器件,其特征在于,所述待保护器件包括第一器件和第二器件,所述第一器件和所述第二器件的至少一个栅极连接到所述保护区。

4.根据权利要求3所述的半导体器件,其特征在于,所述第一器件为nmos器件,所述第二器件为pmos器件,所述nmos器件和pmos器件的栅极与所述保护区连接。

5.根据权利要求4所述的半导体器件,其特征在于,所述nmos器件还包括形成于p阱内的一个高浓度p型掺杂区和多个高浓度n型掺杂区,所述高浓度n型掺杂区的表面形成有栅氧化层,所述栅极一侧的高浓度n型掺杂区形成漏极,所述栅极另一侧的高浓度n型掺杂区形成源极;

6.根据权利要求5所述的半导体器件,其特征在于,所述nmos器件的保护区形成于所述nmos器件的高浓度n型掺杂区,所述pmos器件的保护区形成于所述pmos器件的高浓度p型掺杂区。

7.根据权利要求1所述的半导体器件,其特征在于,所述待保护器件的p阱包括第一p阱和第二p阱,所述第二p阱形成于所述n阱内;

8.一种半导体器件制造方法,其特征在于,包括:

9.根据权利要求8所述的半导体器件制造方法,其特征在于,所述保护区为二极管。

10.根据权利要求9所述的半导体器件制造方法,所述待保护器件包括nmos器件和pmos器件,所述nmos器件和pmos器件分别与所述二极管位于相同阱内。

技术总结本发明提供了一种半导体器件及其制造方法,属于半导体领域。该半导体器件包括P型衬底,接地,所述P型衬底形成有待保护器件,所述待保护器件包括形成于所述P型衬底的P阱和N阱,以及形成于所述P阱和/或N阱的栅氧化层,所述栅氧化层的表面形成有栅极,所述栅极的两侧具有漏极和源极;保护区,形成于具有P阱和N阱的P型衬底上,所述保护区连接至所述栅极,且所述待保护器件和保护区位于相同阱内。本发明通过将把保护区与栅极设置在相同阱内,从而能够确定最佳保护区的位置。不仅能够满足天线设计规则的条件,在保证全局PID可靠性的前提下,降低了芯片的面积。避免对半导体器件的性能造成影响。技术研发人员:蔡亚果,刘哲郡,陆尉,曹亚民受保护的技术使用者:上海华力微电子有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/179115.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表