半导体器件的制作方法

- 国知局

- 2024-07-31 18:32:00

本申请实施例涉及半导体,尤其涉及一种半导体器件。

背景技术:

1、自集成电路器件的封装从单个组件的开发,进入到多个组件的集成后,随着产品效能的提升以及对轻薄和低耗需求的带动下,迈向封装整合的新阶段。在此发展方向的引导下,形成了电子产业上相关的两大新主流:系统单芯片soc(system on chip)与系统化封装sip(systemin packag)。

2、由于摩尔定律的优势越来越难以实现,成本也越来越高,全球半导体产业界正致力于寻找后摩尔定律时代的突破口。美国半导体行业协会(sia)于2015年宣布停止更新itrs(国际半导体技术路线图),接力棒交给了异构集成路线图(hir,于2019年10月发布),其焦点集中在系统级封装(sip)以及未来10年至15年的发展方向:3d、3d互连和晶圆级封装。

3、sip是从封装的立场出发,对不同芯片进行并排或叠加的封装方式,将多个具有不同功能的有源电子元件与可选无源器件,以及诸如mems或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件。

4、sip封装技术采取多种裸芯片或模块进行排列组装,若就排列方式区分可大体分为平面式2d封装和3d封装的结构。采用堆叠的3d技术可以增加使用晶圆或模块的数量,从而在垂直方向上增加可放置晶圆的层数,进一步增强sip技术的功能整合能力;而其内部接合技术可以是单纯的线键合(wire bonding),也可使用倒装键合(flip chip),也可二者混用。

5、主流的sip封装形式还是bga,采用引线键合或者凸点键合的方式与设计的电路板载板进行互连,从而形成一个完整的微系统。目前最先进的3d sip采用interposer(硅基中介层)将裸晶通过tsv(硅穿孔工艺)与基板结合。与常见芯片封装的引线键合或凸点键合技术不同,tsv能够使芯片在三维方向堆叠的密度更大、外形尺寸更小,并且大大改善芯片速度和降低功耗,成为3d芯片新的发展方向。但是tsv工艺难度大,设备精密且复杂,价格昂贵。目前主流的sip封装(采用引线键合或者凸点键合的方式)都是在封装基板上进行加工制作,一方面需要在封装基板上预留芯片贴合的位置,另一方面为了将高密度芯片的i/o接口扇出,对封装基板的制作要求而且受限封装基板的工艺制作限制,一般只能设计的线宽/线距在30um/30um。

技术实现思路

1、本实用新型旨在至少解决现有技术或相关技术中存在的技术问题之一。

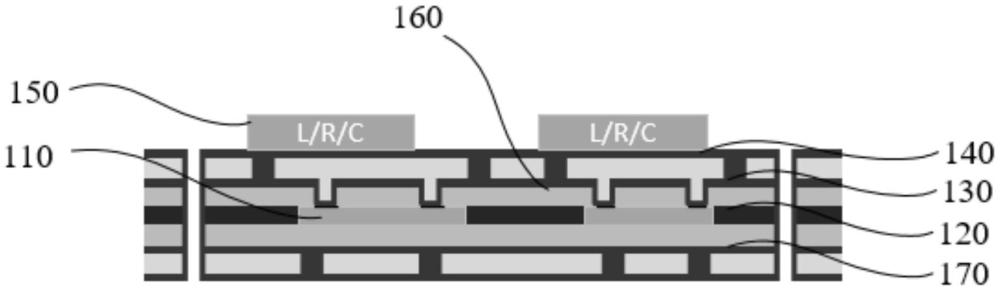

2、有鉴于此,本申请实施例提出了一种半导体器件,包括:

3、芯片;

4、介质薄膜,所述芯片嵌入在所述介质薄膜内;

5、rdl线路层,所述rdl线路层连接于所述芯片;

6、外层电路,所述外层电路连接于所述rdl线路层。

7、在一种可行的实施方式中,半导体器件还包括:

8、无源器件,所述无源器件连接于所述外层电路。

9、在一种可行的实施方式中,半导体器件还包括:

10、第一光刻胶层,所述第一光刻胶层布置在所述介质薄膜和所述芯片与所述rdl线路层之间。

11、在一种可行的实施方式中,半导体器件还包括:

12、背面线路层,所述背面线路层布置在所述芯片和所述介质薄膜背离于所述rdl线路层的一侧。

13、在一种可行的实施方式中,所述背面线路层包括:

14、背面线路和第二光刻胶层,所述第二光刻胶层布置在所述介质薄膜与所述背面线路之间。

15、在一种可行的实施方式中,所述介质薄膜由环氧系材料制成。

16、在一种可行的实施方式中,所述介质薄膜由半固化材料制成。

17、在一种可行的实施方式中,所述芯片上形成有连接盘,所述连接盘连接于所述rdl线路层。

18、在一种可行的实施方式中,所述芯片为裸芯片,所述裸芯片的数量为两个或两个以上。

19、在一种可行的实施方式中,所述外层电路包括多层叠置的电路。

20、相比现有技术,本实用新型至少包括以下有益效果:

21、本申请实施例提供的半导体器件包括了芯片、介质薄膜、rdl线路层和外层电路,芯片嵌入到介质薄膜之内,然后在介质薄膜上进行rdl线路层制作,使芯片pad与rdl线路层形成互连,再通过增层的方式来制作其余所需的外层电路,完成整电路制作的同时,芯片也完成了封装。基于此将介质薄膜作为封装基板,采用嵌入的方式固定芯片,这样可以大幅节省封装基板表面空间,从而使封装后的半导体器件的尺寸大幅降低。通过本申请实施例提供的半导体器件在高密度芯片的i/o接口扇出方面,可以采用半导体封装技术做到线宽/线距在10um/10um的设计,这样可以进一步节省封装基板表面空间,从而使封装后的半导体器件尺寸大幅降低。

技术特征:1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,还包括:

3.根据权利要求1所述的半导体器件,其特征在于,还包括:

4.根据权利要求1所述的半导体器件,其特征在于,还包括:

5.根据权利要求4所述的半导体器件,其特征在于,所述背面线路层包括:

6.根据权利要求1至5中任一项所述的半导体器件,其特征在于,

7.根据权利要求1至5中任一项所述的半导体器件,其特征在于,

8.根据权利要求1至5中任一项所述的半导体器件,其特征在于,

9.根据权利要求1至5中任一项所述的半导体器件,其特征在于,

10.根据权利要求1至5中任一项所述的半导体器件,其特征在于,

技术总结本申请实施例公开了一种半导体器件,半导体器件包括了芯片、介质薄膜、RDL线路层和外层电路,芯片嵌入到介质薄膜之内,然后在介质薄膜上进行RDL线路层制作,使芯片PAD与RDL线路层形成互连,再通过增层的方式来制作其余所需的外层电路,完成整电路制作的同时,芯片也完成了封装,基于此将介质薄膜作为封装基板,采用嵌入的方式固定芯片。这样可以大幅节省封装基板表面空间,从而使封装后的半导体器件的尺寸大幅降低,使得本申请实施例提供的半导体器件在高密度芯片的I/O接口扇出方面,可以采用半导体封装技术做到线宽/线距在10um/10um的设计,这样可以进一步节省封装基板表面空间,从而使封装后的半导体器件尺寸大幅降低。技术研发人员:冯雪,王波,魏瑀,滕乙超,阳俊航,刘洋洋受保护的技术使用者:浙江清华柔性电子技术研究院技术研发日:20231221技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/179600.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表