半导体器件及其制备方法、电子设备与流程

- 国知局

- 2024-07-31 18:26:56

本技术涉及半导体,尤其涉及一种半导体器件及其制备方法、电子设备。

背景技术:

1、在半导体器件的制备过程中,阱区的离子注入是半导体器件制备过程中尤为重要的工艺技术。由于碳化硅材料的原子间作用力较强且原子扩散系数低,通常利用高能离子注入工艺来形成有源层内的阱区。

2、然而,高能、高剂量的离子注入会对离子注入区产生晶格损伤,造成离子注入区内的晶格缺陷,导致半导体器件内反型沟道的电子迁移率下降,增加器件的导通电阻。同时,在离子注入区靠近反型沟道位置处,由于曲率半径较小导致该位置处局部电场强度较大,抑制了半导体器件击穿电压的提升。

技术实现思路

1、本技术实施例提供一种半导体器件及其制备方法、电子设备,用于提升半导体器件的导通特性和击穿特性。

2、为达到上述目的,本技术采用如下技术方案:

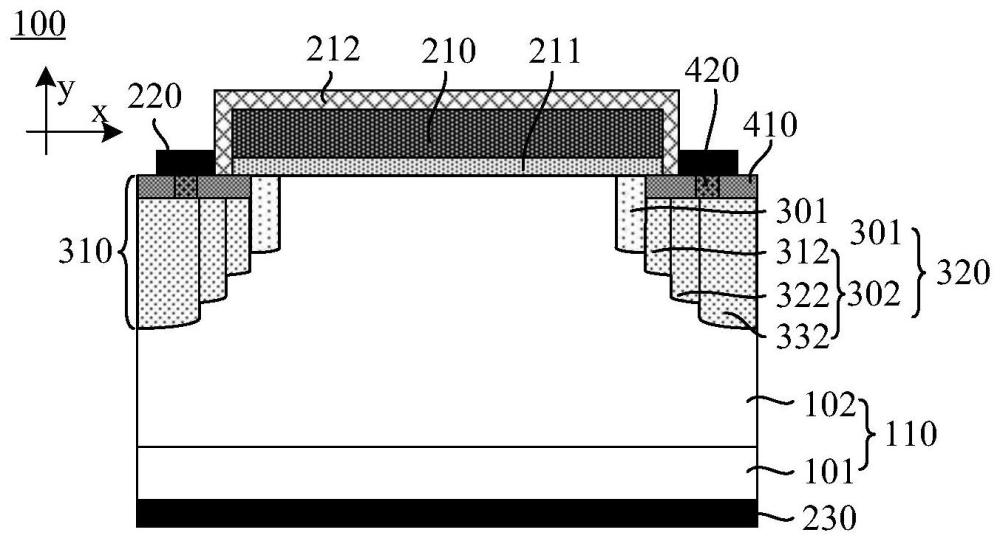

3、本技术实施例的第一方面,提供一种半导体器件,包括半导体衬底、位于半导体衬底的第一表面内的第一阱区和第二阱区以及位于半导体衬底的第一表面上的栅极。其中,第一阱区和第二阱区之间具有间隔,栅极位于第一阱区和第二阱区之间。第一阱区和第二阱区中的至少一个阱区包括沿第一方向依次设置的第一阱段和第二阱段,第一阱段设置于第二阱段靠近栅极一侧,且第一阱段的掺杂浓度小于第二阱段的掺杂浓度。第一方向与半导体衬底表面平行。

4、本技术实施例提供的半导体器件,第一阱段所在区域作为半导体器件的反型沟道。第一阱段的掺杂浓度小于第二阱段的掺杂浓度,相比于现有半导体器件中反型沟道的掺杂浓度减小,缓解了反型沟道中晶格损伤程度,降低了反型沟道中的离子注入损伤,提升反型沟道内的电子迁移率,进而提升半导体器件的导通特性。

5、在一种可能的实现方式中,第二阱段在半导体衬底内的深度大于第一阱段在半导体衬底内的深度。这样一来,能够使得第一阱区和第二阱区中至少一个阱区在靠近栅极的拐角处呈阶梯状,增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径,能够降低第一阱区和第二阱区中至少一个阱区拐角处位置的电场强度,进而提升半导体器件的击穿电压,有助于提升半导体器件的击穿特性。

6、在一种可能的实现方式中,第二阱段包括多个子阱段;多个子阱段沿第一方向依次排布;沿第一阱段指向第二阱段的方向,多个子阱段在半导体衬底内的深度依次增加。这样一来,能够进一步增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径,进一步降低第一阱区和第二阱区中至少一个阱区拐角处位置的电场强度。

7、在一种可能的实现方式中,沿半导体衬底的厚度方向,相邻的两个子阱段的尺寸之差大于100nm。这样一来。能够进一步增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径,进一步降低第一阱区和第二阱区中至少一个阱区拐角处位置的电场强度。

8、在一种可能的实现方式中,沿第一阱段指向第二阱段的方向,多个子阱段的掺杂浓度依次增加。这样一来,能够进一步增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径。

9、在一种可能的实现方式中,多个子阱段的掺杂浓度相同。这样一来,便于形成,节约成本。

10、在一种可能的实现方式中,第二阱段包括沿第一方向依次设置的第一子阱段、第二子阱段以及第三子阱段;第一子阱段位于第二子阱段靠近第一阱段一侧,沿半导体衬底厚度方向,第一子阱段的尺寸小于或者等于第二子阱段的尺寸。这样一来,能够进一步增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径。

11、在一种可能的实现方式中,第二阱段包括沿第一方向依次设置的第一子阱段、第二子阱段以及第三子阱段;第一子阱段位于第二子阱段靠近第一阱段一侧,沿半导体衬底厚度方向,第二子阱段的尺寸小于或者等于第三子阱段的尺寸。这样一来,能够进一步增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径。

12、在一种可能的实现方式中,第一阱区和第二阱区均包括第一阱段和第二阱段。这样一来,能够进一步提升反型沟道内的电子迁移率,进一步提升半导体器件的导通特性。

13、在一种可能的实现方式中,第一阱区和第二阱区的掺杂类型相同。这样一来,易于制备,工艺简单。

14、在一种可能的实现方式中,沿半导体衬底的厚度方向,第二阱段的尺寸与第一阱段的尺寸之差大于100nm。这样一来,能够进一步增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径。

15、在一种可能的实现方式中,第一阱段的掺杂浓度为4×107cm-3~6×107cm-3;第二阱段的掺杂浓度为8×107cm-3~1.3×108cm-3。这样一来,能够缓解反型沟道的晶格损伤程度。

16、在一种可能的实现方式中,半导体器件还包括第一半导体层和第二半导体层;第一半导体层和第二半导体层位于第一阱区和第二阱区内,且第一半导体层包裹第二半导体层的侧面。这样一来,能够形成源极或漏极。这样一来,能够形成晶体管。

17、在一种可能的实现方式中,半导体器件还包括源极和漏极;源极位于第一阱区和第二阱区远离半导体衬底一侧;漏极位于与半导体衬底的第一表面相对的第二表面一侧。

18、本技术实施例的第二方面,提供一种半导体器件,包括:半导体衬底、位于半导体衬底的第一表面内的第一阱区和第二阱区以及位于半导体衬底的第一表面上的栅极。其中,第一阱区和第二阱区之间具有间隔,栅极位于第一阱区和第二阱区之间。第一阱区和第二阱区中的至少一个阱区包括沿第一方向依次设置的第一阱段和第二阱段,第一阱段设置于第二阱段靠近栅极一侧,且第二阱段在半导体衬底内的深度大于第一阱段在半导体衬底内的深度。第一方向与半导体衬底表面平行。

19、本技术实施例提供的半导体器件,第二阱段在半导体衬底内的深度大于第一阱段在半导体衬底内的深度时,使得第一阱区和第二阱区中至少一个阱区在靠近栅极的拐角处呈阶梯状,增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径,能够降低第一阱区和第二阱区中至少一个阱区拐角处位置的电场强度,进而提升半导体器件的击穿电压,有助于提升半导体器件的击穿特性。

20、同时,当半导体器件导通时,由于半导体器件的击穿电压得到提升,因此第一阱区和第二阱区中至少一个阱区下方区域的电流增加,进而降低半导体器件的导通电阻,有助于提升半导体器件的导通特性。

21、在一种可能的实现方式中,第一阱段的掺杂浓度等于第二阱段的掺杂浓度。这样一来,第一阱段所在区域将作为半导体器件的反型沟道,能够缓解反型沟道中晶格损伤程度,降低了反型沟道中的离子注入损伤,提升反型沟道内的电子迁移率,进而提升半导体器件的导通特性。

22、本技术实施例的第三方面,提供一种半导体器件的制备方法,包括:提供半导体衬底;在半导体衬底的第一表面进行第一离子注入,形成第一阱区和第二阱区;第一阱区和第二阱区具有间隔;对第一阱区和第二阱区中的至少一个阱区进行至少一次第二离子注入,形成第二阱段;沿第一方向,第二阱段的边缘不超过第一离子注入的区域边缘,第一方向与半导体衬底表面平行;第二阱段的掺杂浓度大于第一离子注入的区域的掺杂浓度;在半导体衬底的第一表面上形成栅极;栅极位于第一阱区和第二阱区之间。

23、本技术实施例提供的半导体器件的制备方法,通过对半导体衬底进行至少两次离子注入,第一离子注入和第二离子注入,且形成的第二阱段的掺杂浓度大于第一阱区或者第二阱区的掺杂浓度,这样一来,使得本技术实施例形成的半导体器件反型沟道中的掺杂浓度,相比于现有一次高能注入形成的半导体器件反型沟道的掺杂浓度减小,缓解了反型沟道中晶格损伤程度,降低了由于离子注入带来反型沟道中的离子注入损伤程度,进而提升反型沟道内的电子迁移率,有利于提升半导体器件的导通特性。

24、在一种可能的实现方式中,第二离子注入在半导体衬底内的深度大于第一离子注入在半导体衬底内的深度。这样一来,能够使得第一阱区和第二阱区中至少一个阱区在靠近栅极的拐角处呈阶梯状,增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径,能够降低第一阱区和第二阱区中至少一个阱区拐角处位置的电场强度,进而提升半导体器件的击穿电压,有助于提升半导体器件的击穿特性。

25、在一种可能的实现方式中,对第一阱区或者第二阱区中的至少一个阱区进行多次第二离子注入,多次第二离子注入在半导体衬底内的深度依次增大。这样一来,能够进一步增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径,进一步降低第一阱区和第二阱区中至少一个阱区拐角处位置的电场强度。

26、在一种可能的实现方式中,对第一阱区和第二阱区中均进行至少一次第二离子注入。这样一来,能够进一步提升反型沟道内的电子迁移率,进一步提升半导体器件的导通特性。

27、在一种可能的实现方式中,在半导体衬底的第一表面进行第一离子注入之前,制备方法还包括:在半导体衬底的第一表面上形成第一掩膜层;在半导体衬底的第一表面进行第一离子注入之后,制备方法还包括:在半导体衬底的第一表面上形成第二掩膜层,第二掩膜层包裹第一掩膜层的侧面。这样一来,能够实现对多个子阱段的位置实现自对准,减少了第一阱区和第二阱区内多个子阱段位置上的偏差,能够对工艺实现更好的控制。

28、在一种可能的实现方式中,在半导体衬底的第一表面上形成栅极之前,制备方法还包括:在第一阱区和第二阱区内形成第一半导体层;在第一半导体层内形成第二半导体层;第一半导体层包裹第二半导体层的外围。这样一来,能够形成源极和漏极。

29、在一种可能的实现方式中,形成栅极之后,制备方法还包括:在第一阱区和第二阱区远离半导体衬底一侧形成源极;在与半导体衬底的第一表面相对的第二表面上形成漏极。这样一来,能够形成晶体管。

30、本技术实施例的第四方面,提供一种半导体器件的制备方法,包括:提供半导体衬底;在半导体衬底的第一表面进行第一离子注入,形成第一阱区和第二阱区;第一阱区和第二阱区具有间隔;对第一阱区和第二阱区中的至少一个阱区进行至少一次第二离子注入,形成第二阱段;第二离子注入的深度大于第一离子注入的深度;沿第一方向,第二离子注入的区域边缘不超过第一离子注入的区域边缘,第一方向与半导体衬底表面平行;在半导体衬底的第一表面上形成栅极;栅极位于第一阱区和第二阱区之间。

31、本技术实施例提供的半导体器件的制备方法,通过对半导体衬底进行至少两次离子注入,第一离子注入和第二离子注入,且第二离子注入的深度大于第一离子注入的深度。这样一来,使形成的半导体器件中,第一阱区和第二阱区中至少一个阱区在靠近栅极的拐角处呈阶梯状,增大第一阱区和第二阱区中至少一个阱区拐角处的曲率半径,能够降低第一阱区和第二阱区中至少一个阱区拐角处位置的电场强度,进而提升半导体器件的击穿电压,有助于提升半导体器件的击穿特性。

32、本技术实施例的第五方面,提供一种电子设备,包括集成电路和印刷线路板,集成电路与印刷线路板电连接;集成电路包括第一方面和第二方面的半导体器件。

33、本技术实施例第五方面提供的电子设备,包括第一方面和第二方面的半导体器件,其有益效果与半导体器件的有益效果相同,在此不再赘述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/179235.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表