SOI衬底结构及其制备方法

- 国知局

- 2024-07-31 18:49:38

本发明涉及半导体器件领域,特别是涉及一种soi衬底结构及其制备方法。

背景技术:

1、射频(radio frequency,rf)器件需要保持较高的信号传输效率,保持较小的信号损耗,射频器件周围的衬底材料需要具有良好的绝缘性能。因此,大量rf器件、系统被制作在绝缘体上半导体(semiconductor-on-insulator,soi)衬底上。

2、在面向射频应用的soi衬底中,需要使靠近器件区域的衬底层保持高阻状态,以避免射频信号在衬底中形成较大能量损耗。然而,由于soi衬底的绝缘层中通常含有一定量的正电荷,当绝缘层与衬底层接触时,其可以吸引衬底层中的电子,并且使所吸引的电子在衬底层与绝缘层接触的界面处富集,形成较好的导电通路,造成较大的射频信号涡流损耗,一些情况下高频信号的电磁场甚至会穿透到衬底而引起串扰、寄生电容等电性能问题。图1a和图1b提供了两种典型的高电阻率soi衬底的结构示意图。

3、如图1a所示,该高电阻率soi衬底包括插置于衬底层与绝缘层之间的富陷阱多晶硅层(trap rich layer)110a,该soi衬底即为tr-soi,该多晶硅层含有较多的晶界缺陷,由于晶界缺陷可以阻挡载流子流动,因而绝缘层中的正电荷不会在多晶硅层中引入太大的射频信号损耗,而且衬底层通过多晶硅层与绝缘层分隔,免于受到绝缘层中正电荷影响。

4、如图1b所示,该高电阻率soi衬底包括插置于衬底层与绝缘层之间的多孔硅层110b,由于多孔硅层具有较大的电阻率,其也可免受绝缘层中正电荷的影响。

5、尽管如此,上述的高电阻率soi衬底存在如下的不足之处:

6、一)热导率低:如图1b所示的soi衬底,多孔硅层的热导率更低,甚至会起到绝热作用,不利于位于顶功能层中的器件散热。

7、2)高温性能差:如图1a所示的soi衬底,在器件工作温度较高时,例如在200℃时,高温会引起富陷阱的多晶硅(trap-rich poly)层中产生声子激发模式,产生较多的载流子,降低该层的电阻率,使射频信号的损耗增大。

8、3)不耐受高温工艺:如图1a所示的soi衬底的trap-rich poly层,当衬底工艺温度过高时,例如超过1100℃时,会引起多晶硅的重新结晶,并降低trap-rich poly层的电阻率,因而此种soi衬底的工艺温度上限较低;如图1b所示的soi衬底的多孔硅层,其高温稳定性也较差,当工艺温度较高时,例如超过950℃时,该多孔硅层有较大概率发生团聚结合形成多晶硅层,使得原本的多孔硅层电阻率降低,机械稳定性变差,严重影响射频器件性能。

9、4)机械稳定性差:如图1b所示的soi衬底,由于多孔硅层中的孔隙率一般在50%以上,相较于单晶硅、多晶硅多孔硅层的机械强度有大幅下降,使得当该soi衬底受到一定的工艺应力、机械力冲击时,该多孔硅层容易发生变形、断裂,进而严重影响工艺稳定性。

10、因此,急需寻找一种新型的soi衬底结构。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种soi衬底结构及其制作方法、及soi器件,用于解决现有的soi衬底在射频器件的应用中存在机械性能不佳、热导率和耐高温工艺不能满足需求等问题。

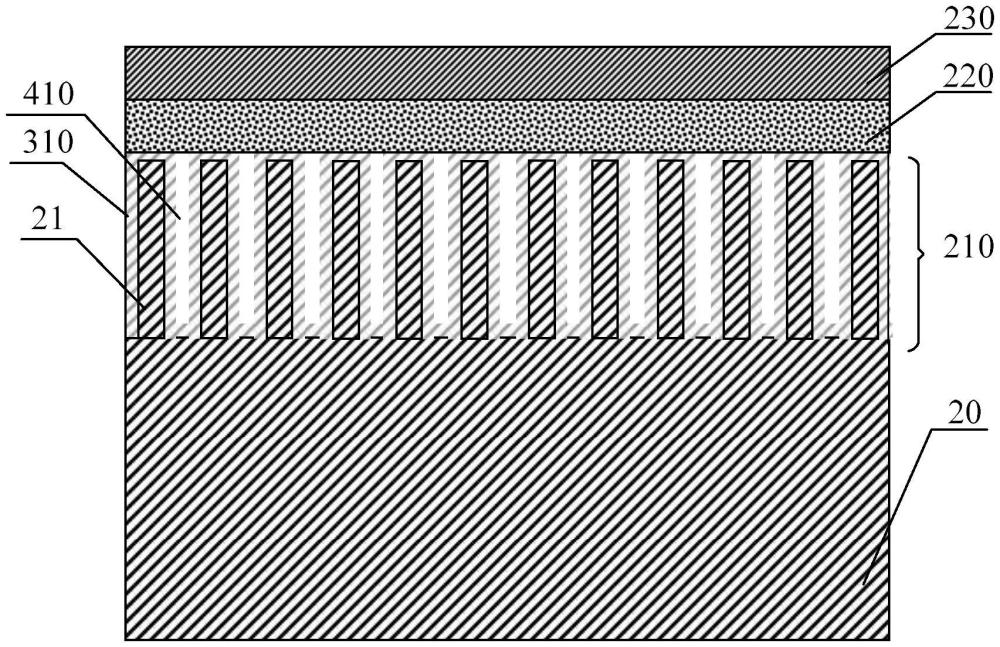

2、为实现上述目的及其他相关目的,本发明提供一种soi衬底结构,包括自下而上堆叠的衬底层、绝缘层和顶功能层,所述衬底层与所述绝缘层之间设置有中间隔离层,所述中间隔离层包括第一面和相对于所述第一面远离所述衬底层的第二面,所述中间隔离层包括自其第一面向第二面凸出的多个柱状支撑结构,所述柱状支撑结构包括中心柱体和包覆于所述中心柱体的壳层,所述柱状支撑结构远离所述衬底层的端部以一预定间距彼此间隔,所述中间隔离层之上设置有至少一绝缘层和至少一顶功能层。

3、可选地,所述中间隔离层之叠置有多层绝缘层和多层顶功能层;和/或,还包括空腔,所述空腔位于所述绝缘层和所述顶功能层中的一者中,或者两者的界面处。

4、可选地,所述中心柱体自所述中间隔离层邻接所述衬底层的第一面贯穿厚度方向设置,所述中心柱体具有与所述衬底层相接合的基部;所述中心柱体采用与所述衬底层相同的材质,或者不同的材质制成。

5、可选地,每一中心柱体具有平行于衬底层表面的非封闭形状的截面,所述中心柱体的截面形状包括条形成角度交叉构成的形状。

6、可选地,于所述衬底层上多个中心柱体分立设置,所述多个中心柱体中的一些各自具有平行于衬底层表面的放射状截面,所述中心柱体的放射状截面包括至少一细长部,所述细长部设置成朝向相邻的中心柱体延伸。

7、可选地,所述壳层围绕所述中心柱体的侧壁设置,而所述中心柱体的顶面和所述中心柱体之间显露的衬底层表面未覆盖所述壳层,所述壳层包括包覆于所述中心柱体的高阻壳层,所述高阻壳层具有不小于500ω·cm的电阻率;或者,

8、所述壳层围绕所述中心柱体的侧壁设置且覆盖所述中心柱体之间显露的衬底层表面,所述壳层包括包覆于所述中心柱体的半导体壳层,所述半导体壳层的材质包括多晶半导体材料、单晶半导体材料、非晶半导体材料中的一种。

9、可选地,所述壳层设置成复合壳层,所述复合壳层包括包覆所述中心柱体的裸露表面设置的第一高阻壳层和包覆于所述第一高阻壳层的第二高阻壳层,所述第一高阻壳层包含绝缘介质材料,所述第二高阻壳层包含多晶半导体材料。

10、可选地,所述柱状支撑结构之间的间隙保留有气隙或真空间隙;和/或,

11、所述柱状支撑结构之间的间隙形成有高阻填充物。

12、可选地,所述柱状支撑结构包括自所述中间隔离层的第一面朝内部延伸并终止于第二面的中心柱体,所述中心柱体由所述中间隔离层的第二面向第一面延伸而终止于所述中间隔离层内部的凹陷限定,自所述中间隔离层的第二面向内部的凹陷具有两种以上的深度;和/或,所述中心柱体远离所述衬底层的端部以不同的中心间距彼此间隔设置。

13、本发明还提供一种soi衬底结构的制备方法,其特征在于,包括以下步骤:

14、提供一基底,所述基底包括衬底层及位于所述衬底层之上的中心柱体,所述中心柱体背向所述衬底层凸出;

15、包覆所述中心柱体形成壳层以构成柱状支撑结构,所述柱状支撑结构远离所述衬底层的端部以一预定间距彼此间隔;

16、于所述柱状支撑结构之上交替形成至少一绝缘层和至少一顶功能层。

17、可选地,形成所述壳层的步骤,包括:

18、覆盖所述中心柱体形成半导体壳层,所述半导体壳层的材质包括多晶半导体材料、单晶半导体材料、非晶半导体材料中的一种;和/或,

19、覆盖所述中心柱体形成高阻壳层,所述高阻壳层具有不小于500ω·cm的电阻率。

20、可选地,形成所述壳层的步骤之后,包括:

21、用所述绝缘层覆盖所述柱状支撑结构的顶面,对所述柱状支撑结构之间的间隙进行密封,所述间隙形成为气隙或真空间隙;和/或,

22、于所述柱状支撑结构之间的间隙形成高阻填充物。

23、可选地,形成所述壳层的步骤之后,包括:

24、用所述高电阻率材料填充所述间隙并覆盖所述柱状支撑结构;随后,

25、对覆盖有高电阻率材料的柱状支撑结构进行减薄,显露出所述中心柱体的顶面,保留于所述间隙内的高电阻率材料形成为高阻填充物。

26、本发明还提供一种soi衬底结构的制备方法,包括以下步骤:

27、提供一soi衬底,所述soi衬底自下而上包括背衬底、绝缘层和顶功能层,图形化所述背衬底,形成贯穿所述背衬底的中心柱体;

28、包覆所述中心柱体形成壳层以构成柱状支撑结构,所述柱状支撑结构远离所述绝缘层的端部以一预定间距彼此间隔,由此得到包括所述柱状支撑结构的soi衬底结构。

29、可选地,形成所述壳层的步骤之后,包括:于所述柱状支撑结构之间的间隙形成高阻填充物。

30、本发明还提供一种soi器件,所述soi器件基于以上所述的soi衬底结构制备得到。

31、如上所述,本发明的soi衬底结构及其制备方法,具有以下有益效果:

32、本发明提供的soi衬底结构,通过于衬底层与绝缘层之间引入中间隔离层,中间隔离层包括沿其厚度方向延伸的柱状支撑结构,多个柱状支撑结构远离衬底层的端部以一预定间距彼此间隔,采用壳层包覆作为芯层的中心柱体,构成柱状支撑结构,能够明显提升柱状支撑结构的面积占比,提升soi衬底结构整体的机械支撑能力和导热能力,更好地满足射频器件应用的需求。

33、soi衬底结构的制备方法,基于衬底形成中心柱体,可通过刻蚀工艺形成中心柱体,包覆中心柱体形成壳层,能够拓宽刻蚀工艺的裕度,具有较高的工艺稳定性,提升soi衬底结构的加工质量,本发明的soi衬底结构的制备方法与现有的cmos工艺高度兼容,具有制造成本低,制造周期短,工艺一致性高等优势,可实现批量生产,能够满足产线生产需求,具有高度产业利用价值。

本文地址:https://www.jishuxx.com/zhuanli/20240731/180655.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

玻璃天线和车辆的制作方法

下一篇

返回列表