立体高集成肖特基势垒二极管及制备方法

- 国知局

- 2024-07-31 18:51:08

本发明属于半导体器件领域,尤其涉及立体高集成肖特基势垒二极管及制备方法。

背景技术:

1、随着电子技术的不断扩展和进步,功率半导体器件正经历着持续的创新和发展,以满足不断增长的应用需求。为了应对这一趋势,功率半导体器件进行了更高程度的集成和模块化设计,针对性选择了具备高击穿场强、高温稳定性、高导电性和高抗辐射性等优点的第三代宽禁带半导体材料(例如sic、gan),并且通过优化器件结构和设计等诸多方式提升和改善器件性能。

2、现如今,功率半导体器件出现了一系列新结构以不断提升器件性能,如鳍式晶体管(finfet)和全环绕栅极晶体管(gate-all-around fet)等,功率器件的发展也呈现出集成化和多功能化的趋势。然而,高集成化的器件散热问题一直困扰着功率半导体器件的发展,目前亟需更先进的封装技术和散热设计解决功率器件的热管理问题,确保器件在高温环境下的可靠性,以提高整体系统的性能和寿命。

技术实现思路

1、本发明的目的在于至少一定程度上解决相关技术中高集成化的功率器件散热性差的问题,提供了一种立体高集成肖特基势垒二极管及制备方法。

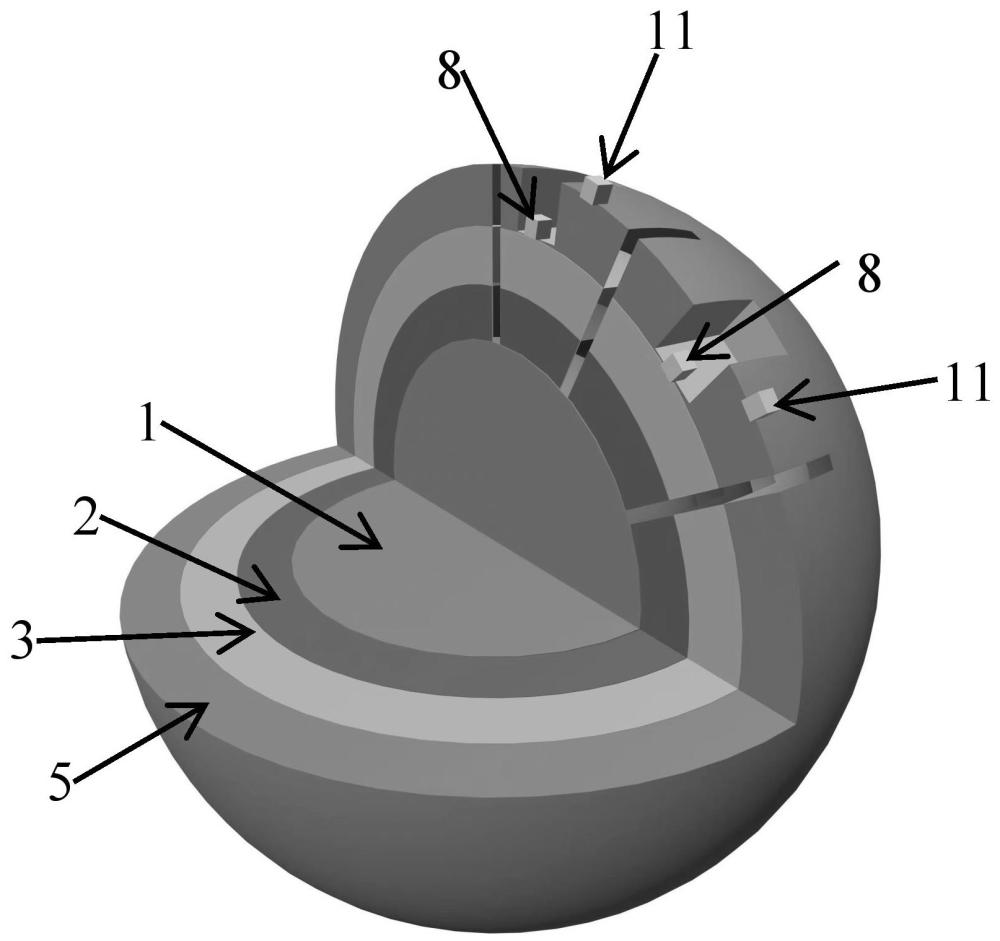

2、为解决上述技术问题,本发明第一方面提供了一种立体高集成肖特基势垒二极管,包括:

3、立体衬底,外表面具有若干器件区域;

4、若干器件,各所述器件对应设置于所述立体衬底的各所述器件区域上,所述器件包括设置于所述立体衬底表面的第一介质层,设置于所述第一介质层表面的n+-gan掺杂层,设置于所述n+-gan掺杂层上的背离所述第一介质层的至少部分表面的阴极和n--gan掺杂层,设置于所述n--gan掺杂层背离所述n+-gan掺杂层的一面上的阳极;

5、绝缘介电层,覆盖于各所述器件上的未接触所述立体衬底的除所述阴极和所述阳极之外的表面;

6、互联介质层,覆盖所述绝缘介电层上背离所述立体衬底的一侧,所述互联介质层固定有若干互联金属,各所述器件之间对应的阳极通过所述互联金属连接,各所述器件之间对应的阴极也通过所述互联金属连接。

7、进一步地,所述互联介质层包括第二介质层,所述第二介质层覆盖于所述绝缘介电层上背离所述立体衬底的一侧,所述第二介质层上具有第一互联金属,各所述器件之间的对应的阴极通过所述第一互联金属连接。

8、进一步地,所述互联介质层还包括第三介质层,所述第三介质层覆盖于所述第二介质层以及所述第一互联金属上,所述第三介质层上具有第二互联金属,各所述器件之间的对应的阳极通过所述第二互联金属连接。

9、进一步地,所述n+-gan掺杂层掺杂si,掺杂浓度为1×1018cm-3~1×1019cm-3;所述n--gan掺杂层掺杂si,掺杂浓度为1×1016cm-3~5×1016cm-3。

10、进一步地,所述阴极为ti/al/ni/au或ti/al/ti/au;所述阳极为ni/au或pt/au。

11、进一步地,所述立体衬底呈球体、多面体或圆柱体状。

12、本发明第二方面提供了一种立体肖特基势垒二极管的制备方法,包括:

13、提供立体衬底,所述立体衬底的外表面具有若干器件区域;

14、在所述立体衬底的外表面上依次生长第一介质层、n+-gan掺杂层以及n--gan掺杂层,刻蚀在所述立体衬底的非器件区域的所述第一介质层、所述n+-gan掺杂层以及所述n--gan掺杂层,暴露出所述立体衬底的非器件区域的表面;

15、将所述n+-gan掺杂层、所述n--gan掺杂层以及所述立体衬底上暴露的部分生长一层绝缘介电层;

16、将各所述器件的部分所述n+-gan掺杂层表面的所述绝缘介电层刻蚀开孔,并在开孔处生长阴极;将各所述器件的部分所述n--gan掺杂层表面的所述绝缘介电层刻蚀开孔,并在开孔处生长阳极;

17、在所述绝缘介电层表面生长互联介质层,在所述互联介质层上对应于所述阴极和所述阳极的位置刻蚀开孔,在所述互联介质层上生长互联金属,使部分所述互联金属连接各所述器件上的所述阴极,部分所述互联金属连接各所述器件上的所述阳极。

18、进一步地,所述在所述立体衬底的外表面上依次生长第一介质层、n+-gan掺杂层以及n--gan掺杂层,刻蚀在所述立体衬底的非器件区域的所述第一介质层、所述n+-gan掺杂层以及所述n--gan掺杂层,暴露出所述立体衬底的非器件区域的表面,具体包括:

19、使用物理气相沉积或化学气相沉积在所述立体衬底的外表面上生长第一介质层;

20、使用化学气相沉积的方法在所述第一介质层上依次生长所述n+-gan掺杂层和所述n--gan掺杂层;

21、使用光刻及刻蚀工艺去除所述立体衬底的非器件区域的所述n--gan掺杂层;

22、使用干法刻蚀以及湿法刻蚀去除部分位置的所述n+-gan掺杂层和所述第一介质层,暴露出所述立体衬底的非器件区域的表面。

23、进一步地,所述将所述n+-gan掺杂层、所述n--gan掺杂层以及所述立体衬底上暴露的部分生长一层绝缘介电层;将各所述器件的部分所述n+-gan掺杂层表面的所述绝缘介电层刻蚀开孔,并在开孔处生长阴极;将各所述器件的部分所述n--gan掺杂层表面的所述绝缘介电层刻蚀开孔,并在开孔处生长阳极,具体包括:

24、使用化学气相沉积法在所述n+-gan掺杂层、所述n--gan掺杂层以及所述立体衬底上暴露的部分生长一层绝缘介电层;

25、使用光刻及刻蚀工艺将各所述器件的部分所述n+-gan掺杂层表面的所述绝缘介电层开孔,并在开孔处蒸镀金属膜,掀金去胶形成阴极后退火;

26、使用光刻及刻蚀工艺将各所述器件的部分所述n--gan掺杂层表面的所述绝缘介电层开孔,并在开孔处蒸镀金属膜,掀金去胶后形成阳极。

27、进一步地,所述在所述绝缘介电层表面生长互联介质层,在所述互联介质层上对应于所述阴极和所述阳极的位置刻蚀开孔,在所述互联介质层上生长互联金属,使部分所述互联金属连接各所述器件上的所述阴极,部分所述互联金属连接各所述器件上的所述阳极,具体包括:

28、在所述绝缘介电层表面生长第二介质层,在所述第二介质层上对应于所述阴极的位置刻蚀开孔,在所述第二介质层上生长第一互联金属,使所述第一互联金属连接各所述器件上的所述阴极;

29、在所述第二介质层和所述第一互联金属表面生长第三介质层,在所述第三介质层上对应于所述阳极的位置刻蚀开孔,在所述第三介质层上生长第二互联金属,使所述第二互联金属连接各所述器件之间的所述阳极。

30、进一步地,所述在所述绝缘介电层表面生长第二介质层,在所述第二介质层上对应于所述阴极的位置刻蚀开孔,在所述第二介质层上生长第一互联金属,使所述第一互联金属连接各所述器件上的所述阴极,具体包括:

31、使用物理气相沉积法在所述绝缘介电层、所述阴极和所述阳极表面生长所述第二介质层,对所述第二介质层的表面平整化;

32、采用光刻和刻蚀工艺使所述第二介质层上对应于所述阴极的区域开孔,暴露出所述阴极;

33、在所述第二介质层上沉积第一互联金属并掀金去胶,使所述第一互联金属接触各所述器件上的所述阴极;

34、所述在所述第二介质层和所述第一互联金属表面生长第三介质层,在所述第三介质层上对应于所述阳极的位置刻蚀开孔,在所述第三介质层上生长第二互联金属,使所述第二互联金属连接各所述器件之间的所述阳极,具体包括:

35、使用物理气相沉积法在所述第二介质层和所述第一互联金属表面生长第三介质层,对所述第三介质层的表面平整化;

36、采用光刻和刻蚀工艺使所述第三介质层上对应于所述阳极的区域开孔,暴露出所述阳极;

37、在所述第三介质层上沉积第二互联金属并掀金去胶,使所述第二互联金属接触各所述器件上的所述阳极。

38、本发明中的立体高集成肖特基势垒二极管及制备方法与现有技术相比,有益效果在于:

39、首先,通过在立体衬底上集成多个肖特基势垒二极管器件,并通过互联介质层内的互联金属实现各器件之间的互联,提升了肖特基势垒二极管的电流密度和功率密度,能够更好地应用于大功率场合;

40、其次,相比于平面的衬底,立体衬底有利于肖特基势垒二极管器件更好地散热,提升了器件在高温环境下的可靠性,提高了器件的性能和寿命;

41、最后,本发明的器件还使用了n+-gan掺杂层和n--gan掺杂层,利用了氮化镓材料的高击穿场强、高温稳定性优异以及更高开关频率等特性进一步提升了器件的性能和寿命。

本文地址:https://www.jishuxx.com/zhuanli/20240731/180787.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表