电阻式内存单元的阻丝成型方法与流程

- 国知局

- 2024-07-31 19:13:00

本发明涉及一种电阻式内存单元的阻丝成型方法。

背景技术:

1、电阻式内存由于具备低功耗、高速运作、高密度以及兼容于互补式金属氧化物半导体制程技术的潜在优势,因此非常适合作为下一世代的非易失性内存组件。

2、图1显示一般1t1r的电阻式内存的结构示意图。如图1所示,电阻式内存通常包括电阻组件r与开关组件t。电阻组件r包括相对配置的上电极14b与下电极14a以及位于上电极14b与下电极14a之间的介电层(例如,过渡金属氧化物(transition metal oxide,tmo)12。在电阻式内存可反复地在高低电阻状态间切换以存储数据前,首先需进行阻丝成型(filament forming)的程序。阻丝成型程序包括对电阻式内存施加一偏压。例如在开关组件t的栅极施加栅极电压vg,在电阻组件r之上电极14b施加漏极电压vd。上述偏压例如正偏压,使得介电层中产生氧空缺和氧离子,并使氧离子脱离介电层(tmo)而在介电层中形成电流路径(阻丝结构),进而使电阻式内存自高阻态变为低阻态。之后,可对电阻式内存进行重设(reset)或设定(set)程序,使电阻式内存分别切换为高阻态与低阻态,以完成数据的存储。

3、图2显示阻丝成型过程中作用在介电层(如tmo)的电压与成型电流(即成型程序完成后的读取电流)的关系以及与栅极电压的相关性。由图2可以得知,当栅极电压vg在1.5v以上时,作用在tmo上的电压会太小(如图所示的0.3v以下),因而无足够的电场推动氧离子脱离tmo。当栅极电压vg太低(如vg=0.65v)的话,虽然作用在tmo的电压增加,但成型电流几乎为0,代表tmo中未产生足够的氧空缺以形成电流路径。因此,难以选择合适的栅极电压vg来进行阻丝成型,进而导致成型效率不佳。

4、图3显示现有技术在阻丝成型后,进行初始(第一次)重设前后的电流变化图,图中x轴为初始重设前电流,y轴为初始重设后的电流。阻丝成型后当电流太早而初始重设被执行,重设后很多比特会增加电流而不是减少电流。亦即,成型的阻丝结构可能不够稳定,而导致电阻式内存的可靠度退化。这也会关系到成型效率。

5、综上所述,需要有一种更可靠的成型方式,使足够的氧离子脱离tmo,形成稳定的阻丝结构,并降低电流尾的状态产生。

技术实现思路

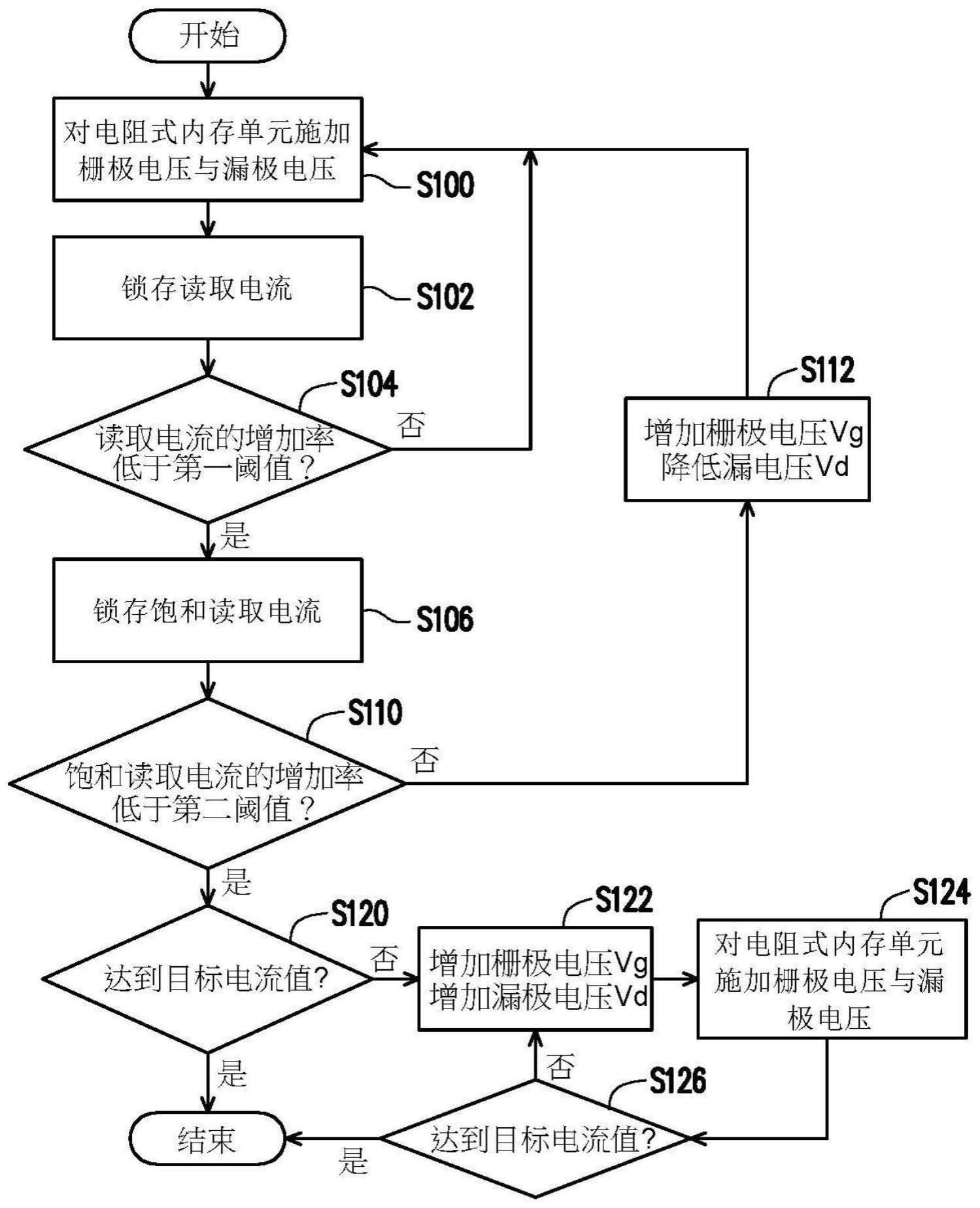

1、根据本发明一实施例,提供一种电阻式内存的阻丝成型方法,包括:对所述电阻式内存单元施加多次第一偏压,直到所述电阻式内存单元的读取电流达到第一饱和状态,其中所述多次第一偏压的各次包括栅极电压与漏极电压;锁存所述第一饱和状态的所述读取电流作为饱和读取电流,并判断所述饱和读取电流的增加率是否低于第一阈值;在判断出所述饱和读取电流的增加率未低于第一阈值时,对所述第一偏压,增加所述栅极电压并且降低所述漏极电压,以作为第二偏压;以所述第二偏压施加至所述电阻式内存单元,直到所述电阻式内存单元的所述读取电流达到第二饱和状态;锁存所述第二饱和状态的所述读取电流作为所述饱和读取电流,并再次判断所述饱和读取电流的增加率是否低于所述第一阈值;以及判断所述饱和读取电流是否达到目标电流值,并且在达到所述目标电流值的情况下,结束所述成型方法。

2、根据本发明另一实施例,提供一种电阻式内存单元的阻丝成型方法,包括:执行第一阶段成型程序,以包括栅极电压与漏极电压的第一偏压施加多次到所述电阻式内存单元,直到所述电阻式内存单元的读取电流达到第一饱和状态,锁存所述第一饱和状态的所述读取电流为饱和读取电流,并判断所述饱和读取电流的增加率是否低于第一阈值;在所述饱和读取电流的增加率未低于所述第一阈值时,执行第二阶段成型程序,以第二偏压施加多次到所述电阻式内存单元,直到所述电阻式内存单元的所述读取电流达到第二饱和状态,并判断所述饱和读取电流的增加率是否低于所述第一阈值,其中所述第二偏压为增加所述栅极电压并且降低所述漏极电压;以及在所述所述饱和读取电流的增加率低于第一阈值时,并且在所述饱和读取电流达到目标电流值时,结束所述阻丝成型方法。

技术特征:1.一种电阻式内存单元的阻丝成型方法,包括:

2.根据权利要求1所述的电阻式内存单元的阻丝成型方法,其特征在于,在所述读取电流的增加率低于第二阈值时,判断所述读取电流达到所述第一饱和状态。

3.根据权利要求1所述的电阻式内存单元的阻丝成型方法,其特征在于,在锁存所述第二饱和状态的所述读取电流作为所述饱和读取电流,并判断出所述饱和读取电流的增加率未低于所述第一阈值的状况下,还包括:

4.根据权利要求1所述的电阻式内存单元的阻丝成型方法,其特征在于,还包括:

5.根据权利要求2所述的电阻式内存单元的阻丝成型方法,其特征在于,所述第二阈值由锁存所述读取电流的存储单元的比特数来决定。

6.根据权利要求5所述的电阻式内存单元的阻丝成型方法,其特征在于,所述比特数为n(n为正整数)时,所述第二阈值为1/2n。

7.根据权利要求1所述的电阻式内存单元的阻丝成型方法,其特征在于,所述漏极电压大于所述栅极电压。

8.一种电阻式内存单元的阻丝成型方法,包括:

9.根据权利要求8所述的电阻式内存单元的阻丝成型方法,其特征在于,在所述读取电流的增加率低于第二阈值时,判断所述读取电流达到所述第一饱和状态。

10.根据权利要求8所述的电阻式内存单元的阻丝成型方法,其特征在于,在以所述第二饱和状态的所述读取电流为所述饱和读取电流,并判断出所述饱和读取电流的增加率未低于所述第一阈值的状况下,还包括:以第三偏压施加多次到所述电阻式内存单元,再次执行所述第二阶段成型程序,直到所述电阻式内存单元的所述读取电流达到第三饱和状态,锁存所述第三饱和状态的所述读取电流为所述饱和读取电流,并判断所述饱和读取电流的增加率是否低于所述第一阈值,其中所述第三偏压为相对于所述第二偏压,增加所述栅极电压并且降低所述漏极电压。

11.根据权利要求8所述的电阻式内存单元的阻丝成型方法,其特征在于,还包括:

12.根据权利要求9所述的电阻式内存单元的阻丝成型方法,其特征在于,所述第二阈值由锁存所述读取电流的存储单元的比特来决定。

13.根据权利要求12所述的电阻式内存单元的阻丝成型方法,其特征在于,所述比特数为n(n为正整数)时,所述第二阈值为1/2n。

14.根据权利要求8所述的电阻式内存单元的阻丝成型方法,其特征在于,所述漏极电压大于所述栅极电压。

技术总结一种电阻式内存单元阻丝成型方法,包括:在第一阶段成型,以包括栅极与漏极电压的第一偏压施加多次到电阻式内存单元。当第一阶段成型进行至读取电流达到第一饱和状态,锁存第一饱和状态的读取电流为饱和读取电流,判断饱和读取电流的增加率是否低于第一阈值。当饱和读取电流的增加率未低于第一阈值时,执行第二阶段成型,施加第二偏压多次到内存单元,直到电阻式内存单元的读取电流达到第二饱和状态,锁存所述第二饱和状态的所述读取电流为所述饱和读取电流,并判断饱和读取电流的增加率是否低于第一阈值,第二偏压为增加栅极电压并且降低漏极电压。在饱和读取电流的增加率未低于第一阈值时,且在饱和读取电流达到目标电流值时,结束此方法。技术研发人员:陈达,王炳琨,林家鸿,黄俊尧受保护的技术使用者:华邦电子股份有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/181890.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表