基于总线的SRAM实时自检和修复方法、装置及系统与流程

- 国知局

- 2024-07-31 19:12:56

本发明涉及芯片检测及修复,具体涉及基于总线的sram实时自检和修复方法、装置及系统。

背景技术:

1、当前芯片内部sram(静态随机存取存储器)的测试通常在芯片出厂时进行,主要使用mbist(memory built-in self-test,内存内建自测)技术,mbist是一种使用集成在芯片内部的mbist电路对芯片的内部存储器单元进行测试的技术。mbist技术可以在芯片的制造过程中采用提前内部自检测试,提高产品质量。但使用mbist技术测试,不能够最接近实际使用中芯片的运行状态,另外随着长时间的使用,sram可能出现新的故障,mbist也无法在芯片运行过程中对于sram进行实时的故障检测,不能保证装有sram的芯片的工作可靠性。

2、虽然cn115954041a提出了一种静态随机存取存储器的实时自检测方法、系统、芯片、电子设备及可读存储介质,但是使用的方法为通过往存储单元中写入一个特殊数据并读出进行比较或者再次写入一个不同特殊数据并读出进行比较来进行检测。一方面,该方法能在一定程度上检测出sram的部分固定型故障(stuck-at faults,saf),但是对于跳变故障(transition faults,tf),耦合故障(coupling faults,cf),相邻图形敏感故障(neighborhood pattern sensitive faults,npsf)和地址译码故障(addressdecoderfaults,adf)等不能进行检测和修复,检测的故障覆盖率低。另外在自检测过程中会对sram的数据造成破坏,可能使芯片出现意料之外的错误。

3、另一方面检测得到的故障存储单元的地址在断电后不能保存,在芯片上电到自检测完成前的时间里可能因为使用了故障存储单元而造成不必要的错误。

技术实现思路

1、本发明所要解决的技术问题是现有sram实时自检测方法测试时要停止芯片的正常运行且等待总线的空闲时间,且测试时可能会对sram的数据造成破坏;只能在一定程度上检测出sram的部分固定型故障,但是对于跳变故障,耦合故障,相邻图形敏感故障和地址译码故障等不能进行检测和修复,检测的故障覆盖率低;另外,检测得到的故障存储单元的地址在断电后不能保存,在芯片上电到自检测完成前的时间里可能因为使用了故障存储单元而造成不必要的错误等问题。

2、本发明目的在于提供基于总线的sram实时自检和修复方法、装置及系统,本发明不用停止芯片的正常运行并进入测试模式,也不用等待总线的空闲时间,在芯片正常运行过程中即可对芯片中的所有sram进行测试,测试结果更真实,更贴近于芯片实际运行状态;可以防止测试时的读写对sram中的数据的破坏;对于固定型故障(stuck-at faults,saf),跳变故障(transition faults,tf),相邻图形敏感故障(neighborhood patternsensitive faults,npsf)能完全检测。耦合故障(coupling faults,cf)和地址译码故障(address decoderfaults,adf)能部分检测;节约了保存故障存储单元的地址所需寄存器和故障地址存储器的大小。也减少了需对比的故障地址的数量和所需的面积;在芯片断电后不会丢失检测到的故障存储单元地址,且在芯片上电后快速取出并及时修复故障存储单元。

3、本发明通过下述技术方案实现:

4、第一方面,本发明提供了基于总线的sram实时自检和修复方法,该方法包括:

5、在芯片上电时,或在芯片使用过程中每经过一定时间间隔后,或者在芯片工作时由总线系统其他主机(如系统处理器等)指定某个sram时,向待测sram发起访问,并根据读回的值判断sram的存储单元是否存在故障:

6、当存在故障时,则将sram的故障存储单元的偏移地址存放于故障地址记录寄存器序列的相应区域中,并为所述偏移地址分配相应故障修复存储器的地址,将该地址存入地址重映射表的相应寄存器中;

7、在检测过程中,将待测sram区块的当前值读出并写入故障检测存储器;并在检测完成时,将故障检测存储器中的值读出并写入待测sram区块,从而完成恢复。

8、进一步地,在芯片上电时,向待测sram发起访问,并根据读回的值判断sram的存储单元是否存在故障,包括:

9、芯片上电后,将存放在故障地址存储器中的故障地址取出;

10、将取出的故障地址保存到故障地址记录寄存器序列中,为故障地址分配相应故障修复存储器的地址,并将该地址存入地址重映射表的相应寄存器中;

11、对故障检测存储器进行检测并将新出现的故障地址保存到故障地址记录寄存器序列中,为新出现的故障地址分配相应故障修复存储器的地址,并将该地址存入地址重映射表的相应寄存器中;

12、对故障修复存储器进行检测并将新出现的故障地址保存到故障地址记录寄存器序列中,为新出现的故障地址分配相应故障修复存储器的地址,将该地址存入地址重映射表的相应寄存器中;

13、对芯片中所有待测sram进行检测,并将新出现的故障地址保存到故障地址记录寄存器序列中,为新出现的故障地址分配相应故障修复存储器的地址,将该地址存入地址重映射表的相应寄存器中;

14、将故障地址记录寄存器序列中保存的故障地址更新到故障地址存储器中。

15、进一步地,在芯片使用过程中每经过一定时间间隔后,向待测sram发起访问,并根据读回的值判断sram的存储单元是否存在故障,包括:

16、在芯片使用过程中,对故障检测存储器进行检测并将新出现的故障地址保存到故障地址记录寄存器序列中,为新出现的故障地址分配相应故障修复存储器的地址,并将该地址存入地址重映射表的相应寄存器中;

17、对故障修复存储器进行检测并将新出现的故障地址保存到故障地址记录寄存器序列中,为新出现的故障地址分配相应故障修复存储器的地址,并将该地址存入地址重映射表的相应寄存器中;

18、对芯片中所有待测sram进行检测并将新出现的故障地址保存到故障地址记录寄存器序列中,为新出现的故障地址分配相应故障修复存储器的地址,将该地址存入地址重映射表的相应寄存器中;

19、将故障地址记录寄存器序列中保存的故障地址更新到故障地址存储器中。

20、进一步地,在芯片工作时由总线系统其他主机(如系统处理器等)指定某个sram时,向待测sram发起访问,并根据读回的值判断sram的存储单元是否存在故障,包括:

21、其他主机通过总线将待测sram的起始和结束地址写入寄存器单元中的相应寄存器,并控制检测开始;

22、对芯片中待测sram进行检测并将新出现的故障地址保存到故障地址记录寄存器序列中,为新出现的故障地址分配相应故障修复存储器的地址,并将该地址存入地址重映射表的相应寄存器中;

23、将故障地址记录寄存器序列中保存的故障地址更新到故障地址存储器中。

24、进一步地,对每个待测sram进行故障检测的流程,包括:

25、步骤1,判断故障检测存储器的大小是否小于待测sram大小;如果故障检测存储器的大小小于待测sram,则将待测sram划分为多个与故障检测存储器的大小相同的区块且相邻区块之间需有至少两行的重合,并分区块进行检测;如果故障检测存储器的大小不小于待测sram,则直接开始检测;

26、步骤2,获取当前区块的起始地址与结束地址,将该区块的当前数据读出并写入故障检测存储器,并同步将该区块的地址重映射到故障检测存储器;

27、步骤3,往该区块中顺序写入测试数据;

28、步骤4,从起始地址开始读出当前地址的数据并判断是否与测试数据相等;如果相等,则往当前地址写入测试数据取反后的值;如果不相等,则认为当前地址对应的存储单元存在故障,判断故障地址记录寄存器序列中是否存在当前地址,如果不存在,则将当前地址存入故障地址记录寄存器序列中,并为当前地址分配相应故障修复存储器的地址,将该地址存入地址重映射表的相应寄存器中;如果已经存在,则不做任何处理;

29、步骤5,地址进行累加并执行步骤4的检测,直到当前区块的结束地址;

30、步骤6,将故障检测存储器的当前数据读出并写入该区块,并同步解除到故障检测存储器的地址重映射。

31、进一步地,对每个待测sram进行故障检测的流程,在步骤5与步骤6之间还包括:

32、步骤a,从起始地址开始读出当前地址的数据并判断是否与测试数据取反后的值相等;如果相等,则往当前地址再次写入测试数据;如果不相等,则认为当前地址对应的存储单元存在故障,判断故障地址记录寄存器序列中是否存在当前地址,如果不存在,则将当前地址存入故障地址记录寄存器序列中,并为当前地址分配相应故障修复存储器的地址,将该地址存入地址重映射表的相应寄存器中;如果已经存在,则不做任何处理;

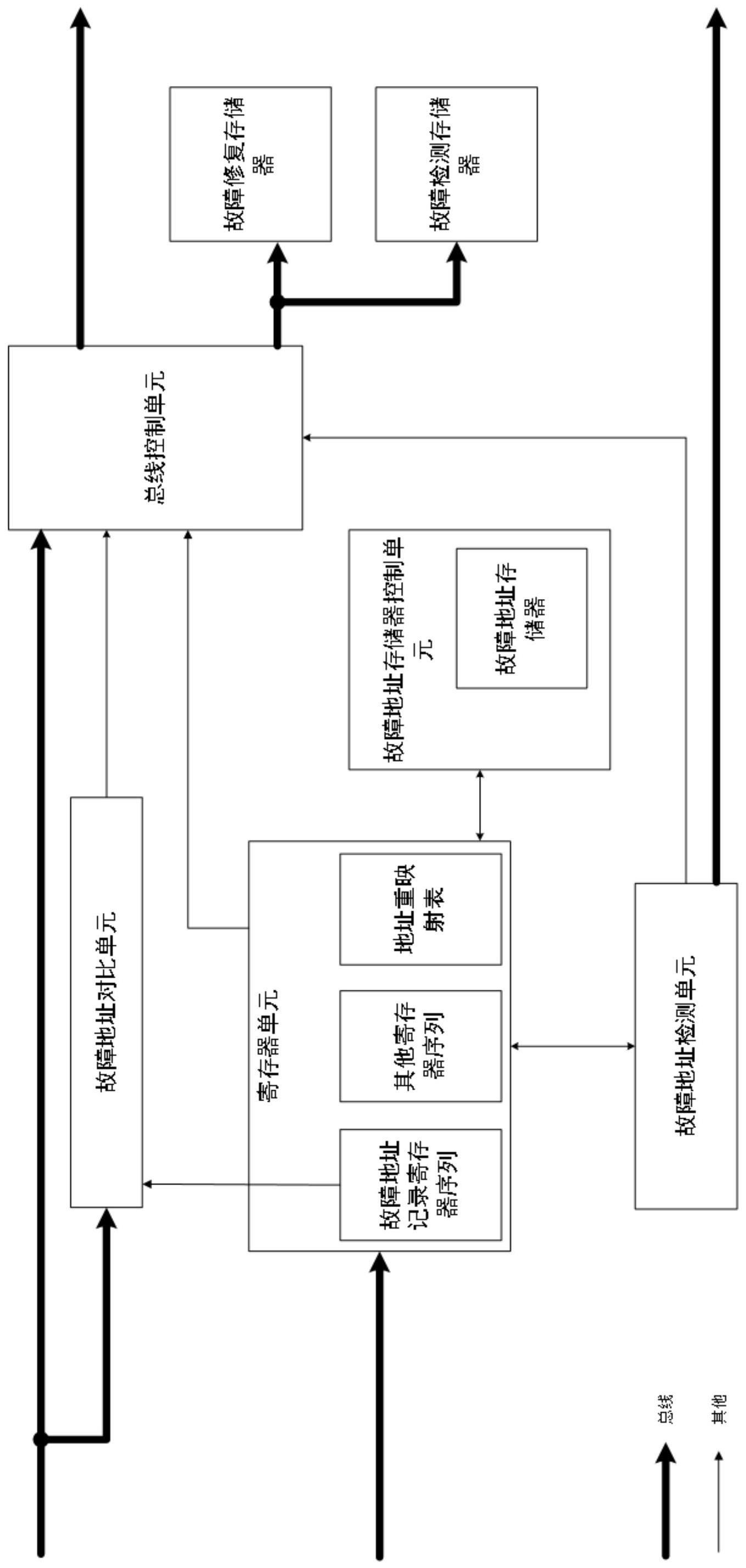

33、步骤b,地址进行累加并执行步骤a的检测,直到当前区块的结束地址;

34、步骤c,从起始地址开始读出当前地址的数据并判断是否与测试数据相等;如果相等,则认为当前地址对应的存储单元不存在故障;如果不相等,则认为当前地址对应的存储单元存在故障,判断故障地址记录寄存器序列中是否存在当前地址,如果不存在,则将当前地址存入故障地址记录寄存器序列中,并为当前地址分配相应故障修复存储器的地址,将该地址存入地址重映射表的相应寄存器中;如果已经存在,则不做任何处理;

35、步骤d,地址进行累加并执行步骤c的检测,直到当前区块的结束地址。

36、进一步地,该方法还包括:对sram的故障存储单元进行修复,具体为:

37、根据当前总线访问的从机编号或者地址,筛选出相应从机对应的故障地址记录寄存器;

38、将筛选出的故障地址记录寄存器中保存的偏移地址与当前总线地址进行比较;

39、如果当前总线地址不存在于故障地址记录寄存器中,则不做任何处理,让当前总线传输直接通过;

40、如果当前总线地址存在于故障地址记录寄存器中,则将送往该从机的传输设置为空闲,并根据地址重映射表将访问重映射到故障修复存储器的相应地址并响应该总线传输。

41、第二方面,本发明又提供了基于总线的sram实时自检和修复装置,该装置使用上述的基于总线的sram实时自检和修复方法;该装置包括:

42、寄存器单元,包括故障地址记录寄存器序列、地址重映射表和其他寄存器序列;故障地址记录寄存器序列,用于保存在芯片上电时读出的故障地址存储器中的故障地址和保存故障地址检测单元检测到的故障地址;地址重映射表,用于保存故障修复存储器中用于置换sram内故障存储单元的相应存储单元的偏移地址;

43、故障地址存储器控制单元,用于在芯片上电时将故障地址存储器中保存的故障地址会被读出并放置到故障地址记录寄存器序列中;在故障检测结束后将故障地址记录寄存器序列中的故障地址写入故障地址存储器;

44、故障地址对比单元,用于监视总线送往各个从机的地址,根据当前总线选择的从机将总线地址与从故障地址记录寄存器序列中保存的相应从机的故障存储单元偏移地址进行比较,并将比较结果输出到总线控制单元;

45、总线控制单元,用于根据所述比较结果及地址重映射表,将相应总线传输重映射到故障修复存储器上;及在sram检测时将访问待测sram区块的总线传输重映射到故障检测存储器上;

46、故障检测存储器,用于在sram检测期间代替待测sram区块参与总线传输;

47、故障修复存储器,用于在各个sram中存在故障存储单元时作为故障存储单元的替换存储单元使用;

48、故障检测单元,用于在芯片上电时,或在芯片使用过程中每经过一定时间间隔后,或者在芯片工作时由总线系统其他主机(如系统处理器等)指定某个sram时,向待测sram发起访问,并根据读回的值判断sram的存储单元是否存在故障,即进行故障检测。

49、进一步地,所述故障地址存储器的大小是根据总线系统中的所有sram的容许的故障地址的个数之和决定;

50、所述故障修复存储器的大小是根据总线系统中的所有sram的容许的故障存储单元的个数之和决定;

51、所述故障地址记录寄存器序列的大小是根据总线系统中的所有sram的容许的故障地址的个数之和决定。

52、第三方面,本发明又提供了基于总线的sram实时自检和修复系统,该系统包括若干主机、若干从机以及sram实时自检测和修改模块,所述sram实时自检测和修改模块设置于主机和从机之间,各个主机通过总线连接所述sram实时自检测和修改模块,所述sram实时自检测和修改模块连接各主机;其中,所述sram实时自检测和修改模块采用如权利要求8至9中任一所述的基于总线的sram实时自检和修复装置。

53、所述sram实时自检测和修改模块在总线中既是从机也是主机,作为从机时,可以接收来自其他主机的控制,其他主机可以控制自检测的开始地址与结束地址,也可以随时启动对任意地址范围的故障检测;作为主机时,可以发起对任意地址范围的故障检测,所述sram实时自检测和修改模块在总线上的优先度一般设置为最低,能够在其他主机进行总线传输时进行避让,保证自检测不会对系统的处理速度造成影响。

54、另外在对总线系统中的sram进行故障修复时会监视总线送往各个从机的地址,在总线地址与故障地址一致时将该访问重映射到故障修复存储器中以保证数据的正确性,避免系统因为sram故障而引起错误。

55、本发明与现有技术相比,具有如下的优点和有益效果:

56、1、本发明基于总线的sram实时自检和修复方法、装置及系统,本发明添加了一块故障检测存储器,通过将待测sram的总线传输重映射到故障检测存储器中,使得不用停止芯片的正常运行并进入测试模式,也不用等待总线的空闲时间,在芯片正常运行过程中即可对芯片中的所有sram进行测试;测试结果更真实,更贴近于芯片实际运行状态;在检测开始时将待测sram的现有数据进行了转移,检测结束后将最新数据写回待测sram,防止了测试时的读写对sram中的数据的破坏,可以防止测试时的读写对sram中的数据的破坏。

57、2、本发明基于总线的sram实时自检和修复方法、装置及系统,对待测sram进行分区测试,能有效缩小测试所需的故障检测存储器的大小,节约了面积;对于固定型故障(stuck-at faults,saf),跳变故障(transition faults,tf),相邻图形敏感故障(neighborhood pattern sensitive faults,npsf)能完全检测。耦合故障(couplingfaults,cf)和地址译码故障(address decoderfaults,adf)能部分检测。

58、3、本发明基于总线的sram实时自检和修复方法、装置及系统,只需要保存故障存储单元在相应sram的偏移地址,有效节约了保存故障存储单元的地址所需寄存器和故障地址存储器的大小。在地址对比时只需对比当前从机的故障存储单元的偏移地址,减少了需对比的故障地址的数量和所需的面积;支持针对某个sram的整体或者部分进行检测,能在需要时快速对某一区域进行检测;另外,添加了故障地址存储器,在芯片断电后不会丢失检测到的故障存储单元地址。且在芯片上电后快速取出并及时修复故障存储单元。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181883.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表