一种基于增强型N沟道与增强型P沟道GaN基晶体管的SRAM存储单元电路结构

- 国知局

- 2024-07-31 19:08:06

本发明属于sram电路,具体涉及一种基于增强型n沟道与增强型p沟道gan基晶体管的sram存储单元电路结构。

背景技术:

1、近年来,硅基器件正快速逼近其本征材料特性的理论极限,例如低饱和速度、低击穿电压、低反型层迁移率和高器件电阻。第三代半导体材料如gan,相比于si基材料,具有禁带宽度大、临界击穿电场高、饱和速度大、导热性好、耐高温以及耐腐蚀等优良的电学性能而被认为其适合应用在高频、大功率、强辐射等场合,且已经被证明有可能满足高温和高功率开关应用的要求。

2、对于原本的si基6t sram电路,其静态功耗较高,且高温、辐照稳定性和抗干扰能力极其有限,所以需在电路结构上做出改进,较为有代表性的是12t与14t结构的sram电路。如一种12t电路在漏电路径末尾增加使能端控制的传输门,偏置于深截至状态用于减小静态功耗,一种14t电路通过增加冗余存储节点这样的校验机制来对抗辐射及单粒子反转。

3、现有技术中的6t sram大多数采用si基器件制造,但是随着对芯片功耗、效率、速度的要求越来越高,si基器件正快速逼近其本征材料特性的理论极限,例如低饱和速度、低击穿电压、低反型层迁移率和高器件电阻。在少数利用e/d-mode gan的逻辑电路解决方案中,采用增强型与耗尽型hemt实现功能,但是耗尽型hemt是一种常开器件,这增加了电路的静态功耗,会影响芯片的整体性能。同时,现有的12t、14t sram电路为了克服静态功耗较高,稳定性差、抗干扰能力低等问题,增加了较多晶体管实现相应功能,所以其电路面积增幅非常大,电路结构复杂度提高,相应的制造成本也大幅提升。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种基于增强型n沟道与增强型p沟道gan基晶体管的sram存储单元电路结构。本发明要解决的技术问题通过以下技术方案实现:

2、一种基于增强型n沟道与增强型p沟道gan基晶体管的sram存储单元电路结构,包括:第一控制读写晶体管n3、第一反相器、第二控制读写晶体管n4和第二反相器;

3、所述第一反相器的输出端与所述第二反相器的输入端和所述第一控制读写晶体管n3的漏端相连;

4、所述第二反相器的输出端与所述第一反相器的输入端和所述第二控制读写晶体管n4漏端相连;

5、所述第一反相器的p沟道晶体管p1和所述第二反相器的p沟道晶体管p2均为氮化镓p沟道增强型异质结晶体管,其阈值电压小于零;

6、所述第一反相器的n沟道晶体管n1、所述第二反相器的n沟道晶体管n2、所述第一控制读写晶体管n3和所述第二控制读写晶体管n4均为氮化镓n沟道增强型异质结晶体管,其阈值电压大于零。

7、在本发明的一个实施例中,所述第一反相器的p沟道晶体管p1和所述第二反相器的p沟道晶体管p2的栅极的宽长比相同;

8、所述第一反相器电路的n沟道晶体管n1和所述第二反相器的n沟道晶体管n2的栅极的宽长比相同,所述第一控制读写晶体管n3和所述第二控制读写晶体管n4的栅极的宽长比相同。

9、在本发明的一个实施例中,所述第一反相器电路的n沟道晶体管n1和所述第二反相器的n沟道晶体管n2的漏极电流相等,且晶体管宽长比相等;

10、所述第一控制读写晶体管n3和所述第二控制读写晶体管n4的漏极电流相等,且晶体管宽长比相等;

11、所述第一反相器电路的n沟道晶体管n1的漏极电流大于所述第一控制读写晶体管n3的漏极电流;所述第一反相器电路的n沟道晶体管n1的晶体管宽长比与所述第一控制读写晶体管n3的晶体管宽长比之比大于1;

12、所述第一反相器的p沟道晶体管p1和所述第二反相器的p沟道晶体管p2的晶体管宽长比相同,且与所述第一反相器电路的n沟道晶体管n1的晶体管宽长比之比介于10~50。

13、在本发明的一个实施例中,所述第一反相器的p沟道晶体管p1和所述第二反相器的p沟道晶体管p2的漏极电流相等,所述第一反相器的p沟道晶体管p1的漏极电流小于所述第一控制读写晶体管n3的漏极电流;

14、所述第一反相器的p沟道晶体管p1的晶体管宽长比与所述第一控制读写晶体管n3的晶体管宽长比之比介于10~50。

15、在本发明的一个实施例中,所述第一反相器的p沟道晶体管p1的晶体管宽长比、所述第一控制读写晶体管n3的晶体管宽长比与所述第一反相器电路的n沟道晶体管n1的晶体管宽长比之比为40:1:2。

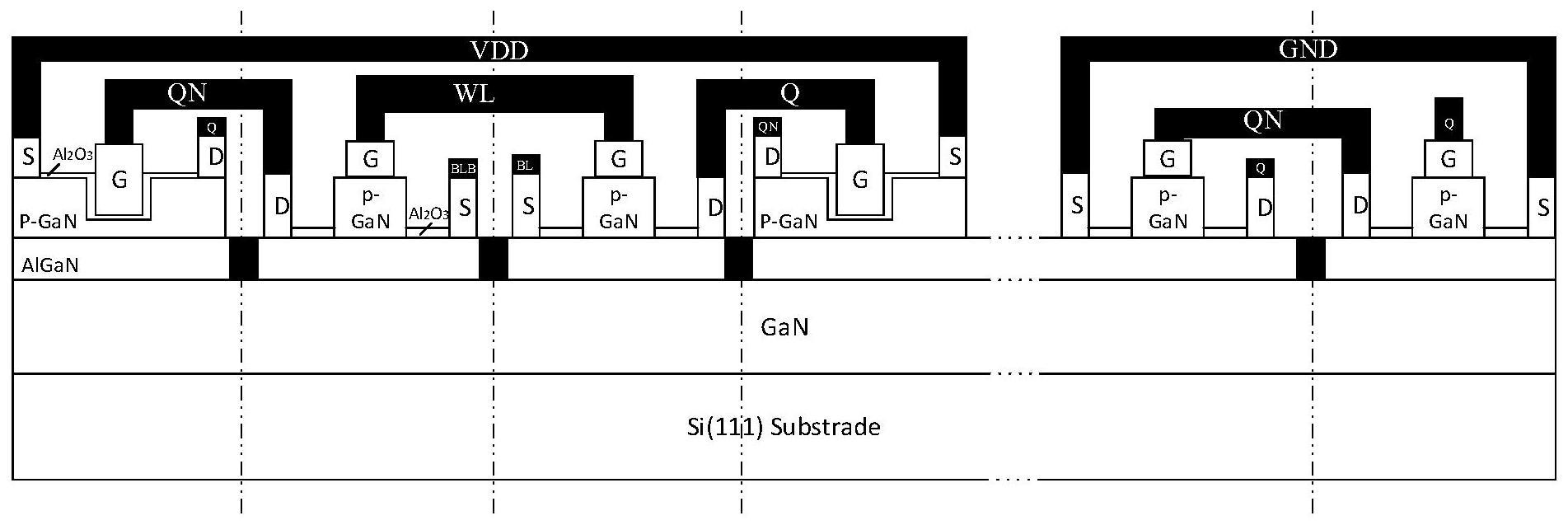

16、在本发明的一个实施例中,所述第一反相器的n沟道晶体管n1、所述第二反相器的n沟道晶体管n2、所述第一控制读写晶体管n3和所述第二控制读写晶体管n4的结构相同,其结构均包括:

17、p-gan帽层、由下至上依次设置的si衬底、gan外延层和algan外延层和al2o3介质层;

18、所述p-gan帽层穿过所述al2o3介质层与所述algan外延层接触;

19、所述algan外延层上设有源极和漏极;所述p-gan帽层上设置有栅极,所述p-gan帽层和所述al2o3介质层均位于所述源极和所述漏极之间。

20、在本发明的一个实施例中,所述第一反相器的p沟道晶体管p1和所述第二反相器的p沟道晶体管p2的结构相同,其结构均包括:

21、由下至上依次设置的si衬底、gan外延层和algan外延层和p-gan层;

22、所述p-gan层开设有凹槽,所述p-gan层上和所述凹槽内覆盖有al2o3介质层;

23、所述p-gan层上设有源极和漏极;所述al2o3介质层均位于所述源极和所述漏极之间;位于所述凹槽内的所述p-gan层上设置有延伸至所述凹槽外的栅极。

24、在本发明的一个实施例中,所述第一反相器的p沟道晶体管p1,源端与电源电压vdd相连,漏端与所述第一控制读写晶体管n3的漏端、所述第一反相器的n沟道晶体管n1的漏端、所述第二反相器的p沟道晶体管p2的栅端和所述第二反相器的n沟道晶体管n2的栅端相连,栅端与所述第一反相器的n沟道晶体管n1的栅端所述第二控制读写晶体管n4的漏端、所述第二反相器的p沟道晶体管p2的漏端和所述第二反相器的n沟道晶体管n2的漏端相连;

25、所述第二反相器的p沟道晶体管p2,源端与电源电压vdd相连,漏端与所述第二反相器的n沟道晶体管n2的漏端、所述第二控制读写晶体管n4的漏端、所述第一反相器的p沟道晶体管p1的栅端和所述第一反相器的n沟道晶体管n1的栅端相连,栅端与所述第二反相器的n沟道晶体管n2的栅端、所述第一控制读写晶体管n3的漏端、所述第一反相器的p沟道晶体管p1的漏端和所述第一反相器的n沟道晶体管n1的漏端相连;

26、所述第一反相器的n沟道晶体管n1,源端接地gnd,漏端与所述第一反相器的p沟道晶体管p1的漏端、所述第一控制读写晶体管n3的漏端、所述第二反相器的p沟道晶体管p2的栅端和所述第二反相器的n沟道晶体管n2的栅端相连,栅端与所述第一反相器的p沟道晶体管p1的栅端、所述第二控制读写晶体管n4的漏端、所述第二反相器的p沟道晶体管p2的漏端和所述第二反相器的n沟道晶体管n2的漏端相连;

27、所述第二反相器的n沟道晶体管n2,源端接地gnd,漏端与所述第二反相器的p沟道晶体管p2的漏端、所述第二控制读写晶体管n4的漏端、所述第一反相器的p沟道晶体管p1的栅端和所述第一反相器的n沟道晶体管n1的栅端相连,栅端与所述第二反相器的p沟道晶体管p2的栅端、所述第一控制读写晶体管n3的漏端、所述第一反相器的p沟道晶体管p1的漏端和所述第一反相器的n沟道晶体管n1的漏端相连;

28、所述第一控制读写晶体管n3,源端接位线,漏端与所述第一反相器的p沟道晶体管p1的漏端、所述第一反相器的n沟道晶体管n1的漏端、所述第二反相器的p沟道晶体管p2的栅端和所述第二反相器的n沟道晶体管n2的栅端相连,栅端与字线相连;

29、所述第二控制读写晶体管n4,源端接位线非,漏端与所述第二反相器的p沟道晶体管p2的漏端、所述第二反相器的n沟道晶体管n2的漏端、所述第一反相器的p沟道晶体管p1的栅端和所述第一反相器的n沟道晶体管n1的栅端相连,栅端与字线相连。

30、本发明的有益效果:

31、本发明采用gan基器件,具有禁带宽度大、临界击穿电场高、饱和速度大、导热性好、耐高温以及耐腐蚀等优良的电学性能而被认为其适合应用在高频、大功率、强辐射等场合。此外与gan基器件相关的电路中如果采用gan制备的存储器来代替硅材料制备的形同电路,则大大降低不同材料之间互联带来的寄生等问题,提高工作效率。本发明采用的n、p沟道器件均为增强型器件,常关的特性使得电路的静态功耗很低。采用gan基cmos结构,既可以利用材料及器件结构本身的性质就可以解决si基sram电路存在的问题,也可以实现全gan集成的电路结构,以规避采用si基sram应用于gan电路中的电路设计及工艺的复杂度增加的问题。

32、以下将结合附图及实施例对本发明做进一步详细说明。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181730.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。