低功耗的多次可编程非易失性存储单元及其存储器的制作方法

- 国知局

- 2024-07-31 19:13:26

本发明总体涉及非易失性存储器,更具体地,涉及具有深n阱的电可编程可擦除的非易失性存储单元,可将存储单元与衬底隔离开。

背景技术:

1、非易失性存储器的存入数据在断电后也不会消失,并且可以长时间保持数据。基于此优点,这类存储器在电子设备中得到广泛应用。尤其是多次电可擦除可编程的非易失性存储器,可以多次进行数据的写入、擦除等,应用很广。这类非易失性存储器,多是单层多晶硅浮栅类型,主要通过沟道热电子注入来实现编程和擦除。编程时沟道热电子跃迁至浮栅,沟道内电流较大,导致功耗较高。

2、目前,行业内十分需求低功耗存储器。因此,需要对此类存储器进行优化,实现低功耗目的。

技术实现思路

1、本发明提供一种低功耗的多次电可擦除可编程的非易失性存储单元及其存储器。

2、本发明的存储单元及其存储器,通过在隧穿电容的栅氧化物层处,发生富勒-诺德海姆(f-n)隧穿,进行编程和擦除操作。与通过沟道热电子注入浮栅进行编程的现有存储单元相比,产生的电流很小(na级),以此实现低功耗。

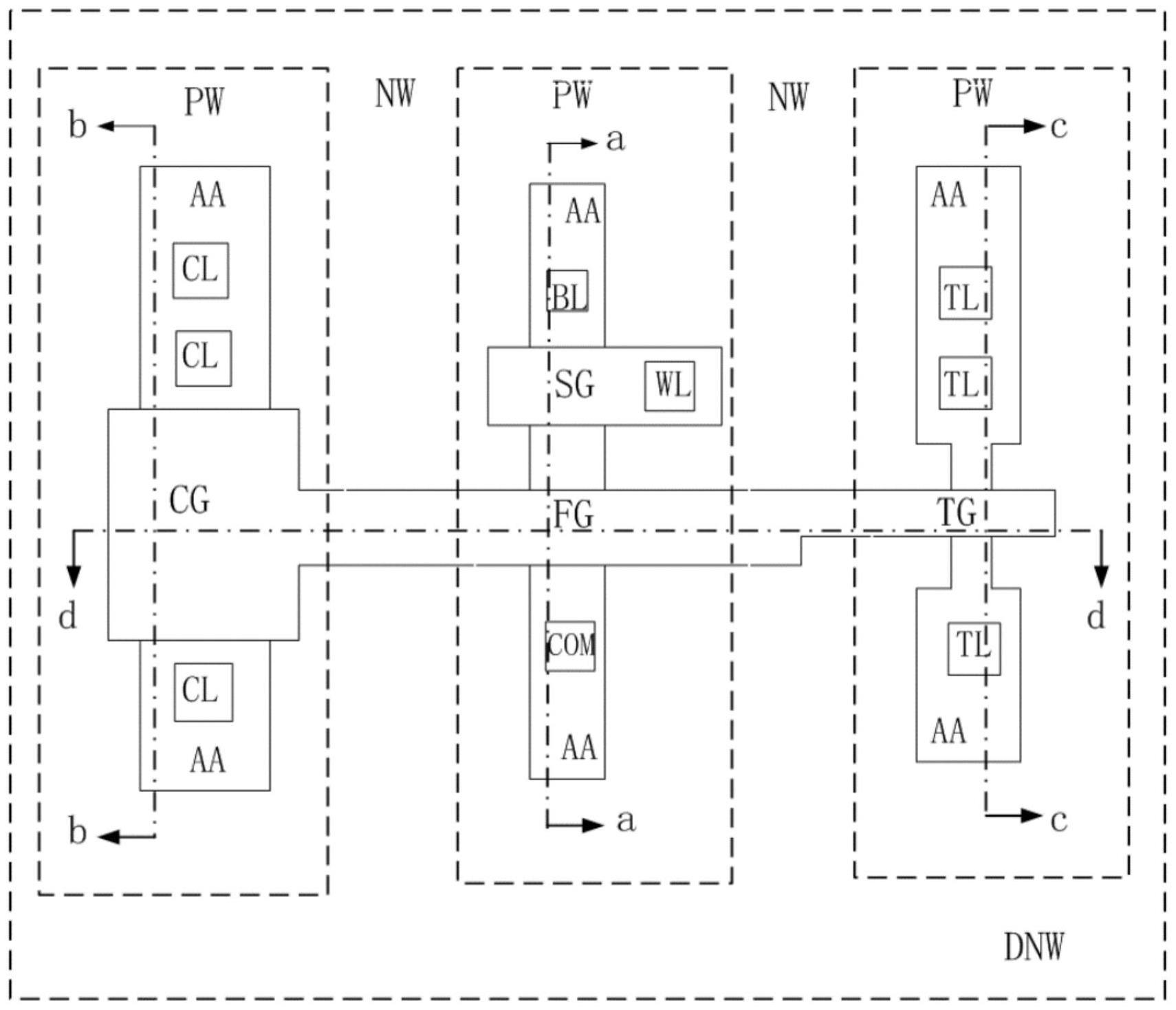

3、本发明的第一方面涉及一个多次可编程非易失性存储单元,包含:一个深n阱;第一p阱、第二p阱、和第三p阱/或第一n阱,这些阱相互平行地位于所述深n阱中;控制电容和隧穿电容分别位于第一和第二p阱中,各自包含一个或两个位于所在p阱中的n型耦合区;一个浮栅晶体管位于第三p阱/或第一n阱中,该浮栅晶体管包含多晶硅浮栅及其下方的栅氧化物;所述浮栅晶体管的浮栅及其栅氧化物,沿垂直于上述p阱的平行方向,延伸至覆盖第一和第二p阱中的控制电容和隧穿电容,分别形成控制电容和隧穿电容的上极板和栅氧化物。

4、在一个优选的实施方式中,所述控制电容内栅氧化物层面积比隧穿电容内栅氧化物层的面积大,两者面积之比为1.1:1.0 – 50 : 1.0。

5、在另一个优选的实施方式中,所述的控制电容和隧穿电容各自都是一个晶体管,各自包含两个位于所在p阱中的n型耦合区,分列于各自上极板的两侧。

6、在再一个优选的实施方式中,所述的浮栅晶体管是nmos晶体管,位于第三p阱中。优选所述第三p阱位于第一p阱和第二p阱之间、或第一和第二p阱的一侧,所述三个p阱中相邻的两个之间分别被另外的n阱分隔开,所述另外的n阱不是第一n阱。

7、在再一个优选的实施方式中,所述的浮栅晶体管是pmos晶体管,位于第一n阱中,第一n阱位于第一p阱与第二p阱之间,或第一和第二p阱的一侧;在第一n阱位于第一和第二p阱的一侧时,所述第一和第二p阱之间被另外的n阱分隔开,所述另外的n阱不是第一n阱。

8、在再一个优选的实施方式中,所述的存储单元还包含一个选择晶体管,位于浮栅晶体管所在的阱中,并与浮栅晶体管串联,所述选择晶体管包含选择栅及其下方的栅氧化物、以及源极和漏极,浮栅晶体管也包含源极和漏极,所述选择晶体管的源极与浮栅晶体管的漏极是一个共用极。

9、本发明的第二方面涉及一个多次可编程非易失性存储器装置,构建在一个p型衬底上,该存储器装置,包含:至少一个本发明上述的非易失性存储单元;其中所有存储单元的深n阱合并成一体,位于所述p型衬底中;所有存储单元以相同的朝向和排布方式,排列成多行和多列,列的方向与存储单元内p阱的平行方向一致;每列中存储单元的第一p阱、第二p阱、第三p阱/或第一n阱、以及夹在相邻两个p阱之间的另外的n阱,均沿列的方向分别合并成一体。

10、在一个优选的实施方式中,所述存储器装置还包含:位线、公共线、控制线、和隧穿线;其中:公共线连接至一行存储单元中每个浮栅晶体管的源极;控制线连接至一行存储单元中每个控制电容的一个或两个n型耦合区域;和隧穿线连接至一列存储单元中每个隧穿电容的一个或两个n型耦合区域;在装置中没有选择晶体管的情形下,位线连接至一列存储单元中每个浮栅晶体管的漏极;在装置中有选择晶体管的情形下,位线连接至一列存储单元中每个选择晶体管的漏极,该情形下还有字线,连接至一行存储单元中每个选择晶体管的栅极。

11、更优选地,所述的控制线连接至一行存储单元中每个控制电容的两个n型耦合区域、及其所在的第一p阱,所述的隧穿线连接至一列存储单元中每个隧穿电容的两个n型耦合区域、及其所在的第二p阱。

12、本发明的第三方面涉及一个多次可编程非易失性存储单元组,它包含:两个本发明上述的存储单元,即:第一存储单元和第二存储单元;在所述两个单元中,浮栅晶体管所在的第三p阱/或第一n阱,位于第一p阱与第二p阱之间;其中两个单元中的两个浮栅晶体管共用一个源极;第一存储单元中的控制电容和隧穿电容,分别与第二存储单元中的隧穿电容和控制电容,共用一个n型耦合区;其中两个单元的深n阱合并成一体;第一存储单元中的第一p阱和第二p阱,分别与第二存储单元中的第二p阱和第一p阱合并成一体;两个单元中的第三p阱/或第一n阱合并成一体、以及夹在相邻两个p阱之间的另外的n阱也合并呈一体。

13、在一个优选的实施方式中,所述存储单元组中的两个存储单元均在其隧穿电容的栅氧化物处,通过富勒-诺德海姆隧穿,进行编程和擦除操作。更优选地,所述第一存储单元中的控制电容内栅氧化物层面积和隧穿电容内栅氧化物层的面积之比,与第二存储单元中的相同,均为1.1:1.0 – 50 : 1.0。

14、在另一个优选的实施方式中,所述的第一存储单元与第二存储单元的结构和组成完全相同。

15、本发明的第四方面涉及一个多次可编程非易失性存储器装置,构建在一个p型衬底上,该存储器装置包含:至少一个本发明上述的存储单元组;其中所有存储单元组的深n阱合并成一体,位于所述p型衬底中;所有存储单元组以相同的朝向和排布方式,排列成多行和多列,列的方向与存储单元内p阱的平行方向一致,每列中存储单元组的所述p阱和n阱,沿列的方向,分别相应合并成一体。

16、在一个优选的实施方式中,所述非易失性存储器装置还包含:位线、公共线、控制线、和隧穿线;其中:公共线连接至一行中每个存储单元组中的两个浮栅晶体管的共用源极,控制线连接至一行中每个存储单元组中的第一存储单元的控制电容的一个或两个n型耦合区域、和第二存储单元的隧穿电容的一个或两个n型耦合区域;隧穿线连接至一列中每个存储单元组中的第一存储单元的隧穿电容的一个或两个n型耦合区域、和第二存储单元的控制电容的一个或两个n型耦合区域;在装置中没有选择晶体管的情形下,位线连接至一列中每个存储单元组中的两个浮栅晶体管的漏极;在装置中有选择晶体管的情形下,位线连接至一列中每个存储单元组中的两个选择晶体管的漏极,该情形下还有字线,连接至一行中每个存储单元组中的两个选择晶体管的栅极。

17、更优选地,所述非易失性存储器装置中的控制线连接至一行中每个存储单元组中的第一存储单元的控制电容的两个n型耦合区域及其所在的p阱、和第二存储单元的隧穿电容的两个n型耦合区域及其所在的p阱;所述的隧穿线连接至一列中每个存储单元组中的第一存储单元的隧穿电容的两个n型耦合区域及其所在的p阱、和第二存储单元的控制电容的一个或两个n型耦合区域。

18、本发明的存储单元的编程,在隧穿电容的栅氧化物层处,通过富勒-诺德海姆(f-n)隧穿进行。与现有技术中的通过沟道热电子注入浮栅进行编程的多次可编程存储单元相比,本发明通过富勒-诺德海姆隧穿进行编程,产生的电流很小(na级),可以大幅度降低功耗。同时,本发明的擦除也通过富勒-诺德海姆隧穿进行,擦除效率高。

19、另外,本发明的包含两个存储单元的存储单元组,可以实现在同一的操作条件下,使一个存储单元进行编程,同时使另一个存储单元进行擦除。这样在读操作中,组内一个存储单元可以作为另一个单元的参考单元进行比较读出,使读出的可靠性大大提高。这是因为存储单元读出时需要与参考存储单元比较而读出,参考存储单元的电流值一般取值为存储单元编程电流值的50%;而本发明的存储单元组内,作为参考单元的存储单元的电流值是其自身的值;组内一个存储单元为编程状态时,作为参考单元的另一个存储单元为擦除状态;一个存储单元为擦除状态时,作为参考单元的另一个存储单元为编程状态;

20、本发明的包含两个存储单元的存储单元组,存储1 bit数据。与单一存储单元存储1bit数据相比,它虽然面积稍大点,但是操作简便,效率和读出可靠性得以大幅度提高。

21、

本文地址:https://www.jishuxx.com/zhuanli/20240731/181921.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表