一种供选择的容错量子逻辑电路的构造方法、电子设备和存储介质

- 国知局

- 2024-07-31 19:13:45

本发明涉及量子逻辑电路领域,尤其涉及一种供选择的容错量子逻辑电路的构造方法、电子设备和存储介质。

背景技术:

1、量子逻辑电路,也称量子线路,是最常用的通用量子计算模型,表示在抽象概念下,对于量子比特进行操作的线路,其组成包括了量子比特、线路(时间线)以及各种量子逻辑门。最后常需要量子测量将结果读取出来。其从本质上是一个量子逻辑门的执行序列,它是从左至右依次执行的。量子逻辑门的合集被称为通用量子门库,而通用逻辑门库的构成不是唯一的,例如:有{cnot,单量子位u}门库、{toffoli,h,p}门库,{cnot,h,t}门库。

2、量子纠错码是克服量子态退相干,从而实现量子计算的有效方案,其能够通过编码、检错及纠错步骤纠正出错的量子态,从而保证存储和传输中量子信息的正确性。面对量子逻辑电路中复杂的量子逻辑门操作,其中一旦存在错误,其会迅速地增殖与传播,而量子纠错码的纠错能力始终是一定的,增加的错误无法被纠错,这样便会获取不到理想的计算结果。因此,在量子逻辑电路的构造过程中,需要通过容错计算规范量子态制备、测量、逻辑门操作等过程,使得错误限制在一定的阈值内,保证计算的精确性和可持续性。

3、现有技术中分别提供了以steane-[[7,1,3]]纠错码(下称7码)和以reed-muller-[[15,1,3]]纠错码(下称15码)的两种方式所支持的{cnot,h,t}门库,分别为7码门库和15码门库。其中,7码门库的纠错能力强,但是其实现时间较长(尤其是对于t门的实现);而15码门库相较于7码门库的纠错能力不弱,但是其实现时间较短(尤其是对于t门的实现)。当用户需要构造量子逻辑电路,可以根据实际需求进行选择对应的通用量子门库。然而由于选择较少,使得构造出来的量子逻辑电路仅能单方面突出表现其中一方面的性能。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种供选择的容错量子逻辑电路的构造方法、电子设备和存储介质。

2、本发明的目的是通过以下技术方案来实现的:

3、本发明的第一方面,提供一种供选择的容错量子逻辑电路的构造方法,包括以下步骤:

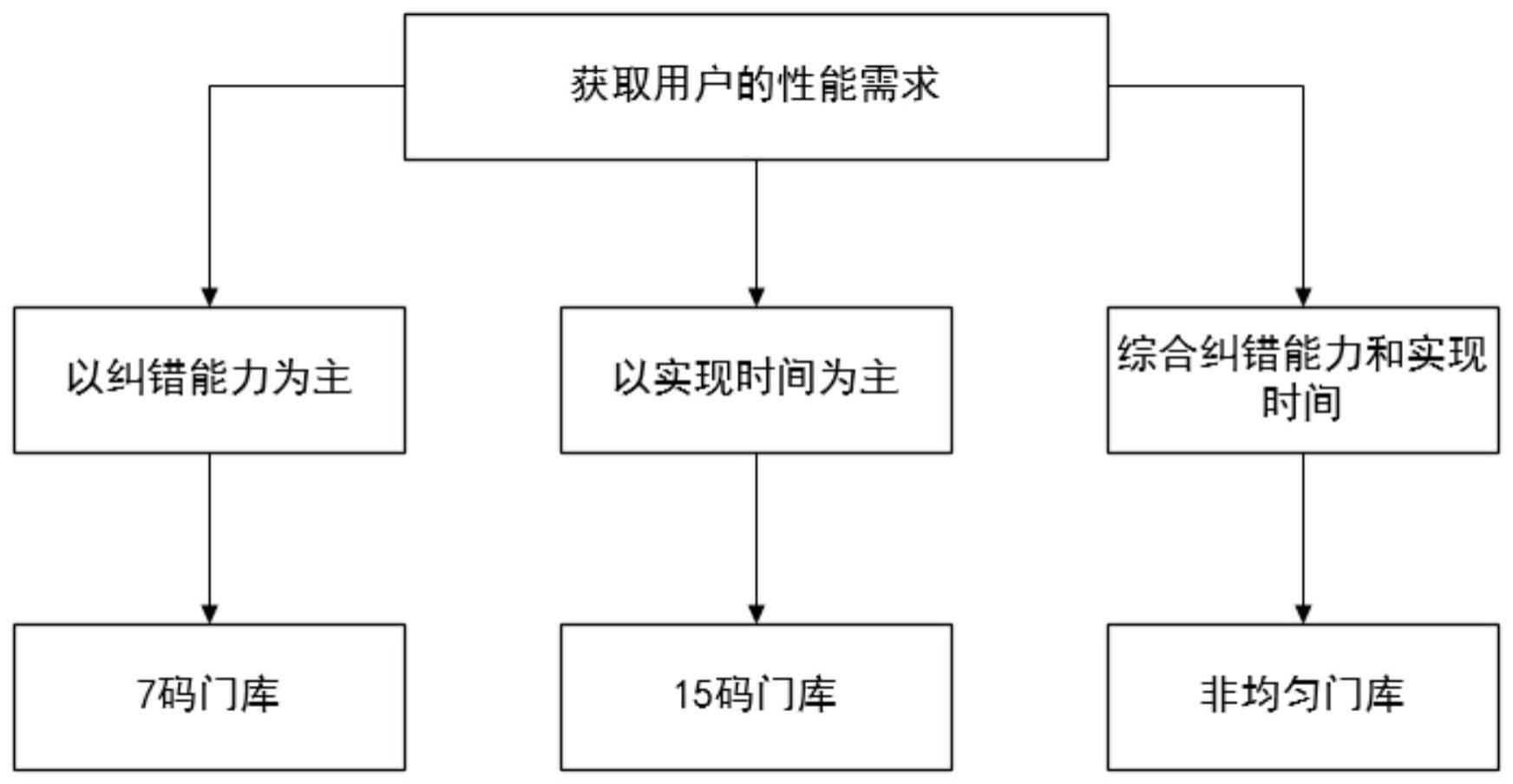

4、获取用户的量子逻辑电路构造需求,所述量子逻辑电路构造需求包括以纠错能力为主、以实现时间为主、综合纠错能力和实现时间在内的性能需求;

5、根据性能需求,提供对应类型的通用量子门库,每个通用量子门库均包括h门、cnot门和t门;其中:以纠错能力为主的通用量子门库为7码门库,以实现时间为主的通用量子门库为15码门库,综合纠错能力和实现时间的通用量子门库为非均匀门库;7码为steane-[[7,1,3]]纠错码,15码为reed-muller-[[15,1,3]]纠错码;

6、所述非均匀门库为包含33个物理量子比特的量子门库,其中第1~15个量子比特为第0号位、第16~19个量子比特分别为第1~4号位、第20~26个量子比特为第5号位、第27~第33个量子比特为第6号位;

7、非均匀门库的h门的第0号位采用15码的第一逻辑h门,h门的第1~4号位为物理h门,h门的第5号位和第6号位均采用7码的第二逻辑h门;

8、非均匀门库的cnot门包括以第5号位或第6号位为控制位、以第0号位为目标位的第一cnot门,以第0号位为控制位、以第5号位或第6号位为目标位的第二cnot门,以第5号位为控制位、以第6号位为目标位的第三cnot门,以第6号位为控制位、以第5号位为目标位的第四cnot门,其中第三cnot门和第四cnot门为7码的cnot门;

9、非均匀门库的t门包括顺次设置的:第四cnot门,以第5号位为控制位、以第0号位为目标位的第一cnot门,15码的逻辑t门,以第5号位为控制位、以第0号位为目标位的第一cnot门,第四cnot门。

10、进一步地,所述第一cnot门和第二cnot门为分段容错结构,即在每个逻辑电路被分为至少两个子段,在每个子段后方连接有一个纠错模块。

11、进一步地,第一cnot门的22个量子比特,分别对应于q0~q21,其中前7个量子比特对应第5号位或第6号位,后15个量子比特对应于第0号位;

12、整个第一cnot门被分为两段,第一cnot门的第一段顺次包括:q0为控制位、q7为目标位的第一子cnot门,q1为控制位、q8为目标位的第二子cnot门,q2为控制位、q9为目标位的第三子cnot门,q3为控制位、q10为目标位的第四子cnot门,q4为控制位、q11为目标位的第五子cnot门,q5为控制位、q12为目标位的第六子cnot门,q6为控制位、q13为目标位的第七子cnot门,q0为控制位、q14为目标位的第八子cnot门,q1为控制位、q14为目标位的第九子cnot门;

13、第一cnot门的第二段顺次包括:q2为控制位、q14为目标位的第十子cnot门,q0为控制位、q15为目标位的第十一子cnot门,q1为控制位、q16为目标位的第十二子cnot门,q2为控制位、q17为目标位的第十三子cnot门,q3为控制位、q18为目标位的第十四子cnot门,q4为控制位、q19为目标位的第十五子cnot门,q5为控制位、q20为目标位的第十六子cnot门,q6为控制位、q21为目标位的第十七子cnot门;

14、第一cnot门的第一段后连接有第一纠错模块ε1,第一cnot门的第二段后连接有第二纠错模块ε2。

15、进一步地,所述第一纠错模块ε1具体实现方式为:

16、依照分段容错纠错策略,第一纠错模块ε1为常数型稳定子的投影测量过程,在此过程中对常数稳定子进行测量以得到可扩散性错误的相关信息;具体而言,在第一纠错模块ε1中,利用shor所设计的容错校验信息提取策略,针对控制逻辑量子位即控制位,依次测量稳定子:z_{0}z_{2}z_{4}z_{6}、z_{1}z_{2}z_{5}z_{6}、z_{3}z_{4}z_{5}z_{6};

17、针对目标逻辑量子位即目标位,依次测量稳定子:x_{14}x_{15}x_{16}x_{17}x_{18}x_{19}x_{20}x_{21}、x_{10}x_{11}x_{12}x_{13}x_{18}x_{19}x_{20}x_{21}、x_{8}x_{9}x_{12}x_{13}x_{16}x_{17}x_{20}x_{21}、x_{7}x_{9}x_{11}x_{13}x_{15}x_{17}x_{19}x_{21};

18、所述第二纠错模块ε2具体为:

19、依照分段容错策略,第二纠错模块ε2为在末尾的纠错过程,需要对控制逻辑量子位于目标逻辑量子位分别进行一轮完整的稳定子测量,提取校验信息,并与第一纠错模块ε1中获取的信息一并送入解码器进行解码并纠错;具体而言,在第二纠错模块ε2中,利用steane所设计的容错校验信息提取策略,针对控制逻辑量子位即控制位,依次测量稳定子:z_{0}z_{2}z_{4}z_{6}、z_{1}z_{2}z_{5}z_{6}、z_{3}z_{4}z_{5}z_{6}、x_{0}x_{2}x_{4}x_{6}、x_{1}x_{2}x_{5}x_{6}、x_{3}x_{4}x_{5}x_{6};

20、针对目标逻辑量子位即目标位,依次测量稳定子x_{14}x_{15}x_{16}x_{17}x_{18}x_{19}x_{20}x_{21}、x_{10}x_{11}x_{12}x_{13}x_{18}x_{19}x_{20}x_{21}、x_{8}x_{9}x_{12}x_{13}x_{16}x_{17}x_{20}x_{21}、x_{7}x_{9}x_{11}x_{13}x_{15}x_{17}x_{19}x_{21}、z_{14}z_{15}z_{16}z_{17}z_{18}z_{19}z_{20}z_{21}、z_{10}z_{11}z_{12}z_{13}z_{18}z_{19}z_{20}z_{21}、z_{8}z_{9}z_{12}z_{13}z_{16}z_{17}z_{20}z_{21}、z_{7}z_{9}z_{11}z_{13}z_{15}z_{17}z_{19}z_{21}、z_{18}z_{19}z_{20}z_{21}、z_{16}z_{17}z_{20}z_{21}、z_{15}z_{17}z_{19}z_{21}、z_{12}z_{13}z_{20}z_{21}、z_{11}z_{13}z_{19}z_{21}、z_{9}z_{13}z_{17}z_{21};

21、其中数字0~21分别代表q0~q21。

22、进一步地,第二cnot门的22个量子比特,分别对应于q22~q43,其中前15个量子比特对应于第0号位,后7个量子比特对应第5号位或第6号位;

23、整个第二cnot门被分为两段,第二cnot门的第一段顺次包括:q22为控制位、q37为目标位的第十八子cnot门,q23为控制位、q38为目标位的第十九子cnot门,q24为控制位、q39为目标位的第二十子cnot门,q25为控制位、q40为目标位的第二十一子cnot门,q26为控制位、q41为目标位的第二十二子cnot门,q27为控制位、q42为目标位的第二十三子cnot门,q28为控制位、q43为目标位的第二十四子cnot门,q29为控制位、q37为目标位的第二十五子cnot门,q29为控制位、q38为目标位的第二十六子cnot门;

24、第二cnot门的第二段顺次包括:q29为控制位、q39为目标位的第二十七子cnot门,q30为控制位、q37为目标位的第二十八子cnot门,q31为控制位、q38为目标位的第二十九子cnot门,q32为控制位、q39为目标位的第三十子cnot门,q33为控制位、q40为目标位的第三十一子cnot门,q34为控制位、q41为目标位的第三十二子cnot门,q35为控制位、q42为目标位的第三十三子cnot门,q36为控制位、q43为目标位的第三十四子cnot门;

25、第二cnot门的第一段后连接有第三纠错模块ε3,第二cnot门的第二段后连接有第四纠错模块ε4。

26、进一步地,所述第三纠错模块ε3具体为:

27、依照分段容错纠错策略,第三纠错模块ε3为常数型稳定子的投影测量过程,在此过程中对常数稳定子进行测量以得到可扩散性错误的相关信息;具体而言,在第三纠错模块ε3中,利用shor所设计的容错校验信息提取策略,针对控制逻辑量子位即控制位,依次测量z_{29}z_{30}z_{31}z_{32}z_{33}z_{34}z_{35}z_{36}、z_{25}z_{26}z_{27}z_{28}z_{33}z_{34}z_{35}z_{36}、z_{23}z_{24}z_{27}z_{28}z_{31}z_{32}z_{35}z_{36}、z_{22}z_{24}z_{26}z_{28}z_{30}z_{32}z_{34}z_{36}、z_{33}z_{34}z_{35}z_{36}、z_{31}z_{32}z_{35}z_{36}、z_{30}z_{32}z_{34}z_{36}、z_{27}z_{28}z_{35}z_{36}、z_{26}z_{28}z_{34}z_{36}、z_{24}z_{28}z_{32}z_{36};

28、针对目标逻辑量子位即目标位,依次测量稳定子x_{37}x_{39}x_{41}x_{43}、x_{38}x_{39}x_{42}x_{43}、x_{40}x_{41}x_{42}x_{43};

29、所述第四纠错模块ε4具体为:

30、依照分段容错策略,第四纠错模块ε4为在末尾的纠错过程,需要对控制逻辑量子位于目标逻辑量子位分别进行一轮完整的稳定子测量,提取校验信息,并与第三纠错模块ε3中获取的信息一并送入解码器进行解码并纠错,具体而言,在该模块中,利用steane所设计的容错校验信息提取策略,针对控制逻辑量子位即控制位,依次测量稳定子x_{29}x_{30}x_{31}x_{32}x_{33}x_{34}x_{35}x_{36}、x_{25}x_{26}x_{27}x_{28}x_{33}x_{34}x_{35}x_{36}、x_{23}x_{24}x_{27}x_{28}x_{31}x_{32}x_{35}x_{36}、x_{22}x_{24}x_{26}x_{28}x_{30}x_{32}x_{34}x_{36}、z_{29}z_{30}z_{31}z_{32}z_{33}z_{34}z_{35}z_{36}、z_{25}z_{26}z_{27}z_{28}z_{33}z_{34}z_{35}z_{36}、z_{23}z_{24}z_{27}z_{28}z_{31}z_{32}z_{35}z_{36}、z_{22}z_{24}z_{26}z_{28}z_{30}z_{32}z_{34}z_{36}、z_{33}z_{34}z_{35}z_{36}、z_{31}z_{32}z_{35}z_{36}、z_{30}z_{32}z_{34}z_{36}、z_{27}z_{28}z_{35}z_{36}、z_{26}z_{28}z_{34}z_{36}、z_{24}z_{28}z_{32}z_{36};

31、针对目标逻辑量子位即目标位,依次测量稳定子z_{37}z_{39}z_{41}z_{43}、z_{38}z_{39}z_{42}z_{43},z_{40}z_{41}z_{42}z_{43},x_{37}x_{39}x_{41}x_{43},x_{38}x_{39}x_{42}x_{43},x_{40}x_{41}x_{42}x_{43};

32、其中数字22~43分别代表q22~q43。

33、进一步地,所述量子逻辑电路构造需求还包括使用t门和不使用t门在内的使用需求;

34、所述根据性能需求,提供对应类型的通用量子门库,包括:

35、首先对量子逻辑电路构造需求的使用需求进行判断,若使用需求为使用t门,则进一步进行性能需求的判断,并直接根据性能需求的选择作提供对应类型的通用量子门库。

36、进一步地,若使用需求为不使用t门,则直接提供7码门库。

37、本发明的第二方面,提供一种电子设备,包括存储单元和处理单元,所述存储单元上存储有可在所述处理单元上运行的计算机指令,所述处理单元运行所述计算机指令时执行所述的一种供选择的容错量子逻辑电路的构造方法的步骤。

38、本发明的第三方面,提供一种存储介质,其上存储有计算机指令,所述计算机指令运行时执行所述的一种供选择的容错量子逻辑电路的构造方法的步骤。

39、本发明的有益效果是:

40、在本发明的一示例性实施例中,当用户需要构造量子逻辑电路时,首先获取用户的量子逻辑电路构造需求,并根据性能需求,提供对应类型的通用量子门库;同时,在现有的7码门库和15码门库的基础上,提供可以了一种可以综合纠错能力和实现时间的新的通用量子门库即非均匀门库,从而可以满足用户不同的纠错能力和实现时间的需求。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181943.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表